1

Изобретение относится к вычислительной технике и может быть использовано для вывода информации на экран электроннолучевой трубки.. ,Известно устройство для вывода информации, содержащее блок памяти, подключенный к блоку управления, соединенному с кольцевым регистром, подключенным через дешифратор к блоку «л памяти i .

Недостатком известного устройства является невысокое быстродействие.

Наиболее близким по технической сущности к изобретению является устройство, содержащее первые элементы И первые входы которых подключены к информационным входам устройства, а вторые входы - к его первому управляющему входу, выходы первых элемен- 20 тов И соедипэчы с первыми входами первого регистра, выходы которого подключены к первым входам блока памяти, вторые входы которого соединены с выходами деи ифратора, подключенного ко 25 второму регистру, соединенному с первыми выходами блока управления, второй выход которого подк.шочен к блоку памяти, выходы которого соединены с первыми входами вторых элементов И JQ

первый вход блока управления подключен ко второму управляющему входу устройства 2 .

Недостатком данного устройства является невысокая надежность.

Цель изобретения - повышение надежности устройства.

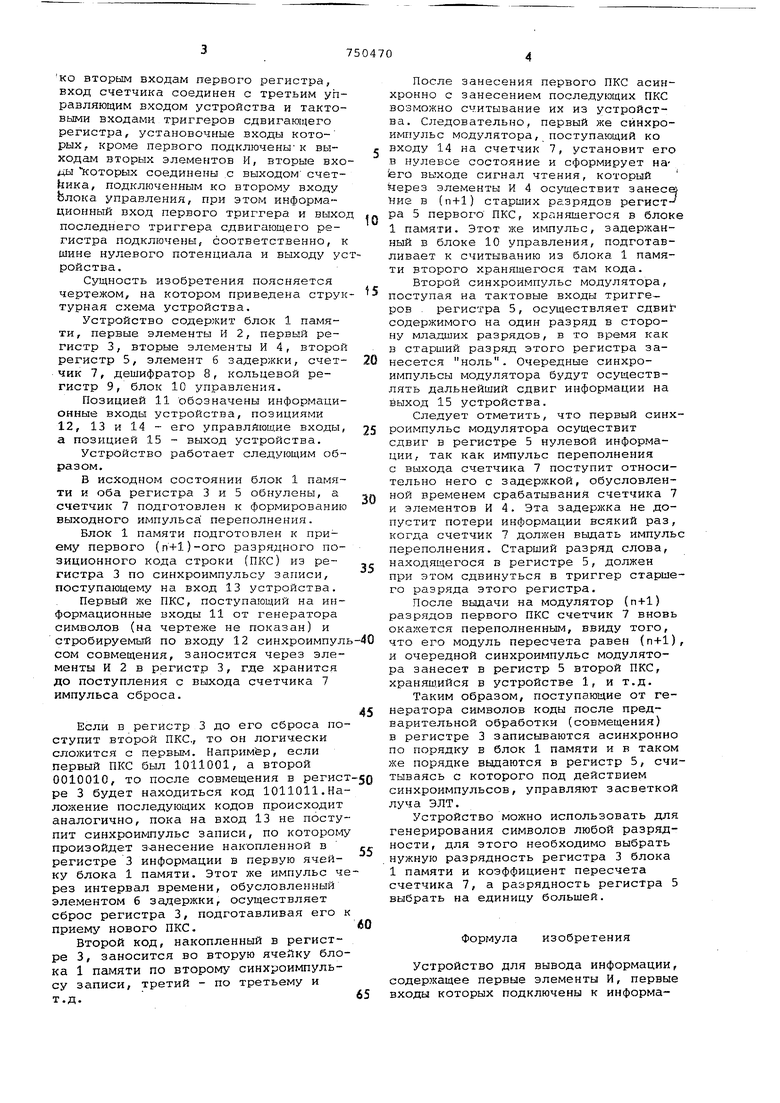

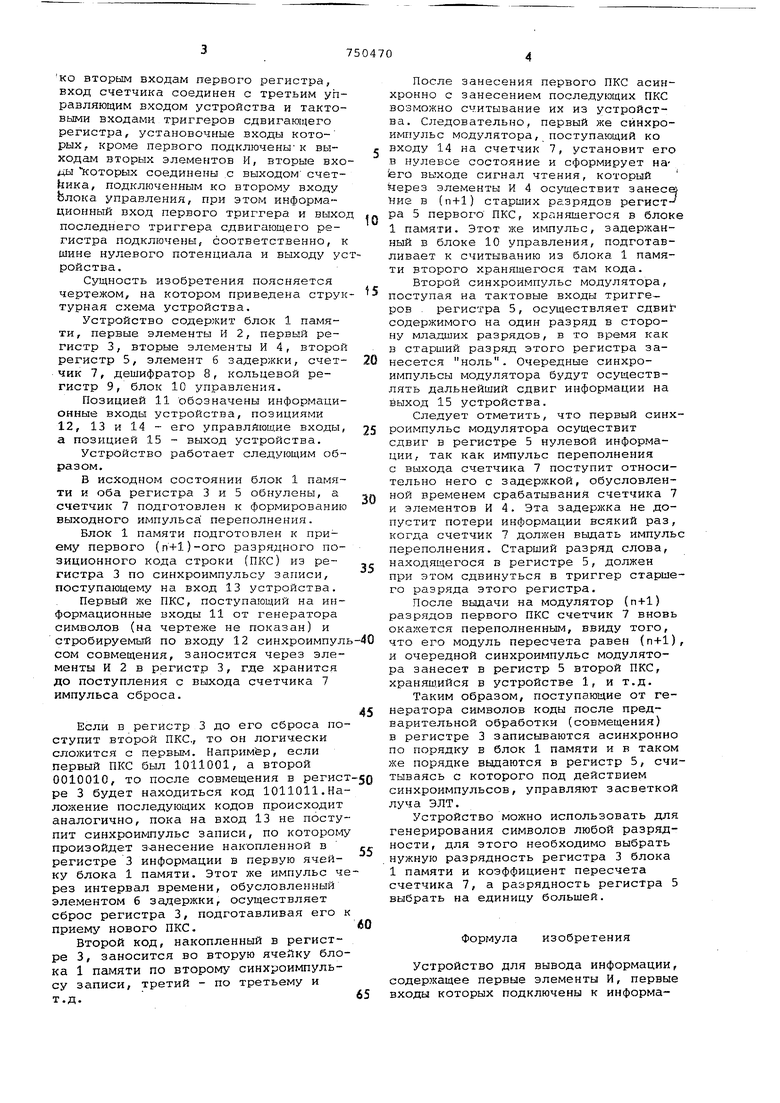

Это достигается тем, что в устройство, содержащее первые элементы И, первые входы которых подключены к информационным входам устройства, а вторые входы - к его первому управлякядему входу, выходы первых элементов И соединены с первыми входами первого регистра, выходы которого подключены к первым входам блока памяти, вторые входы которого соединены с выходами дешифратора, подключенного ко второму регистру, соединенному с первыми выходами блока управления, второй выход которого подключен к блоку памяти, выходы которого соединены с первыми входами вторых элементов И, первый вход блока управления подключен ко второму управляющему входу устройства, введены счетчик, сдвигающий регистр и элемент задержки, вход которого подключен ко второму управляющему входу устройства, а выход ко вторым входам первого регистра, вход счетчика соединен с третьим уп равляющим входом устройства и такто выми входами триггеров сдвигающего регистра, установочные входы которык, кроме первого подключенык выходам вторых элементов И, вторые вх №1 Которых соединены .с выходом счет Ьика, подключенным ко второму входу Ьлока управления, при этом информационный вход первого триггера и выхо последнего триггера сдвигающего регистра подключены, соответственно, шине нулевого потенциала и выходу у ройства. Сущность изобретения поясняется чертежом, на котором приведена стру турная схема устройства. Устройство содержит блок 1 памяти, первые элементы И 2, первый регистр 3, вторые элементы И 4, второ регистр 5, элемент б задержки, счет чик 7, дешифратор 8, кольцевой регистр 9, блок 10 управления. Позицией 11 обозначены информаци онные входы устройства, позициями 12, 13 и 14 - его управляющие входы а позицией 15 - выход устройства. Устройство работает следующим об разом, В исходном состоянии блок 1 памяти и оба регистра 3 и 5 обнулены, а счетчик 7 подготовлен к формированию выходного импульса: переполнения. Блок 1 памяти подготовлен к приему первого (п+1)-ого разрядного позиционного кода строки (ПКС) из регистра 3 по синхроимпульсу записи, поступающему на вход 13 устройства. Первый же ПКС, поступающий на информационные входы 11 от генератора символов (на чертеже не показан) и стробируемый по входу 12 синхроимпул сом совмещения, заносится через элементы И 2 в регистр 3, где хранится до поступления с выхода счетчика 7 импульса сброса. Если в регистр 3 до его сброса по ступит второй ПКС., то он логически сложится с первым. Например, если первый ПКС был 1011001, а второй 0010010, то после совмещения в регис ре 3 будет находиться код 1011011.На ложение последующих кодов происходит аналогично, пока на вход 13 не посту пит синхроимпульс записи, по котором пpoизoй дeт занесение накопленной в регистре 3 информации в первую ячейку блока 1 памяти. Этот же импульс ч рез интервал времени, обусловленный элементом 6 задержки, осуществляет сброс регистра 3, подготавливая его приему нового ПКС, Второй код, накопленный в регистре 3, заносится во вторую ячейку бло ка 1 памяти по второму синхроимпульсу записи, третий - по третьему и После занесения первого ПКС асинхронно с занесением последующих ПКС возможно считывание их из устройства. Следовательно, первый же синхроимпульс модулятора, поступающий ко входу 14 на счетчик 7, установит его в нулевое состояние и сформирует наего выходе сигнал чтения, который аерез элементы И 4 осуществит занес® ние в (п + 1) старших разрядов регистра 5 первого ПКС, хранящегося в блоке 1 памяти. Этот же импульс, задержанный в блоке 10 управления, подготавливает к считыванию из блока 1 памяти второго хранящегося там кода. Второй синхроимпульс модулятора, поступая на тактовые входы триггеров . регистра 5, осуществляет сдвиг содержимого на один разряд в сторону младших разрядов, в то время как в старший разряд этого регистра занесется ноль. Очередные синхроимпульсы модулятора будут осуществлять дальнейший сдвиг информации на выход 15 устройства. Следует отметить, что первый синхроимпульс модулятора осуществит сдвиг в регистре 5 нулевой информации, так как импульс переполнения с выхода счетчика 7 поступит относительно него с задержкой, обусловленной временем срабатывания счетчика 7 и элементов И 4. Эта задержка не допустит потери информации всякий раз, когда счетчик 7 должен выдать импульс переполнения. Старший разряд слова, находящегося в регистре 5, должен при этом сдвинуться в триггер старшего разряда этого регистра. После выдачи на модулятор (п+1) разрядов первого ПКС счетчик 7 вновь окажется переполненным, ввиду того, что его модуль пересчета равен (п+1), и очередной синхроимпульс модулятора занесет в регистр 5 второй ПКС, храняш.ийся в устройстве 1, и т.д. Таким образом, поступающие от генератора символов коды после предварительной обработки (совмещения) в регистре 3 записываются асинхронно по порядку в блок 1 памяти и в таком же порядке выдаются в регистр 5, считываясь с которого под действием синхроимпульсов, управляют засветкой луча ЭЛТ, Устройство можно использовать для генерирования символов любой разрядности, для этого необходимо выбрать нужную разрядность регистра 3 блока 1 памяти и коэффициент пересчета счетчика 7, а разрядность регистра 5 выбрать на единицу большей. Формула изобретения Устройство для вывода информации, содержащее первые элементы И, первые входы которых подключены к информационным входам устройства, а вторые входы - к его первому управляющему входу, выходы первых элементов и соединены с первыми входами первого регистра, выходы которого подключены к первым входам блока памяти, вторые рходы которого соединены с выходами дешифратора,подключенного ко второму регистру, соединенному с первыми блока управления, второй выхо которого подключен к блоку памяти, выходы которого соединены с первыми входами вторых элементов И, первый вход блока управления подключен ко второму управляющему входу устройства, отличающееся тем что, с целью повышения надежности, в него введены счетчик, сдвигающий регистр и элемент задержки, вход которого подключен ко второму управляющему входу устройства, а выход - ко вторым входам первого регистра Г вход

счетчика соединен с третьим управляющим входом устройства и тактовыми входами триггеров сдвигающего регистра, установочные входы которых, кроме первого подключены к выходам вторых элементов И, вторые входы которых соединены с выходом счетчика,подключенным ко второму входу блока управления, при этом информационный вход первого триггера и выход последнего триггера сдвигающего регистра подключены, соответственно, к шине нулевого потенциала и выходу устройства.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 488202, кл.С 06 F 3/04, 1976.

2.Комплекс АСВТ М-бООО, устройство СИД, документация д ВЗ. 048.025 ЭЗ (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обучения | 1986 |

|

SU1345234A1 |

| Устройство для коррекции ошибок в блоках памяти | 1985 |

|

SU1257708A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки /ЭЛТ/ | 1989 |

|

SU1633387A1 |

| Устройство для коммутации каналов передачи данных мониторной АСУ | 1990 |

|

SU1718257A1 |

| Устройство для ввода информации | 1990 |

|

SU1698890A1 |

| Мультиплексный канал | 1980 |

|

SU957199A1 |

| Устройство для вывода информации | 1982 |

|

SU1019429A1 |

| Устройство для регистрации состояний контролируемого блока | 1984 |

|

SU1236488A1 |

| Автокоррелятор | 1989 |

|

SU1617447A1 |

| Устройство для поиска перемежающихся неисправностей | 1986 |

|

SU1381511A1 |

Авторы

Даты

1980-07-23—Публикация

1978-01-05—Подача