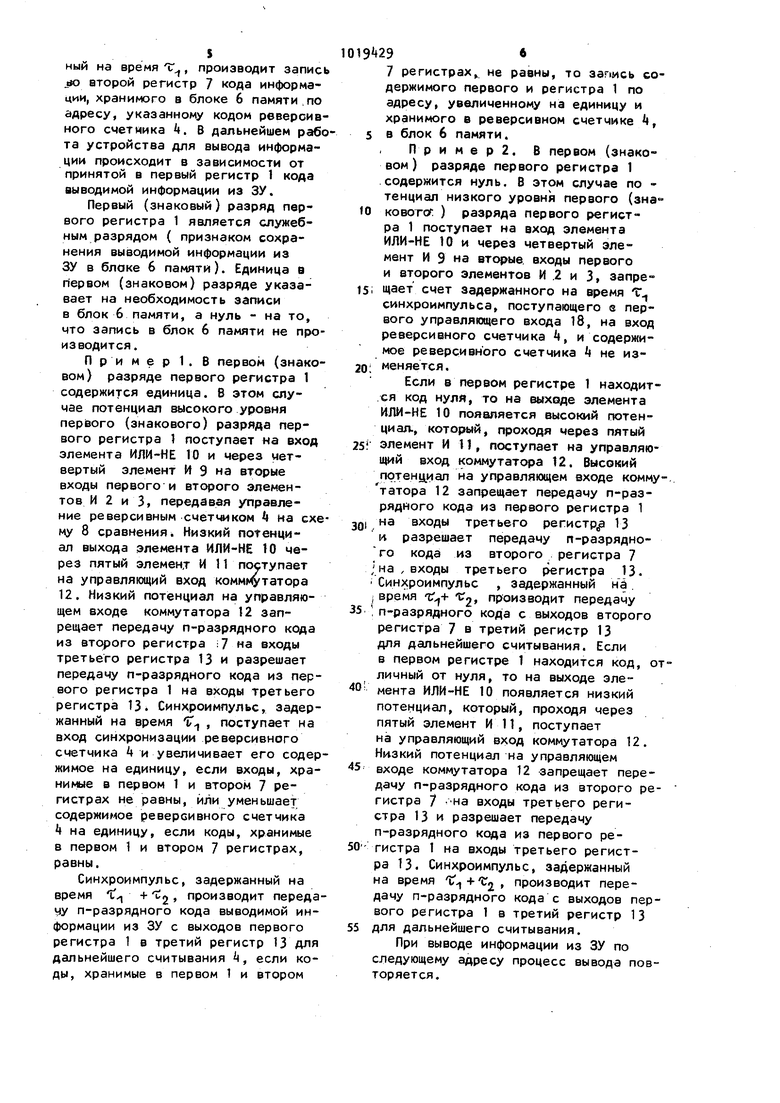

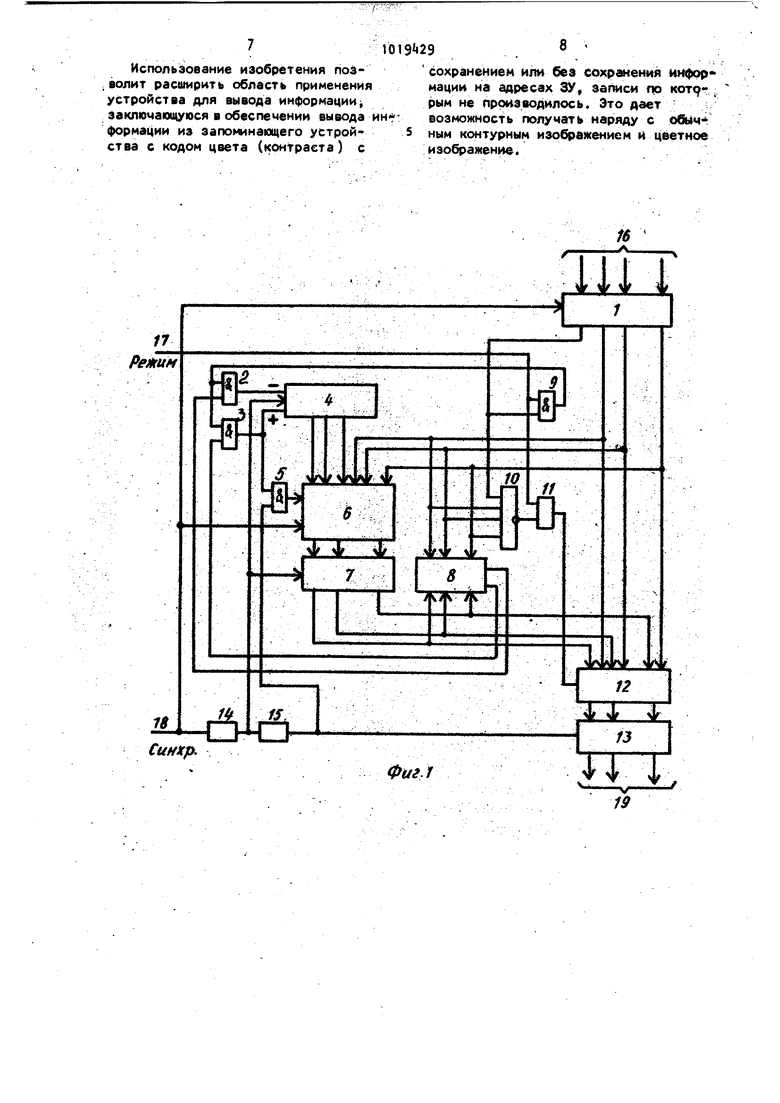

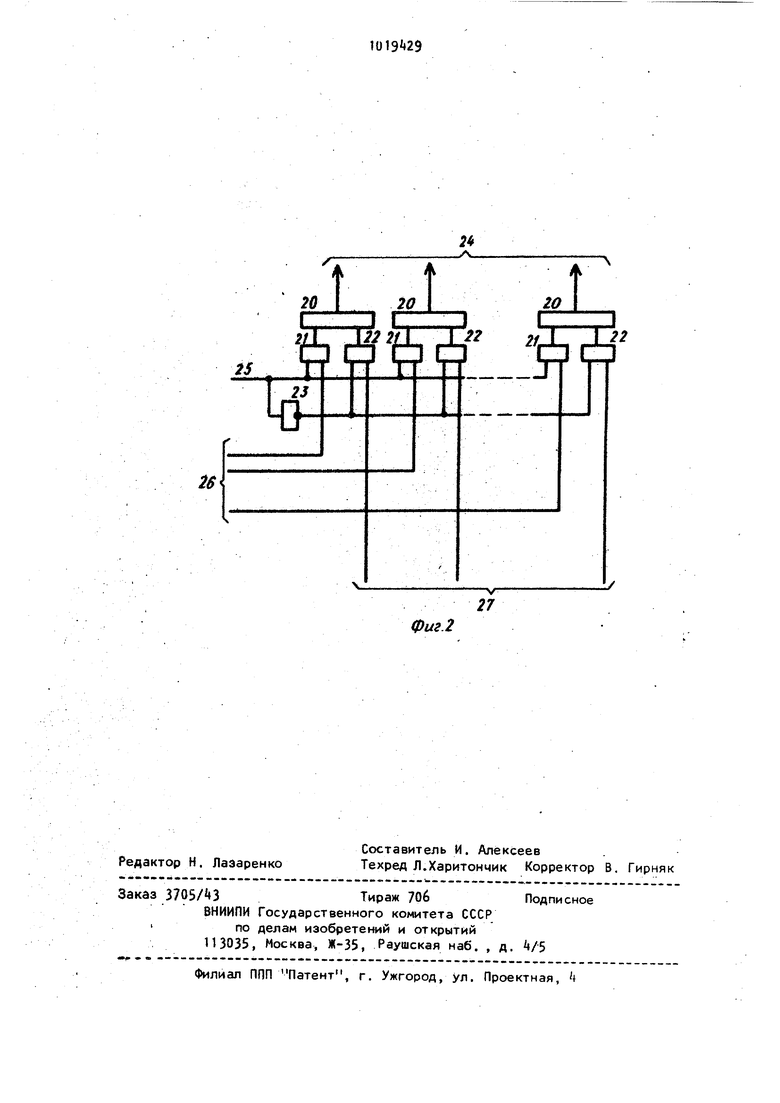

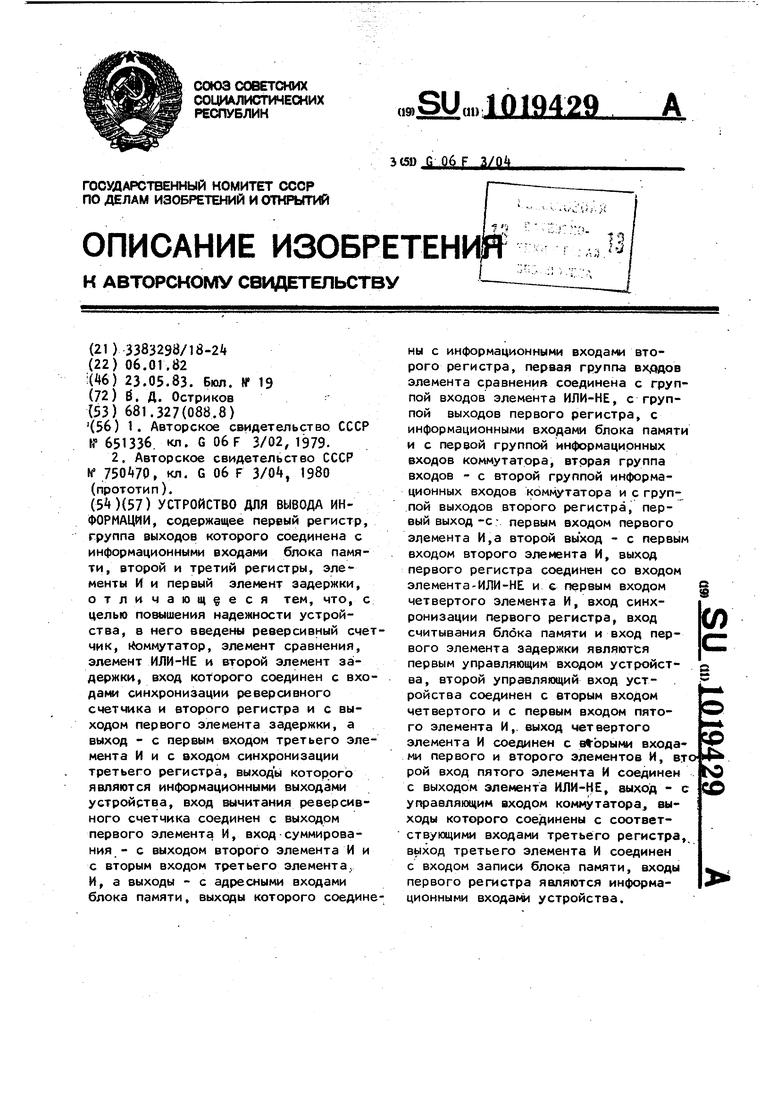

Изобретение относится к автоматике и вычислительной технике и пре назначено для вывода информации из запоминающего ycTponctsa для получения цветного изображения. Известно устройство для вывода информации, содержащее первый регис входы которого являются входами уст ройства, а выходы соединены с входами второго регистра, выходы которого являются выходами уст|эойства, первый триггер, первый вход которого подключен к входу устройства и первому элементу задержки, второй вход - к выходу элемента И, а выход - к входу первого регистра, второй элемент задержки, вход которого соединен с входом второго реги стра, выход первого элемента задерж ки подключен к первому входу элемен та И, второй триггер,первый вход ко рого подключен к выходу второго эле мента задержки,второй вход - к выходу элемента И, а выход - к втором входу элемента И 1 , Недостатком этого устройства является низкая помехозащищенность, так как при выводе портится информация в памяти. Наиболее близким по технической сущности к изобретению является устройство для вывода информации, содержащее первые элементы И, первые входы которых подключены к инфо мационным входам устройства, а вторые входы - к его первому управляющему входу, выходы первых элементов И соединены с первыми входами первого регистра, выходы которого подключены к первым входам блока памяти, вторые входы которого сое динены с выходами дешифратора, подключенного к второму регистру, соеди ненному с первыми выходами блока управления, второй вход которого подключен к блоку памяти, выходы которого соединены с первыми входами вто рых элементов И, первый вход блока управления подключен к второму управляющему входу устройства, счетчик, сдвигающий регистр и элемент задержки, вход которого подключен к второму управляюще.му входу устройства, а выход - к вторым входам первого регистра, вход счетчика соединен с третьим управляющим входом устройства и тактовыми входами триггеров сдвигающего регистра, установочные входы которых, кроме первого подключены к выходам вторых элемен тов И, вторые входы которых соединены с выходом счетчика, подключенным к второму входу блока управления, при этом информационный вход первого триггера и выход последнего триггера сдвигающего регистра подключены соответственно к шине нулевого потенциала и выходу устройства 2, Недостатком известного устройства является низкая надежность, так как информация в памяти портится при выводе. Цель изобретения - повышение надежности устройства. Поставленная цель достигается тем, что в устройство для вывода информации, содержащее первый регистр, группа выходов которого соединена с информационными входами блока памяти, второй и третий регистры, элементы И и первый элемент задержки, введены реверсивный счетчик, коммутатор, элемент сравнения, элемент ИЛИ-НЕ и второй элемент задержки, вход которого соединен с входами синхронизации реверсивного счетчика и второго регистра и с выходом первого элемента задержки, а выход - с первым входом третьего элемента И ис входом синхронизации третьего регистра,, выходы которого являются информационными выходами устройства, вход вычитания реверсивного счетчика соединен с выходом первого элемента И, вход суммирования - с выходом второго элемента И и с вторым входом третьего элемента И, а выходы - с адресными входами блока памяти, выходы которого соединены с информационными входами второго регистра, первая группа входов элемента сравнения соединена с группой входов элемента ИЛИ-НЕ, с группой выходов первого регистра, с информационными входами блока памяти и с первой группой информационных входов коммутатора, вторая группа входов - с второй группой информационных входов коммутатора и с группой выходов второго регистра, первый выход - с первым входом первого элемента И, а второй выход - с первым входом второго элемента И, выХОД первого регистра соединен с входом элемента (-НЕ, вход синхронизации первого регистра, вход считывания блока памяти и вход первого элемента задержки являются первым упра ляющим входом устройства, второй уп равляющий вход устройства соединен с вторым входом четвертого и с первым входом пятого элементов И, выход четвертого элемента И соединен вторыми входами первого и второго элементов И, второй вход пятого эле мента И соединен с выходом элемента ИЛИ-НЕ,выход - с управляющим вхо дом коммутатора, выходы которого со динены с соответствующими входами третьего регистра, выход третьего элемента И соединен с входом записи блока памяти, входы первого регистpa являются информационными входами устройства. На фиг. 1 приведена блок-схема у ройства для вывода информации; .-la фиг. 2 - блок-схема коммутатора. Устройство содержит первый pieгистр 1, первый 2 и второй 3 элемен ты И , реверсивный сметчик k, третий элемент И 5, блок 6 памяти, вто рой регистр 7, элемент 8 сравнения, четвертый элемент И 9, элемент ИЛИ-НЕ 10, пятый элемент И 11, коммутатор 12, третий регистр 13, пер вый Ц и второй 15 . элементы задержки, инфЬрмационные входы 1б, второй 17 и первый 18 управляющие входы и информационные выходы 19, элементы ИЛИ 20, элементы И первой 21 и второй 22 группы, инвертор 23, информационные выходы 2, управляющий вход 23, вторые 2б и первые 27 информационные входы коммутатора. В исходном состоянии устройстBio для вывода информации имеет на выходе реверсивного счетчика f} код адреса блока 6 памяти (установка в нуль реверсивного счетчика 4 прои водится извне, цепи установки в нул для упрощения не показаны),на выход регистра 13- код выводимой информации попредыдущему адресу ЗУ, на в ходах регистров 1 и 7 - код выводи, мой информации по предыдущему или более раннему адресу ЗУ, в блоке па мяти 6 находятся коды выводимой информации предыдущей строки ЗУ. Устройство для вывода информации работает в режиме Вывод, соответствующем наличию на втором управляющем входе устройства 17 потенциала низкого уровня, который, проходя через пятый элемент ИЛИ 11, поступает на управляющий вход коммутатора ,12 и через четвертый элемент И Э на вторые входы первого и второго элементов И 2 и 3.Низкий потенциал на управляющем входе коммутатора 12 запрещает передаму п-разрядного кода из второго рег 1стра 7 на входы третьего регистра 13 и разрешает передачу п-разрядного кода из первого регистра 1 на входы третьего . регистра 13. Низкие потенциалы на вторых входах первого и второго элементов И 2 и 3 запрещают смет задержанного на время Т синхроимпульса, поступающего с первого управляющего входа 1В на вход реверсивного счетчика А, и содержимое реверсивного счетчика k не изменяется . На выходе реверсивного счетчика, k присутствует код адреса блока 6 памяти. Синхроимпульс, поступивший по первому управля1С1Щему входу 18, производит прием кода выводимой информации из запоминающего устройства в первый регистр 1, считывание информации в выходной регистр блока 6 памяти по адресу, указанному кодом реверсивного счетчика , синхроимпульс, задержанный на время Т, производит запись во второй регистр 7 кода информации, хранимого в блоке 6 памяти по адресу, указанному кодом реверсивного счетчика 4. Синхроимпульс, задержанный на время Т + Т, производит передачу п-разрядного кода выводимой информации из ЗУ с выходов первого регистра 1 в третий регистр 13 для дальнейшего считывания. Первый .(знаковый) разряд первого регистра 1 не участвует в передаме и на работу устройства в данном режиме не оказывает влияния. Устройство для вывода информации работает также, в режиме Вы-вод с сохранением информации, соответствующем налимию на втором управляющем входе устройства 17 потенциала высокого уровня. Синхроимпульс, поступивший по первому управляющему входу устройства 18, производит прием кода выводимой информации из ЗУ в первый регистр 1 и считывание.информации в выходной регистр блока 6 памяти по адресу, указанному кодом реверсивного счетчика k. Синхроимпульс, задержанныи на время Т, производит запис «ю второй регистр 7 кода информации, хранимого в блоке 6 памяти,по адресу, указанному кодом реверсив ного счетника 4. В дальнейшем раб та устройства для вывода информации происходит в зависимости от принятой в первый регистр 1 кода выводимой информации из ЗУ. Первый (знаковый) разряд первого регистра 1 является служебным разрядом ( признаком сохранения выводимой информации из ЗУ в блоке 6 памяти). Единица в первом (знаковом) разряде указавает на необходимость записи в блок 6 памяти, а нуль - на то, что запись в блок 6 памяти не про изводится. П р и м е р 1. В первом (знако вом) разряде первого регистра 1 содержится единица. В этом случае потенциал высокого уровня первого (знакового) разряда первого регистра 1 поступает на вход элемента ИЛИ-НЕ 10 и через четвертый элемент И 9 на вторые входы первого и второго элементов И 2 и 3, передавая /правление реверсивным счетчиком 4 на сх Nty 8 сравнения. Низкий потенциал выхода элемента ИЛИ-НЕ tO через пятый элемент И 11 поступает на управляющий вход комм(4татора 12. Низкий потенциал на управляющем входе коммутатора 12 запрещает передачу п-разрядного кода из второго регистра :7 на входы третьего регистра 13 и разрешает передачу п-разрядного кода иЗ пер вого регистра 1 на входы третьего регистра 13. Синхроимпульс, задер жанный на время IT-, , поступает на вход синхронизации реверсивного счетчика 4 и увеличивает его соде жимое на единицу, если входы, хра нимые в первом 1 и втором 7 регистрах не равны, или уменьшает содержимое реверсивного счетчика на единицу, если коды, хранимые в первом 1 и втором 7 регистрах, равны. Синхроимпульс, задержанный на 2, производит перед уу п-разрядного кода выводимой ин формации из ЗУ с выходов первого регистра 1 в третий регистр 13 дл дальнейшего считывания , если ко ды, хранимые в первом 1 и втором 9 7 регистрах, не равны, то запись содержимого первого и регистра 1 по адресу, увеличенному на единицу и хранимого в реверсивном счетчике t, В блок 6 памяти. Пример2. В первом (знаковом ) разряде первого регистра 1 содержится нуль. В этом случае по тенциал низкого уровня первого (зна° ковотос ) разряда первого регистра 1 поступает на вход элемента ИЛИ-НЕ 10 и через четвертый элемент И 9 на вторые, входы первого и второго элементов И .2 и 3, запрещает счет задержанного на время Т синхроимпульса, поступающего а первого управляющего входа 18, на вход реверсивного счетчика k, и содержимое реверсивного счетчика не изменяется. Если в первом регистре 1 находится код нуля, то на выходе элемента ИЛИ-НЕ 10 появляется высокий потенциал., который, проходя через пятый элемент И 11, поступает на управляющий вход коммутатора 12. Высокий потенциал на управляющем входе комму-, татора 12 запрещает передачу п-разрядного кода из первого регистра 1 на входы третьего регистру 13 и разрешает передачу п-разрядного кода из второго регистра 7 на , входы третьего регистра 13. Синхроимпульс , задержанный на. время производит передачу п-разрядного кода с выходов второго регистра 7 в третий регистр 13 для дальнейшего считывания. Если в первом регистре 1 находится код, отличный от нуля, то на выходе элемента ИЛИ-НЕ 10 появляется низкий потенциал, который, проходя через пятый элемент И 11, поступает на управляющий вход коммутатора 12. Низкий потенциал на управляющем входе коммутатора 12 запрещает передачу п-разрядного кода из второго регистра 7 На входы третьего регистра 13 и разрешает передачу п-разрядного кеда из первого регистра 1 на входы третьего регистра 13. Синхроимпульс, задержанный на время f-,-fC2 , производит передачу п-разрядного кода с выходов первого регистра 1 в третий регистр 13 для дальнейшего считывания. При выводе информации из ЗУ по следующему адресу процесс вывода повторяется. Использование изобретения поз, волит расширить область применения устройства для вывода информации эакпючашцуюся в обеспечении вывода формации из запоминающего устройства с кодом цвета (контраста) с . сохранением или без шфэр мации на адресах ЗУ, записи по кот9г рым не производилось. Это дает возможность получать наряду с обич н ным контурным изо ажением и цветное изображение.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессора с памятью | 1983 |

|

SU1149272A1 |

| СПОСОБ ФОРМИРОВАНИЯ ИЗОБРАЖЕНИЯ НА ТЕЛЕВИЗИОННОМ ЭКРАНЕ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2090977C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С ТЕЛЕГРАФНЫМИ КАНАЛАМИ СВЯЗИ | 1979 |

|

SU826332A1 |

| Устройство для отображения информации | 1988 |

|

SU1624435A1 |

| Микропрограммное устройство управления с самоконтролем | 1985 |

|

SU1247871A1 |

| Дисплейный процессор | 1981 |

|

SU1292031A1 |

| Запоминающее устройство | 1987 |

|

SU1413674A1 |

| Устройство сопряжения процессора с памятью | 1985 |

|

SU1357967A1 |

| Устройство для вертикального сдвига строк на дисплее | 1986 |

|

SU1410091A1 |

| Устройство для отображения и редактирования информации на экране электронно-лучевой трубки | 1989 |

|

SU1695288A1 |

ill I

Ш

S i

Qt

.моек

Ж12-1Ж

9

т

t

4wy

13

CuHXp.

TT

Фиг r

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для вывода информации | 1977 |

|

SU651336A1 |

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР W , кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-05-23—Публикация

1982-01-06—Подача