Изобрете ще относится к вычислительной технике.

Цель изобретения - сокращение оборудования.

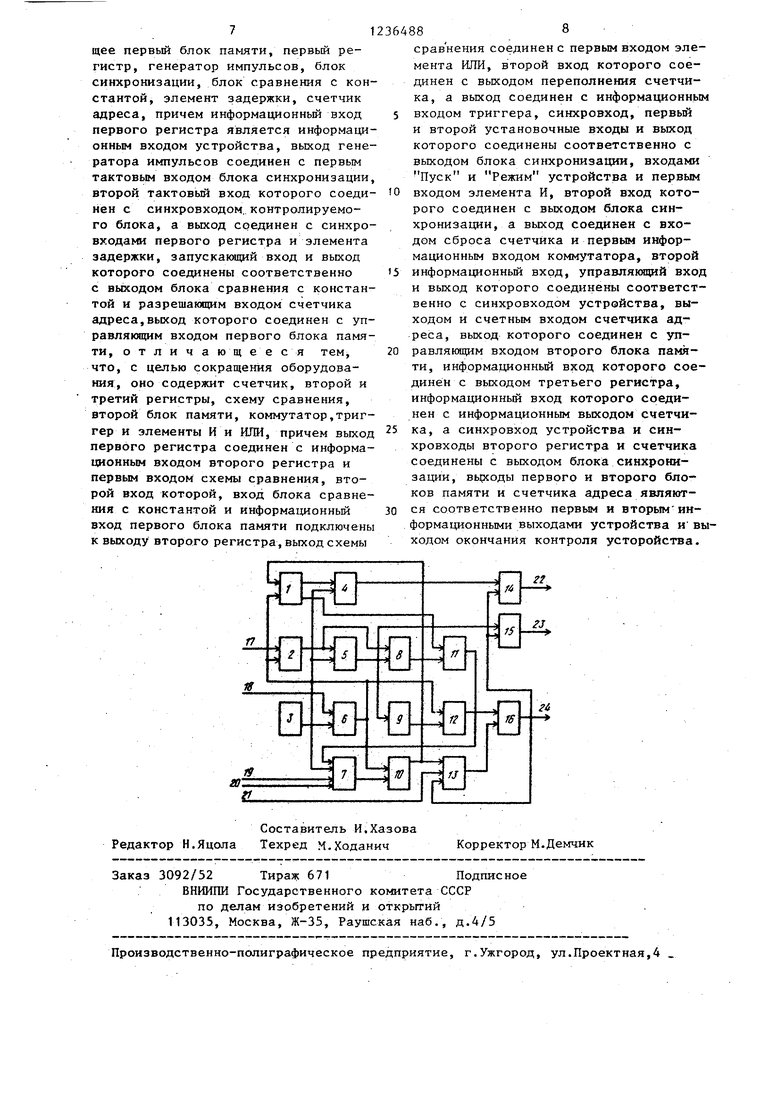

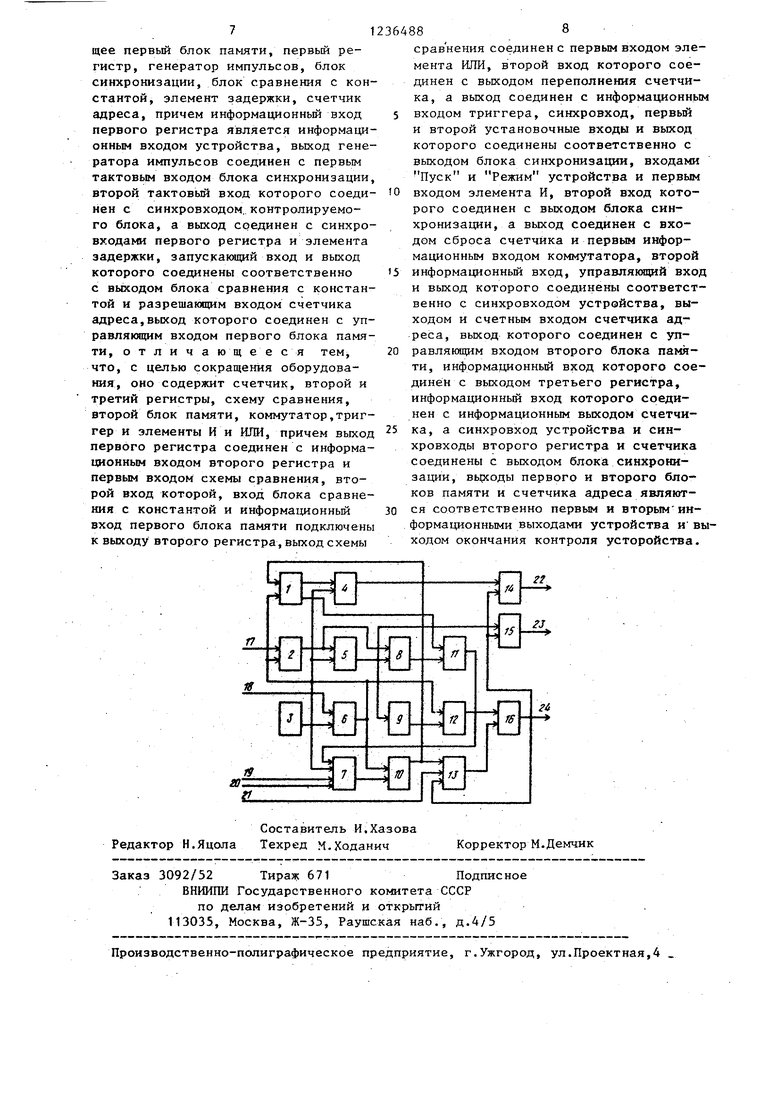

На чертеже представлена структурная схема устройства.

Устройство содержит счетчик 1,пер- вьй регистр 2, генератор 3 импульсов, третий 4 и второй 5 регистры, блок 6 синхронизации, триггер 7, схему 8 сравнения, блок 9 сравнения с константой, элементы И 10 и ИЛИ 11, элемент 12 задержки, кoм fyтaтop 13, второй блок 14 памяти, первый блок 15 памяти и счетчик 16 адреса, входы информационный 17, синхронизации 18 Режим 19, Пуск 20, синхронизации 21, информационные выходы 22 и 23, выход 24 конца контроля.

Устройство работает в трех режимах: регистрация логических состояний; регистрация времен ных диаграмм; пересылка данных в ЭВМ.

Режим регистрации логических состояний задается сигналом, поступающим на вход Режим 19 устройства, являющийся единичным установочным входом триггера 7. Начало работы устройства задается сигналом Пуск, равным единице, поступающим на вход устройства, являющийся нулевым установочным входом триггера 7. Значение сигнала Пуск, равное нулю, устанавливает триггер 7 в исходное нулевое состояние. Во времени сигнал Пуск предшествует сигналу Режим, исходное значение сигнала Режим - единица.

В режиме регистрации логических состояний устройство работает следующим образом.

Синхронизация устройства осуществляется посредством синхроимпульсов контролируемого блока, поступающих вместе с сигналом разрешения на вход 18 блока 6 синхронизации, который является синхронным входом устройства. Сигнал Режим, равный нулю, устанавливает в единичное состояние триггер 7 и блокирует его дальнейшее переключение по информационному входу,

тем самым открывая элемент И 10 дщя прохождения синхроимпульсов на пер- вьй информационньй вход коммутатора 13, Который транслирует сигнал с выхода элемента И 10 на вход счетчика 16 адреса.

В каждом такте синхронизации значение входных сигналов, поступающих по каналам связи на информационный вход устройства, запоминается в регистре 2, затем переписывается во второй регистр 5, с выхода которого поступает на второй блок 15 памяти. Занесение входных данных в блок 15 памяти начинается с такта синхронизации Т . Идентификация такта осуО.

ществляется по ожидаемому значению входных сигналов и коду задержки, выраженному в тактах синхроимпульсов. Значение входного сигнала и код

задержки заносятся оператором перед началом работы устройства соответственно в блок 9 и элемент 12 задержки. В процессе работы значение входных сигналов с выхода второго регистра 5 поступает на вход блока 9 и сравнивается с ожидаемым значением. При появлении слова, равного ожидаемому, на выходе блока 9 вырабатывается сигнал запуска элемента 12 задержки. С приходом запуска в элементе 12 задержки начинается отсчет тактов. Спустя заданный интервал времени, на выходе элемента 12 задержки вырабатывается сигнал, по которому в счетчике 16 начинается формирование сигналов управления первым блоком 15 памяти и вторым блоком 14 памяти, поступающих на их вход. По сигналам управления в блоке 15 памяти происходит регистрация значений входных сигналов - логических состояний контролируемого блока, при этом второй блок 14 памяти не используется.Процесс регистрации продолжается до момента переполнения счетчика 16 адреса. В момент переполнения счетчика адреса с его выхода в ЭВМ поступает сигнал об окончании режима регистрации. Этот же сигнал поступает на управляющий

вход коммутатора 13 и переключает его на. передачу сигналов, поступающих по его второму входу.

В режиме регистрации временных диаграмм устройство работает следующим образом.

Синхронизация устройства осуществляется посредством генератора 3 импульсов, с выхода которого синхроимпульсы поступают на второй вход бло- ка 6 синхронизации. Сигнал Режим, равный единице, не переключает триггер 7 из исходного нулевого состояния, и его прямой выход закрывает

3

элемент И 10 для прохождения синхроимпульсов на первый вход коммутатора 13. В каждом такте синхронизации значения входных сигналов, поступающих по каналам связи, запоминаются в регистре 2, после чего переписываются во второй регистр 5, одновременно с этим код с информационного выхода счетчика 1, которьй считает такты синхроимпульсов, переписывается в третий регистр 4. Затем содержимое второго 5 и третьего 4 регистров поступает на второй вход, соответственно первого блока 15 памяти и второго блока 14 памяти. Но запоминание данных в блоках памяти осуществляется только в тех тактах, в которых произопшо изменелие значения сигналов на информационном входе устройства либо переполнение счетчика 1. Факт изменения значения входных сигналов устанавливается схемой 8 сравнения путем сравнения данных, записанных в регистре 2 и втором регистре 5. Сигналы с выхода схемы 8 сравнения и с выхода переполнения счетчика 1 , объединенные элементом ИЛИ 11, поступают на информационный вход триггера 7, Если произошло изменение значения сигналов на информационном входе устройства, либо переполнился счетчик 1, на вькоде элемента ИЛИ 11 появляется единица, которая записывается в триггер 7.

Прямой выход триггера 7 открывает элемент И 10 для прохождения синхроимпульсов на первый информационный вход коммутатора 13. С выхода коммутатора 13 синхроимпульсы поступают на управляющий вход счетчика 16 и на вход счетчика 1. С приходом синхроимпульсов счетчик 16 работает так же, как в первом режиме, причем по сигналам управления в блоке 15 памяти происходит регистрация значений входных сигналов, а во втором блоке 14 памяти запоминаются величины временных интервалов (выраженные в тактах синхронизации) между тактами изменения входных сигналов либо переполнения счетчика 1. В отсутствии синхроимпульсов счетчик 16 находится в состоянии ожидания, и сигналы управления блоками 15 и 14 памяти сохраняют свое предьщущее значение. С приходом сигнала на второй вход счетчика 1 значение его обнуляется.

4884

В режиме пересыпки данных в ЭВМ синхронизация работы устройства осуществляется посредством синхроимпульсов ЭВМ, поступающих на синхронный вход 21 устройства, являюсцийся вторым входом коммутатора 13. В каждом такте синхронизации счетчик 16 формирует сигналы управления блоками 13 и 14 памяти, поступающие на их

вход. По сигналам управления зарегистрированные данные считываются из блоков 15 и 14 памяти и поступают соответственно на первый и второй информационные выходы устройства.

Завершается пересылка данных по переполнению счетчика 16 адреса.

Блок 6 синхронизации представляет собой коммутатор, реализованнъй, например, на элементах И или ИЛИ

(не показаны). При этом выходы пер- вого и второго элементов И соединены с входом элемента ИЛИ, выход которого является выходом блока синхронизации. Первые (прямой и инверсный) входы соответственно первого и второго элементов И соединены между собой и являются управляюшзим входом коммутатора. Вторые входы элементов И являются первым и вторым

информационным входами коммутатора, Группа входов, включаю1цая первый информационный вход коммутатора и его управляющий вход является первым входом блока синхронизации, вторым входом которого является второй информационный вход коммутатора. На выход блока 6 синхронизации транслируются либо синхроимпульсы контролируемого блока, поступакяцие на его первый вход, либо синхроимпульсы генератора 3, поступающие на его второй вход.

Схема 8 сравнения может быть построена на сумматорах по модулю два,

выходы которых объединены элементом ИЛИ (не показаны), первые входы подключены к выходу регистра 2, а вторые входы подключены к выходам второго регистра 5. На выходе схемы

сравнения, которым является вьрсоД элемента ИЛИ, вычисляется результат поразрядного сравнения кодов, поступающих на ее входы. Если коды равны между собой, результат сравнения принимает значение единицы, если нет - нуля.

Блок 9 сравнения с константой может быть реализован на регистре,сум

маторах по модулю два, элементе ИЛИ и триггере (не показаны). Причем входы регистра и установочный вход триггера подключены к тумблерам, выходы регистра соединены с первыми входами сумматоров по модулю два, вторые входы которых являются входом цифрового компаратора, а вькоды объединены элементом ИЛИ, сигнал с выхода элемента ИЛИ поступает на синхровход триггера, на информационном входе которого установлено значение логической единицы, выход триггера является вькодом цифрового компаратора. Перед началом работы с помощью тумблеров в регистр заносится ожидаемое значение входных сигналов, а триггер устанавливается в исходное нулевое состояние. В процессе работы на выходе элемента ИЖ вычисляется результат поразрядного сравнения ожидаемого кода и текущего кода, поступаимцего на вход блока. В момент равенства кодов сигнал на выходе элемента ИЛИ принимает значение единицы, т.е. формируется положительный фронт, которы устанавливает триггер в единичное состояние.

Элемент 12 задержки может вклю- чать в себя регистр, счетчик, cy fiyta- торы по модулю два и элемент ИЛИ (не показаны), при этом входы регистра подключены к тумблерам, а выходы - к первым входам сумматоров по моду- лю два, на вторые входы которых поступает код с выходов счетчика, установочный вход счетчика является первым входом блока задержки, соединенным с выходом блока 9, а синхровход счетчика является вт орым входом блока задержки, подключенным к выходу блока 6 синхронизации, выходы торов по модулю два объединены элементом ИЛИ, выход которого является выходом блока. В начальный момент времени с помощью тумблеров в регист заносится код, сигнал на первом входе элемента задержки, имеющий нулевое значение, устанавливает счетчик 3 нуль и блокирует его работу в режиме сложения. В момент времени, со- ответствуклций установлению единицы на первом входе блока задержки, счетчик переходит в режим сложения. На выходе элемента ИЛИ вычисляется результат поразрядного сравнения заданного кода и кода, снимаемого с

выходов счетчика. Как только коды сравняются,, сигнал с выхода элемента ИЛИ, который принимает значение единицы, закрывает вход разреп1ения счетчика. Счет импульсов прекращается и на выходе элемента задержки сохраняется значение единицы.

Коммутатор 13 может быть реализован на элементах И и ИЛИ (не показаны) , причем первые входы первого и второго элементов И являются соответственно первым и вторым информа- ционньпчи входами коммутатора, второй инверсный вход первого элемента И соединен с вторгз1м прямым входом второго элемента И и является управляющим входом коммутатора, выход элемента ИЛИ является выходом коммутатора. Если на управляющем входе коммутатора установлено значение нуля, то на его выход транслируются сигналы с первого информационного входа, в противном случае на вход пропускаются сигналы с второго информационного входа.

Счетчик 16 адреса может представлять собой счетчик и элемент И (не показаны)„ Причем синхровход счетчика соединен с первым входом элемента И и является разрешающим входом счетчика, на который с выхода блока 7 задержки поступает сигнал. Группа выходов, включакщая выходы счетчика и элемента И, является выходом блока управления. В начальный момент времени сигнал, равный нулю, устанавливает элемент И и счетчик в нуль, а также блокирует работу счетчика в режиме сложения. С приходом сигнала, равного единице, элемент И открывается для прохождения синхроимпульсов, а счетчик переходит в режим сложения На выходе элемента И формируется сигнал Выборка, со старшего разряда счетчика снимается сигнал ЗП/ЧТ, а с его младших разрядов, которые представляют собой счетчик адреса, снимается значение адреса. Перечисленные сигналы являются сигналами управления блоков 15 и 14 памяти, причем рехшму записи соответствует ЗП/ЧТ 0, а режиму чтения - ЗП/ЧТ 1. Сигнал ЗП/ЧТ поступает также на управляющий вход ко1 Ф1утатора и в ЭВМ. Формула изобретения

.Устройство для регистрации состояний контролируемого блока, содержа71

щее первый блок памяти, первый регистр, генератор импульсов, блок синхронизации, блок сравнения с константой, элемент задержки, счетчик адреса, причем информационньй вход первого регистра является информационным входом устройства, выход генератора импульсов соединен с первым тактовым входом блока синхронизации, второй тактовый вход которого соединен с синхровходом, контролируемого блока, а выход соединен с синхро- входами первого регистра и элемента задержки, запускающий вход и выход которого соединены соответственно с выходом блока сравнения с константой и разрешающим входом счетчика адреса,выход которого соединен с управляющим входом первого блока памяти, отличающееся тем, что, с целью сокращения оборудования, оно содержит счетчик, второй и третий регистры, схему сравнения, второй блок памяти, коммутатор,триггер и элементы И и ИЛИ, причем выход первого регистра соединен с информационным входом второго регистра и первым входом схемы сравнения, второй вход которой, вход блока сравнения с константой и информационньй вход первого блока памяти подключены к выходу второго регистра, выход схемы

Составитель И.Хазова Редактор Н.Яцола Техред М.Ходанич

Заказ 3092/52 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открьп-ий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

364888

срав нения соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом переполнения счетчика, а выход соединен с информационным 5 входом триггера, синхровход, первый и второй установочные входы и выход которого соединены соответственно с выходом блока синхронизации, входами Пуск и Режим устройства и первым

to входом элемента И, второй вход которого соединен с выходом блока синхронизации, а выход соединен с входом сброса счетчИка и первым информационным входом коммутатора, второй

)5 информационньй вход, управлякяций вход и выход которого соединены соответственно с синхровходом устройства, выходом и счетным входом счетчика адреса, выход которого соединен с уп20 равляницим входом второго блока памяти, информационньй вход которого соединён с выходом третьего регистра, информационньй вход которого соединен с информационным выходом счетчи25 ка, а синхровход устройства и син- хровходы второго регистра и счетчика соединены с выходом блока синхронизации, вьрсоды первого и второго блоков памяти и счетчика адреса являют30 ся соответственно первым и вторым информационными выходами устройства и выходом окончания контроля усторойства.

Корректор М.Демчик

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регистрации неисправностей | 1986 |

|

SU1429116A1 |

| Устройство для регистрации неисправностей | 1986 |

|

SU1377858A1 |

| Устройство для программируемой задержки информации | 1986 |

|

SU1381468A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1476466A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОРРЕЛЯЦИОННОЙ ФУНКЦИИ | 1992 |

|

RU2037198C1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439618A1 |

| Мультимикропрограммное устройство управления | 1983 |

|

SU1161942A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для сопряжения процессора с памятью | 1983 |

|

SU1149272A1 |

| Устройство для идентификации аналоговых сигналов | 1991 |

|

SU1789985A1 |

Изобретение относится к вьтисли- телыюй технике. Целью изобретения является сокращение оборудования путем уменьшения объема используемой памяти. Указанная цель достигается тем, что в устройство, содержащее регистр, блок синхронизации, генератор импульсов, блок памяти, цифровой компаратор, блок задержки, блок управления, причем информационньй вход регистра является информационным входом устройства, первый вход блока синхронизации является синхронным входом устройства, второй вход блока синхронизации соединен с выходом генератора импульсов, а выход подключен к синхровходу регистра, к второму входу блока задержки, первый вход которого соединен с выходом цифрового компаратора, а выход подключен к второму входу блока управления, выход которого соединен с первым входом блока памяти, введены счетчик, второй и третий регистры, схема сравнения, элементы И и ИЛИ, коммутатор, триггер и второй блок памяти, причем вьгход регистра соединен с первым входом схемы сравнения и информационным входом второго регистра, выход которого соединен с вторым входом схемы сравнения, вторым входом блока памяти и входом цифрового компаратора, синхровходы второго и третьего регистров счетчика, триггера и первый вход элемента И подключены к выходу блока синхронизации, выход переполнения счетчика соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом схемы сравнения, а выход подключен к информаци- ониому входу триггера, установочный вход R которого является входом Пуск устройства, а установочный вход является входом Режим устройства, выход триггера подключен к второму входу элемента И, выход которого подключен к второму входу счетчика и к первому информационному входу коммутатора, второй информационный вход которого является вторым синхронным входом устройства, а выход соединен с управляющим входом блока управления, вьгход которого подключен к управляющему входу коммутатора, первому -входу второго блока памяти и является выходом управления устройства, информационньй выход счетчика соединен с информационным входом третьего регистра, выход которого подключен к второму входу второго блока памяти,выходы первого и второго блоков памяти являются соответственно первым и BTopbiM информационны- ьш выходами устройства. 1 ил. i (Л CZ to оо а 4: 00 СХ)

| Устройство для контроля цифровыхСигНАлОВ | 1978 |

|

SU809006A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля логических схем | 1978 |

|

SU744580A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-06-07—Публикация

1984-09-21—Подача