(54) РЕГИСТР СДВИГА

1

Изобретение относится к области цифровой вычислительной техники и дискретной автоматики на интегральных схемах.

Одной из важнейших задач построения узлов цифровой вычислительной техники и дискретной автоматики на основе потенциальных логических элементов и универсальных триггеров является обеспечение функциональной надежности. Устройство будет функционально надежным, если оно не содержит опасных состязаний. Условием исключения опасных состязаний в регистрах ю сдвига является обеспечение тактирования всех разрядов от одного источника тактовых импульсов.

Известно ступенчатое построение генератора тактовых импульсов, при котором обеспечение необходимой нагузочной способности генератора тактовых импульсов осуш,ествляется путем ступенчатого размножения тактовых импульсов на микросхе.мах той же серии, на которой построено все цифровое устройство 1.20

Однако при таком методе каждый отдельный выходной формирователь тактовых импульсов имеет ограниченную нагрузочную способность. Поскольку в практике построения цифровых устройств используются регистры сдвига со значительным числом разрядов (24, 48, 64, 128), то выполнить условие отсутствия опасных состязаний без дополнительного оборудования невозможно.

Наиболее близким из известных по технической сущности является регистр сдвига, содержащий дополнительный RS-триггер 2.

Однако этот регистр сдвига построен на элементах И-НЕ (ИЛИ-НЕ), образующих Т-триггер, в котором для работы дополнительного RS-триггера используется специфическая информация, вырабатываемая внутри разряда.

В настоящее время весьма актуальной задачей является построение регистров сдвига на основе универсальных JK-триггеров. Для обеспечения функциональной надежности регистров сдвига на основе JK-триггеров возможно использовать дополнительный RS-триггер.

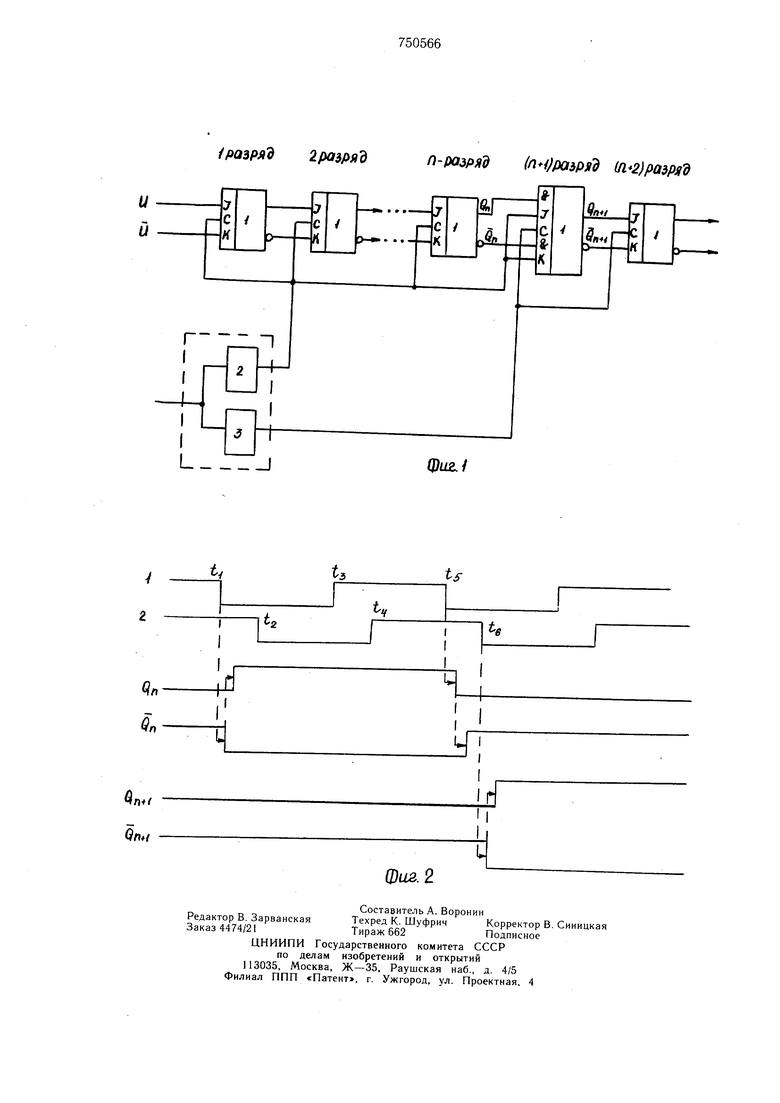

Использование дополнительного состава оборудования для обеспечения функциональной надежности является недостатком известного устройства. Цель изобретения - упрощение регистра сдвига. Поставленная цель достигается тем, что в регистре сдвига, содержащем в каждом разряде JK-триггеры, причем С-входы JKтриггеров первый и второй группы разрядов соответственно соединены с выходами первого и второго формирователей тактовых импульсов, выход первого формирователя тактовых импульсов и выход второго формирователя тактовых импульсов соединены соответственно с дополнительными входами первого JK-триггера второй группы разрядов. На фиг. 1 приведена функциональная схема предлагаемого регистра сдвига; на фиг. 2 - временная диаграмма регистра сдвига. Он содержит первую группу п разрядов и вторую группу (п + ш) разрядов. Каждый разряд выполнен на JK-триггере 1. Регистр сдвига также содержит формирователи 2 и 3 тактовых импульсов. Работу регистра сдвига рассмотрим на примере использования JK-триггеров с позитивной входной логикой и негативным управлением по тактовым импульсам. Пусть разброс времени задержки срабатывания формирователей 2 и 3 определяется временным сдвигом (ta--ti ) (t4-ta) (tg-ts). В момент t( П-ЫЙ разряд воспринимает входную информацию и изменяет свое состояние. Одновременно с этим на дополнительные J и К входы (п + 1)Го разряда поступает сигнал логического нуля с выхода формирователя 2 и поэтому изменение состояний выходов п-го разряда не может быть воспринято (п + 1)-ым разрядом. Начиная с момента з (п-f 1)-ый разряд воспринимает новое состояние выходов п-го разряда. В момент U (п + 1)-ый разряд начинает воспринимать информацию, поступающую на его J и К входы с выхода п-го разряда. С момента if, в п-ом и (п + 1)-ом разрядах идут процессы, аналогичные переходам в момент t(. Отсутствие соединения выхода формирователя 2 с дополнительными J и К входами (п + 1)-го разряда привело бы к тому, что, например, в момент tj состояние логической единицы с выхода п-го разряда распространилось бы на выход (п + 1)-го разряда. Следовательно, за время действия одного такта информация распространилась бы на два разряда регистра, т. е. произошел бы сбой, определяемый наличием опасных состязаний. Сдвиг сигналов на выходах формирователей 2 и 3, при котором tt tt, не является опасным, так как при этом условии сигнала происходят переключения в последующем разряде, а в предыдущем. Поэтому к моменту, когда на J и К входах (п + 1)-го разряда начинается изменение состояния, эти входы будут отключены тактовым импульсом с выхода формирователя 3. Таким образом, предложенный регистр сдвига упрощается по сравнению с известным, так как не требует при своей реализации дополнительного оборудования при тактировании его от нескольких формирователей ГТИ. Формула изобретения Регистр сдвига, содержащий в каждом разряде JK-триггеров, причем С-входы JKтриггеров первой и второй группы разрядов соответственно соединены с выходами первого и второго формирователей тактовых импульсов, отличающийся тем, что, с целью упрощения регистра сдвига, в нем выход первого формирователя тактовых импульсов и выход второго формирователя тактовых импульсов соединены соответственно с дополнительными входами первого JK-триггера второй группы разрядов. Источники информации, принятые во внимание при экспертизе 1.Потемкин И. С.. Функциональные узлы на потенциальных элементах. М., «Энергия, 1976, с. 93-96, рис. 63. 2.Авторское свидетельство СССР № 432602, кл. G И С 19/00, 1972 (прототип) .

разряЪ

( )роьряд

| название | год | авторы | номер документа |

|---|---|---|---|

| Регистр сдвига | 1977 |

|

SU1076950A1 |

| -Разрядный регистр сдвига | 1977 |

|

SU746734A1 |

| РЕГИСТР СДВИГА | 1972 |

|

SU432602A1 |

| Регистр сдвига | 1978 |

|

SU771724A1 |

| -Разрядный регистр сдвига | 1973 |

|

SU594529A1 |

| Устройство для извлечения квадратного корня | 1987 |

|

SU1425662A1 |

| -Разрядный регистр сдвига | 1973 |

|

SU503296A1 |

| Ячейка памяти для регистра сдвига | 1979 |

|

SU858106A1 |

| Синхронный счетчик | 1985 |

|

SU1257838A1 |

| Устройство для определения свойств полноты логических функций | 1984 |

|

SU1170446A1 |

.

ts

Авторы

Даты

1980-07-23—Публикация

1977-09-05—Подача