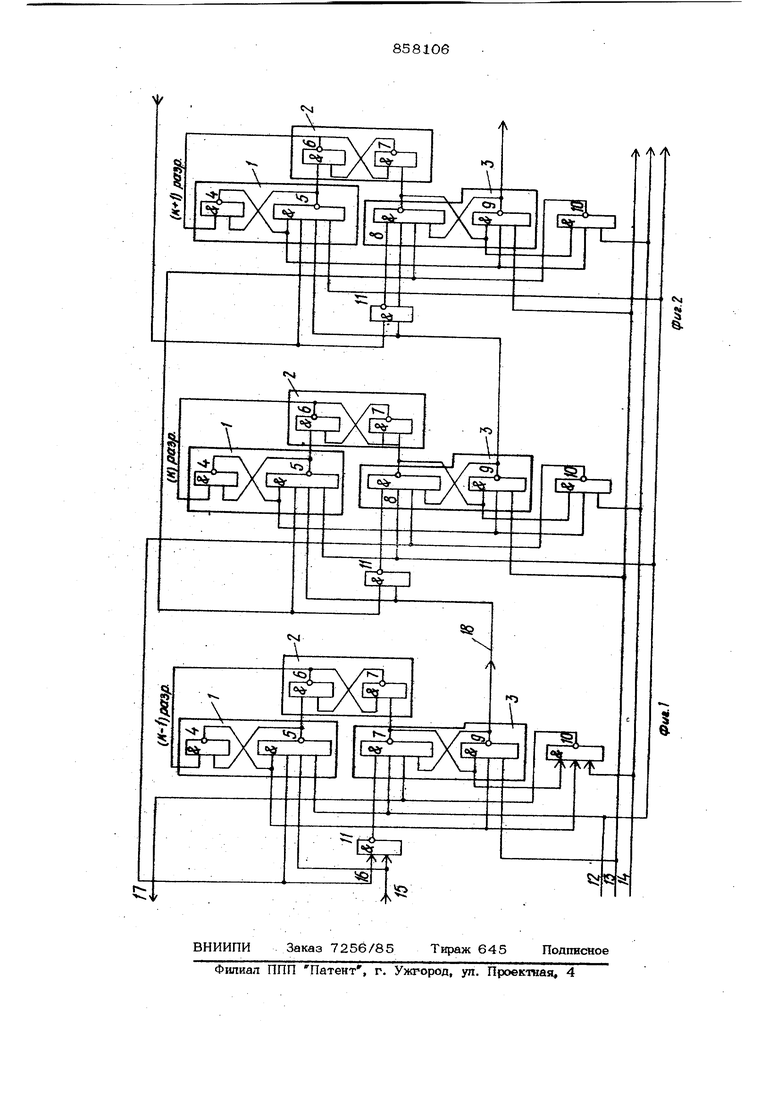

Изобретение относится к построенто устройств цифровой вычислительной текНИКИ и дискретной автоматики на потенциальных логических элементах и может быть испольа ано для построения реверсивных регистров сдвига. Известны функционально надежные (не содержащие опасных состязаний) регистры сдвига, построенные на потеншн апьных логических элементах И-НЕ, каж дый разряд которых содержит три fiS триггера, причем первый выход лервого триггера соединен с s -входом третьего триггера, а первый выход второго триггера соединен с R -входсм третьего триггера, первый выход первого триггера соединен с G -входом первого триггера, второй выход первого триггера соединен с R -входом второго, а первый вход ре стра соединен с 5 -входами первого и второго триггеров TlJ . Известен также р ерсивный регистр сдвига, построенный на основе однонаправленного регистра сдвига. Реверсивный регистр сдвига отличается небольшим чиспом логических элйу«ентав (8), отсутствием опасных состязанийC2l. Однако данный регистр имеет большое число соединений (30). Наиболее близким к предлагаемой по технической сущности является ячейка памяти для- р ерсивного регистра сдвига, которая выполнена на трех треггерах, например, RS -триггерах, двух элементах И-НЕ. Ячейка памяти с использованием известных методов реверса не содержит опасных состязаний, имеет небольшое число соединений (21) sj . Однако известная ячейка требует большего числа логических элет ентсж(10) Цель изобретения - упрощение ячейки памяти. Поставленная пепь достигается тем, что в ячейке памяти для репютра сдвига, содержащее первый триггер, один из выходсж которого- соединен с одним из входе второго триггера, третий триггер, первый выход которого подключен ко р- прому входу второго триггера, выход второго триггера соединен с одним из входов первого триггера, другой выход которого подсоединен к одному из входов третьего триггера, другие входы первого и третьего триггеров соединены с первой шиной управления, один из входов первого элемента И-НЕ подключен ко второй шине управления, второй элемент И-НЕ, входы которого соединены с информационными входами ячейки памяти, и третью шину управления, в которой выход первого элемента И-НЕ соединен с третьим входом третьего триггера и первым выходом ячейки памяти, другой и третий входы первого элемента И-НЕ соединены соответственно с другим выходам первого . триггера и первым выходом третьего триггера, четвертый вход третьего тркг- гера подключен к третьей шине упр пения выход второго эпаиента И-НЕ соединен с пятым входом третьего триггера, второй выход которого подсоединен ко второму выходу ячейки памяти, соответству- юшие информационные входы которой соединены с входами первого триггера. На фиг. 1 изображена функциональная схема предложенной ячейки памят на фиг. 2-вариант построения реверсивного регистра сдвига на предложенной ячейке памяти. Ячейка памяти содержит триггеры 1-3 выполненные соответственно на элементах И-НН 4 и 5, 6 и 7, 8 и 9, элементы И-НЕ 10 и 11, шины 12-14 управления, информационные входы 15 и 16 и выходу 17 и 18 ячейки памяти. Триггеры I - 3 выполнены по схеме R -триггера. Ячейка памяти функционирует следуюшим образом. Работу рассмотрим на примере функционирования реверсивного регистра сдвига, выполненного на предложенной ячейке памяти. Сдвиг вправо происходит при подаче сигнала логической 1 на щину 13 и логического О на шину 14. Синхроимпульсы подаются на шину 12. При этом на выходе элемента 1О каждого разряда поддерживается сигнал логической 1, а с выхода элемента 9 каждого разряда информация передается к последующему разряду. Сдаиг впево происходит при подаче сигнала логического О на шину 13 и логической 1 на шину 14. Приэтом на выходе элемента 9 каждого разряда поддерживается сигнал логической , а с выхода элемента 1О каждого разряда информация передается к предыдущему разряду.

Таким образом, предложенная ячейка

памяти имеет 8 логических элементов с общим количествен входов - 22. Относительная эконся 5ия количества логических элементов по сравнению с известной ячейкой составляет 20%. .

Формула Изобретения

Ячейка памяти для регистра сдвига, содержащая первый триггер, один из выходов которого соединен с одним из входов второго триггера, третий триггер, первый выход которого подключен ко второму входу второго триггера, выход вто- . рого триггера соединен с одним из входе первого триггера, другой выход которого подсоединен к одному из входе третьего триггера, другие входы первого и третьего триггеров соединены с первой шиной управления, один из входов первого элемента И-НЕ подключен ко второй шине управления, второй элемент И-НЕ, входы которого соединены с информационными входами ячейки памяти, и третью шину управления, отлич ающаяся тем, что с целью упрощения ячейки памяти, в ней выход первого элемента И-НЕ соединен с третыа«5 входом третьего триггера и первым выходсад ячейки памяти, другой и третий входы первого элемента И-НЕ соединень соответственно с другим выходом первого триггера и первым выходем третьего триггера, четвертый вход третьего треттера подключен к третьей шине управления, выход второго элемента И-НЕ соединен с -пятым входом третьего триггера, второй выход которого подсоединен ко второму выходу ячейки памяти, соответствукацие информационные входы которой соединены с входами первого триггера. Источники информации, принятые во внимание при экспертизе 1. Проектирование микроэлектронных ци{) устройств. Под ред. С. А. Майорова. М. , Советское радио, 1977, с. 185-190, рис. 5. 26.-5.28. 2.Авторское свидетельство СССР № 474853, кл. G 11 С 19/ОО, 1975. 3.Проектирование микроэлектронных цифровых устройств. Под ред. С. А. Майорова. М. , Советское радио , 1077, с. 202, рис. 5. 36 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный регистр сдвига | 1971 |

|

SU474853A1 |

| Ячейка памяти для сдвиговогоРЕгиСТРА | 1976 |

|

SU809382A1 |

| Реверсивный регистр сдвига | 1990 |

|

SU1721632A1 |

| Ячейка памяти для реверсивногоРЕгиСТРА СдВигА | 1979 |

|

SU801102A1 |

| Регистр сдвига | 1979 |

|

SU858108A1 |

| Реверсивный буферный регистрСдВигА | 1979 |

|

SU841050A1 |

| Устройство для сопряжения ЦВМ и накопителя информации | 1985 |

|

SU1265780A1 |

| ДВУХКАСКАДНЫЙ ДИНАМИЧЕСКИЙ СДВИГОВЫЙ РЕГИСТР | 2014 |

|

RU2542898C1 |

| Реверсивный регистр сдвига | 1979 |

|

SU830577A1 |

| Устройство для сдвига со встро-ЕННыМ КОНТРОлЕМ | 1979 |

|

SU809386A1 |

Авторы

Даты

1981-08-23—Публикация

1979-06-27—Подача