(54) ПРЕОБРАЗОВАТЕЛЬ ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Зарядно-пусковое устройство | 1988 |

|

SU1647768A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ИНТЕРВАЛ ВРЕМЕНИ | 1991 |

|

RU2032269C1 |

| ЧАСТОТНО-ИМПУЛЬСНОЕ МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕУСТРОЙСТВО | 1972 |

|

SU424188A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ СОВМЕЩЕННОГО ИНТЕГРИРОВАНИЯ | 1992 |

|

RU2036559C1 |

| Устройство для автоматического измерения параметров колебательных контуров | 1986 |

|

SU1406525A1 |

| Интегрирующий аналого-цифровой преобразователь | 1985 |

|

SU1279069A1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1293842A1 |

| Автоматический измеритель параметров радиотехнических устройств и элементов | 1988 |

|

SU1756833A1 |

| Зарядно-пусковое устройство | 1987 |

|

SU1534632A1 |

| Фазоимпульсный преобразователь | 1989 |

|

SU1691947A1 |

1

Изобретение относится к автоматике и вычислительной технике, в частности к устройствам для преобразования двух последовательностей импульсов в третью импульсную последовательность, длительность импульсов и частота их следования которой соответственно равны периоду следования импульсов одной последовательности и частоте следования другой последовательности.

Известно устройство для преобразования импульсов, содержащее источник эталонного тока, ключ, интегрирующую емкость, компаратор, триггер и источник эталонного напряжения 1.

Недостаток устройства - ограниченные функциональные возможности.

Наиболее близким является преобразователь импульсов, содержащий перЬый элемент И, подключенный первым входом к первой входной шине преобразователя импульсов, вторым входом - к выходу первого триггера, а выходом - к счетному входу второго триггера, первый выход которого соединен с первым установочным входом первого триггера, подключенного вторым установочным входом к выходной шине преобразователя импульсов и к первому

выходу третьего триггера, соединенного установочными входами соответственно с второй входной шиной преобразователя импульсов и выходом компаратора, подключенного первым входом к шине нулевого потенциала, , а вторым входом - к выходу блока преобразования длительности импульсов в напряжение, входы которого соответственно соединены с вторыми установочными входами второго и третьего триггеров 2.

Недостаток устройства - ограниченный

10 частотный диапазон изменения входных сигналов, а именно максимальная частота второй импульсной последовательности должна быть в три раза меньше частоты первой импульсной последовательности. Это ограничение вызвано тем, что после окончания

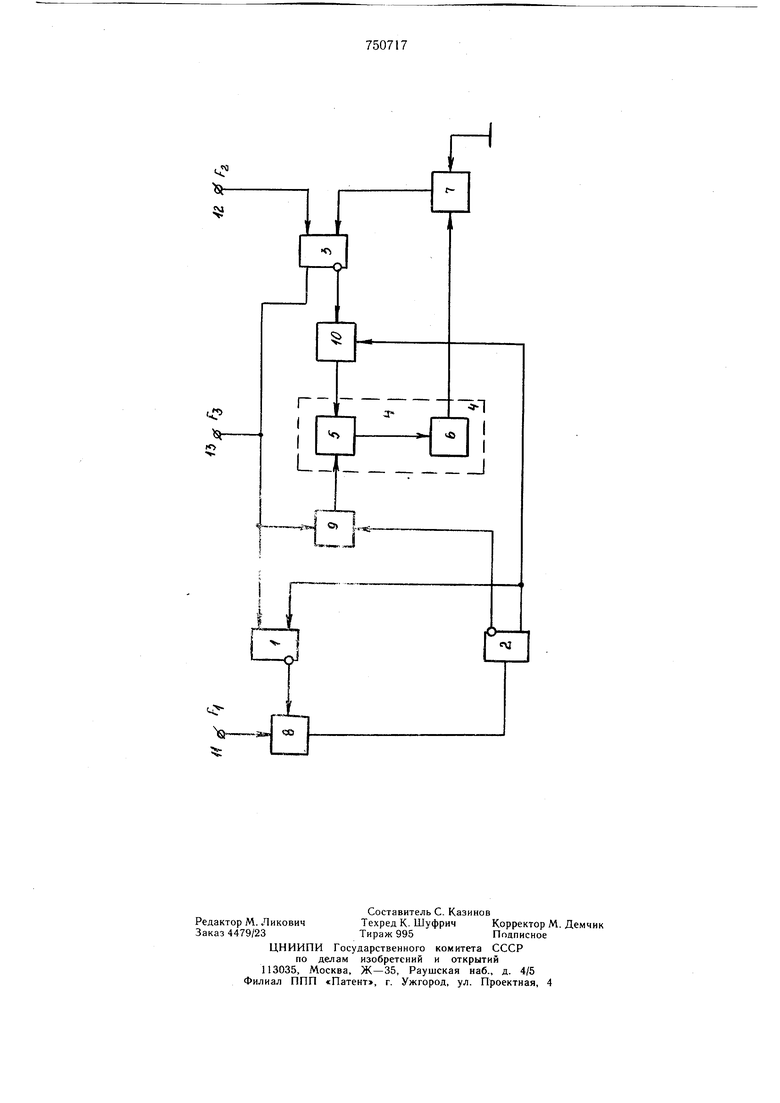

15 выходного импульса устройство с приходом очередного импульса первой последовательности переходит в режим заряда, который длится в течение времени одного периода следования импульсов первой последовательности, и если в течение этого времени приходит импульс второй последовательности, то работа устройства становится неустойчивой из-за возможности одновременного включения цепей заряда и разряда блока преобразователя длительности импульсов в напряжение. Цель изобретения - расширение частотного диапазона. С этой целью в преобразователь импульсов, содержащий первый элемент И, подключенный первым входом к первой входной шине преобразователя импульсов, вторым входом - к выходу первого триггера, а выходом - к счетному входу второго триггера, первый выход которого соединен с первым установочным входом первого триггера, подключенного вторым установочным входом к выходной шине преобразователя импульсов и к первому выходу третьего триггера, соединенного установочными - входами соответственно с второй шиной преобразователя импульсов и выходом компаратора, подключенного первым входом к шине нулевого потенциала, а вторым входом - к выходу блока преобразования длительности импульсов в напряжение, дополнительно введены второй и третий элементы И, подключенные выходами к входам блока преобразования длительности импульсов в напряжение, причем первый вход второго элемента И, подключенного вторым входом к второму выходу второго триггера, соединен с первым выходом третьего триггера, подключенного вторым выходом к первому входу третьего элемента И, второй вход которого соединен с первым выходом второго триггера. На чертеже изображена блок-схема устройства. Преобразователь импульсов содержит первый, второй и третий триггеры 1, 2, 3, блок 4 преобразования длительности импульсов в напряжение,выполненный на источнике 5 постоянного по величине зарядноразрядного тока и интегратора 6, компаратор 7, первый, второй и третий элементы И 8, 9 и 10. Элемент И 8 подключен первым входом к первой входной шине 11 преобразователя импульсов и соединен вторым входом с выходом (инверсным) триггера 1. Выход элемента И 8 подключен к счетному входу триггера 2, соединенного первым выходом с первым установочным входом триггера 1 и с вторым входом элемента И 10. Второй (инверсный) выход триггера 2 подключен к второму входу элемента И 9. Выходы элементов И 9 и 10 соединены соответственно с входами блока 4 преобразования длительности импульсов в напряжение, подключенного выходом к второму входу компаратора 7. Выход компаратора 7, соединенного первым входом с шиной нуле-вого потенциала, подключен к одному установочному входу триггера 3, другой установочный вход которого соединен с второй входной шиной 12 преобразователя импульсов. Первый выход триггера 3 подключен к второму установочному входу триггера 1, первому входу элемента И 9 и выходной шине 13 преобразователя импульсов. Второй (инверсный) выход триггера 3 соединен с первым входом элемента И 10. Работает устройство следуюш,им образом. Первая последовательность импульсов FI поступает на шину 11, соединенную с первым входом элемента И 8. Вторая импульсная последовательность В поступает на шину 12, соединенную с одним из установочных входов триггера 3 (входом установки триггера в нуль). Перед началом работы триггер 1 находится в нулевом состоянии, а триггеры 2 и 3 - в единичном состоянии. При этом на второй вход элемента И 8 подан разрешаюш,ий потенциал с выхода триггера 1, аналогично с первых выходов триггеров 2 и 3 поданы разрешающие потенциалы на второй вход элемента И 10 и первый вход элемента И 9 соответственно. Срабатывание триггеров 1-3 происходит в моменты изменения на их входах низкого потенциала на высокий. В момент прихода первого импульса последовательности FI открывается элемент И 8, выходной импульс которого переключает триггер 2 в нулевое состояние. Потенциалом с второго выхода триггера 2 открывается элемент И 9, а сигналом с выхода элемента И 9 включается в источнике 5 цепь заряда интегратора 6. Зарядный ток поступает на интегратор б до момента прихода следующего импульса FI . В момент прихода этого импульса сигналом с выхода элемента И 8 триггер 2 возвращается в исходное единичное состояние. При этом низким потенциалом с второго выхода тригrgpa 2 закрывается по второму входу элемент И 9, а высоким потенциалом с первого выхода триггера 2 открывается по второму входу элемент И 10. При появлении высокого потенциала на первом выходе триггера 2, его передним фронтом устанавливается в единичное состояние триггер 1 (несмотря на наличие на его втором входе ВЫСОКОГО потенциала с первого выхода триггера 3). При этом закрываются элементы И 8 и 9, а на интеграторе 6 запоминается напряжение, пропорциональное временному интервалу между двумя импульсами последовательности FI . В момент прихода импульса F триггер 3 устанавливается в нулевое состояние. При этом на первом выходе триггера 3 и, соответственно, выходной щине 13 формируется передний фронт выходного сигнала FJ и закрывается по первому входу элемент И 9. Сигналом с второго выхода триггера 3 через элемент И 10 включается в источнике 5 цепь разряда интегратора 6. В момент перехода выходного напряжения интегратора 6 через нуль на выходе компаратора 7 появляется сигнал, который возвращает тригrep 3 в единичное состояние. Низким потенциалом второго выхода триггера 3 закрывается по первому входу элемент И 10, выключая цепь разряда интегратора 6. Высоким потенциалом первого выхода триггера 3 открывается по первому входу элемент И 9 и возвращается в нулевое состояние триггер 1, который открывает по второму входу элемент И 8. На выходной шине 13 формируется задний фронт выходного сигнала устройства.

С приходом очередного импульса последовательности FI триггер 2 снова устанавливается в нулевое состояние, открывая элемент И 9 и включая в источнике 5 цепь заряда интегратора 6. Если при этом очередной импульс последовательности R приходит до окончания заряда интегратора 6, то при установке триггера 3 в нулевое состояние на его первом выходе появляется низкий потенциал, по переднему фронту которого на выходной шине 13 формируется передний фронт нового импульса последовательности Fi и закрывается элемент И 9, включая цепь заряда интегратора 6. С приходом следующего импульса последовательности FI триггер 2 возвращается в единичное состояние. При этом закрывается по второму входу эЛемент И 9, устанавливается в единичное состояние триггер 1 (закрывая элемент И 8) и открывается элемент И 10, выходной сигнал которого включает в источнике 5 цепь разряда интегратора 6. По окончанию разряда интегратора 6 блока 4 триггер 3 возвращается в единичное состояние. Соответственно закрывается элемент И 10, открывается по первому входу элемент И 9, на выходе устройства формируется задний фронт последовательности Б и возвращается в нулевое состояние триггер 1. В дальнейшем работа устройства протекает аналогичным образом.

Таким образом, предлагаемое устройство в отличие от известного обеспечивает нормальную работу при поступлении импульсов второй последовательности F. не только после окончания процесса заряда интегратора блока преобразования длительности импульсов в напряжение, но и до окончания процесса заряда, что позволяет увеличить частотный диапазон изменения входных сигналов.

Формула изобретения

Преобразователь импульсов, содержащий первый элемент И, подключенный первым входом к первой входной шине преобразователя импульсов, вторым входом - к выходу первого триггера, а выходом - к счетному входу второго триггера, первый выход которого соединен с первым установочным входом первого триггера, подключенного вторым установочным входом к выходной шине преобразователя импульсов и к первому выходу третьего триггера, соединенного установочными входами соответственно с второй входной шиной преобразователя импульсов и выходом компаратора, подключенного первым входом к шине нулевого потенциала, а вторым входом - к выходу блока преобразования длительности импульсов в напряжение, отличающийся тем, что, с целью расширения частотного диапазона, в преобразователь импульсов дополнительно введены второй и третий элементы И, подключенные выходами к входам блока преобразования длительности импульсов в напряжение, причем первый вход второго элемента И, подключенного вторым входом к второму выходу второго триггера, соединен с первым выходом третьего триггера, подключенного вторым выходом к первому входу третьего элемента И, второй вход которого соединен с первым выходом второго триггера.

Источники информации, принятые во внимание при экспертизе 1. Куликов С. В. ИмпулБсные измерительные преобразователи. М., «Энергия, 1974, с. 82-84.

№ 515268, кл. И 03 К 5/13, 1975 (прототип).

3

г

rt

1

I

I I

«жЦ О J..™

I

M

Авторы

Даты

1980-07-23—Публикация

1978-06-28—Подача