1

Устройство относится к области приема, передачи и обработки информации и может быть использовано в различных отраслях промь1шленности, где требуется сокращение избыточности информационного массива.

Известно устройство для обработки и сжатия информавди, содержащее регистры текущей выборки и числа, сумматор, оперативную память, буферную память, счетчик ее заполнения, схему сравнения и элементы И, ИЛИ 1.

Недостатком такого устройства является низкое его быстродействие, обусловленное двумя операциями сравнения, охватывающими полную разрядную сетку тел и происходящими в разные промежутки времени.

Наиболее близкнм к изобретению по технической сущности является устройство для сокращения избыточности й} формации, содержащее блок базовых приращений, первый и второй входы которого обьединены с соответствующими входами блока анализа ошибки рассогласования и подключены соответстве1шо к t -му и j -му входам устройства, выход блока базовых приращений соединен с третьим

входом блока анализа ощкбки рассогласования (2.

Недостатком такого устройства является низкое быстродействие- устройства, которое ограничивает его использование для сжатия информации процессов с повьщденной динамикой. Это объясняется тем, что устройство реализует критерий выборки, выполнение которого свя, зано с осуществлением ряда достаточно сложных арифметических операций, таких как

10 операции зМножения.

Цель юобретения - повьппение быстродействия устройства.

Поставленная цель достигается тем, что в устройство введены блок анализа и формиро15вания информации и блок управления приемом приращений, первый и второй входы которого соединены с i -м входом устройства, а третий и четвертый входы подключены к j -му входу устройства, выход блока управления

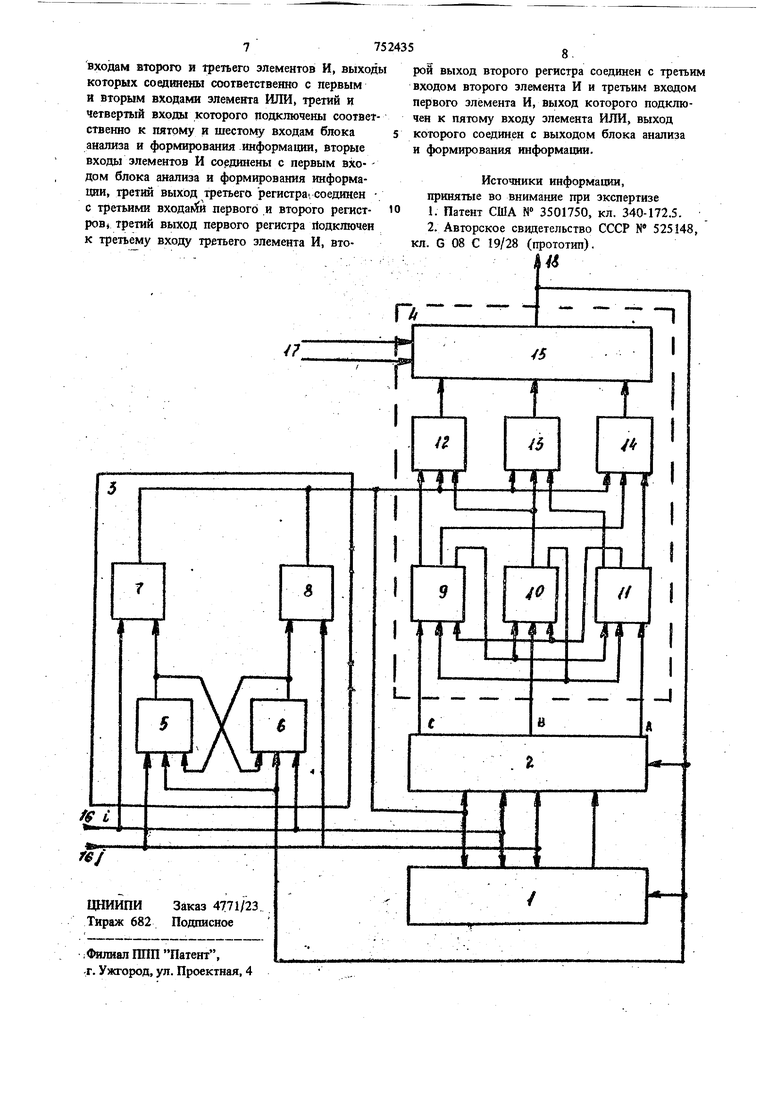

20 приемом 1ф1фащений - соединен с первым входом блока анализа и формирования информации, с третьим входом блока базовых приращений и четвертым входом блока анализа ошибки рассогласования, первый, второй м третий выходы которого подключены соответственно ко второму, третьему и четвертому входам блока анализа и формирования информации, пятый и шестой входы которого подключены ко входам устройства, выход блока анализа и формирования информации соединен с выходом устройства и подключен к пятому входу блока анализа ошибки рассогласования, к четвертому входу блока базовых приращений и к пятому входу блока управления приемом приращений. Блок управления приемом приращений содержит первый и второй элементы И и первый и второй триггеры первые входы которых объединены и подключены к пятому входу блока управления приемом приращений, вторы входы первого и второго триггеров подключены соответственно ко второму и третьему входам блока управления приемом приращений выход первого триггера соединен с первым входом первого элемента И и третьим входом Ьторого триггера, выход которого подключен к третьему входу первого триггера и к первому входу второго элемента И, второй вход которого соединен с первым входом бло ка управления приемом приращений, четвертый вход которого подключен ко второму входу первого элемента И, выход которого объединен с выходом Второго элемента И и соединен с выходом блока управления приемом приращений. Блок анализа и формирования информации содержит элементы И, ИЛИ и первый, второй и третий регистры, первые входы которых подключены соответственно ко второму, третьему и четвертому входам блока, первый и второй выходы первого регистра подключены соответственно к первому входу первого элемента И и ко вторым входам второго и треть го регистров, первый выход второго регистра соединен со вторым входом njepBoro регистра и третьим входом третьего регистра, первый и второй выходы которого подключены соответственно к первым входам второго и третьего элементов И, выходы которых соединень соот ветственно с первым и вторым входами элемента ИЛИ, третий и четвертый входы которого подключены соответственно к пятому и шестому входам блока анализа и формирования информации, вторые входы элементов И соедш1ены с первым входом блока анализа н формирования информации, третий выход Третьего регистра соединен с третьими входами первого и второго регистров, третий выход первого регистра подключен к третьему входу третьего элемента И, второй выхЬд второго регистра соединен с третьим входом второго 4 элемента И и третьим входом первого элемента И, выход которого подключен к пятому входу элемента ИЛИ, выход которого соединен с выходом блока анализа и формирования информации. На чертеже представлена блок-схема уст.ройства для сокращения избыточности информации. Устройство содержит блок 1 базовых приращений, блок 2 рассогласования, блок 3 управления приемом приращений, блок 4 анализа и формирования информации, блок 3 управления приемом содержит два триггера 5 и 6 и два элемента 7 и 8 И. Блок анализа и формирования информации содержит три регистра 9, 10 и 11, три элемента 12, 13 и 14 И и элемент 15 ИЛИ Шины 16 являются входами устройства. Шины 17 на входах блока анализа и формирова™я информации являются знаковыми входами приращений. Шина 18 является выходом устройства. Работа устройства основана на вьшелении базового приращения, под которым понимается .элементарный отрезок, параллельный одной из осей координат и последующем сравнении базового приращения с текущими приращениями, из которых состоит аппроксимируемая прямая. При достижении определенного, наперед заданного рассогласования считывается, что текущее приращение не принадлежит к вычисляемому отрезку прямой. Пусть, например, первые единичные приращения поступают по шине 16 i . Триггер 6 устанавливается в единичное состояние, а в блоке начальных приращений накапливается количество единичных приращений, пришедших по оси t . Единичное приращение по оси j происходит через элемент 8 И и переписывает в блок 2 содержимое блока начальных приращений - величину базового приращения, которое хранится в блоке базовых приращений до тех пор, пока блок 4 не вьщаст сигнала о том, что очередное элементарное приращение выходит за пределы допустимой ошибки. Очередные единичные приращения, поступающие по шине 16 V , вычитаются из содержимого блока анализа ошибки рассогласования. С приходом единичного приращения по оси j сигнал с выхода элемента 8 И поступает на выходы элементов 12, 13 и 14, которые дешифрируют состояние регистров 9, 10 и 11. Первые входы регистров соединены с выходами А, И и С блока рассогласования. Наличие сигнала на выходе 8 говорит о том, что базовое приращение совпало с текущим прира57щением. Наличие сигнала на выходе А или С говорит об отклонении текущего приращения либо в сторону уменьшения, либо в сторону увеличения базового приращения. Блок 4 вырабатывает сигнал о том, что текущее приращение не принадлежит рассматриваемой прямой в соответствии с выражением iF4AAC)v()V(64c)v(l3)v(5j) Это выражение говорит о том, что сигнал формируется тогда, когда отклонения имеются как в ту, так и в другую сторону от базового приращения - выражение (АЛС); два раза подряд было состояние В и затем дважды подряд состояние А или наоборот (ВЛА); дважды подряд было состояние В, затем .дважды состояние С или наоборот - (ВЛс); а также когда было изменение знака единичных приращений по осям t или J (Н« ) Сигнал с выхода блока 4 очищает блок 1 базовых приращений, блок 2, а также сбрасывает в исходное состояние триггеры 5 и 6. Если сигнал на выходе блока 4 не появился то из блока 1 базовых приращений в блок 2 заносится начальное базовое приращение и устройство готово к приему очередных единичных приращений по шинам 16. Если в начале поступают единичные приращения по шине 16, то работа устройства аналогична писанному выше циклу с той лишь разницей, что в блоке управления приемом приращений работает триггер 5 и элемент 7 И Блок 3 реализует логическую операшво в соответствии с выражением tg V | t. Л jg |. Связь с выхода одного триггера на вход другого необходима для запоминания информации о том, по какой из осей t или 3 прищел первый сигнал, другой триггер в этом случае заблокирован до окончания цикла измерений. Быстродействие предлагаемого устройства высокое, задержки на выполнение анализа очередного приращения определяются только логическими злемснтами и не превышает ощ-ю рабочего такта устройства. Формула изобретения 1. Устройство для сокращения избыточности информации, содержащее блок базовых приращений, первый и второй входы которого объединены с соответствующими входами блока анализа ошибки рассогласования и подключены соответственно к i, -му и j -му входам устройства, выход блока базовых при.ращений соединен с третьим входом блока анализа ошибки рассогласования, о. т л и5чающееся тем, что, с целью повышения быстродействия устройства, в него введены блок анализа и формирования информации и блок управления приемом приращений, первый и второй входы которого соединены с -м входом устройства, а третий и четвертый входы подключены к j -му входу устройства, выход блока управления приемом приращений соединен с первым входом блока анализа и формирования информации, с третьим входом блока базовых прирашений и четвертым входом блока анализа ошибки рассогласования, первый, второй н третий выходы которого подключены соответственно ко второму, третьему и четвертому входам блока анализа и формирования информации, пятый и шестой входы которого подключены ко входам устройства, выход блока анализа и формирования информации соединен с выходом устройства и подключен к пятому входу блока анализа ошибки рассогласования, к четвертому входу блока базовых приращений и к пятому входу блока управления приемом приращений. 2.Устройство по п. 1, отличающееся тем, что блок управления приемом приращений содержит первый и второй злементы И и первый и второй тргатеры, первые входы которых объед1{нены и подключены к пятому входу блока управления приемом приращений, вторые входы первого и второго триггеров подключены соответственно ко второму и третьему входам блока управления приемом приращений, выход первого триггера соединен с первым входом первого элемента И и третьим входом второго триггера, выход которого подключен к третьему входу первого триггера и к первому входу второго элемента И, второй вход которого соединен с первым входом блока управления приемом пр1фащений, четвертый вход которого подключен ко второму входу первого злемента И, выход которого объединен с выходом второго элемента И и соединен с выходом блока управления приемом приращений. 3.Устройство по п. 2, отличающееся ТОМ; что блок анализа и формирования информации содержит элементы И, ИЛИ и первый, второй и третий регистры, первые входы которых подключены соответственно ко второму, третьему и четвертому входам блока, первый и второй выходы первого регистра подключены соответственно к первому входу первого злемента И и ко вторым входам второго и третьего регистров, первый выход второго регистра соединен со вторым входом первого регистра и третьим входом третьего регистра, первый и второй выходы koTOOorp подключены соответственно к первым

| название | год | авторы | номер документа |

|---|---|---|---|

| Интерполятор | 1985 |

|

SU1413600A1 |

| ПРИЕМНИК ДИСКРЕТНОЙ ИНФОРМАЦИИ С АВТОМАТИЧЕСКИМ СОГЛАСОВАНИЕМ СКОРОСТЕЙ ПЕРЕДАЧИ И ПРИЕМА | 2003 |

|

RU2249919C2 |

| Устройство для сопряжения | 1979 |

|

SU805295A1 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

| Устройство для декодирования сверточных кодов | 1980 |

|

SU900448A1 |

| Трехканальная резервированная микропроцессорная система | 1985 |

|

SU1378287A1 |

| Цифровой линейный интерполятор | 1988 |

|

SU1624405A2 |

| Система для программного управления | 1985 |

|

SU1325409A1 |

| Устройство для отображения кривых на экране электронно-лучевой трубки | 1988 |

|

SU1547022A1 |

| Устройство для передачи и приема информации | 1982 |

|

SU1104571A1 |

Авторы

Даты

1980-07-30—Публикация

1978-07-20—Подача