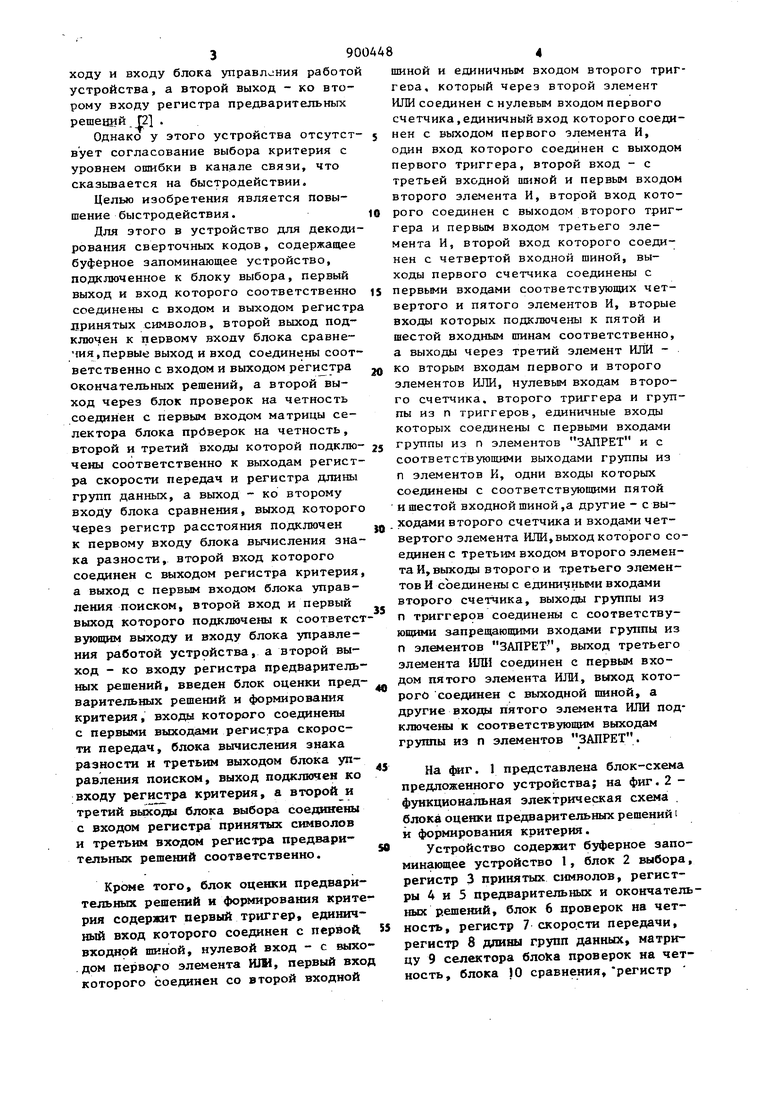

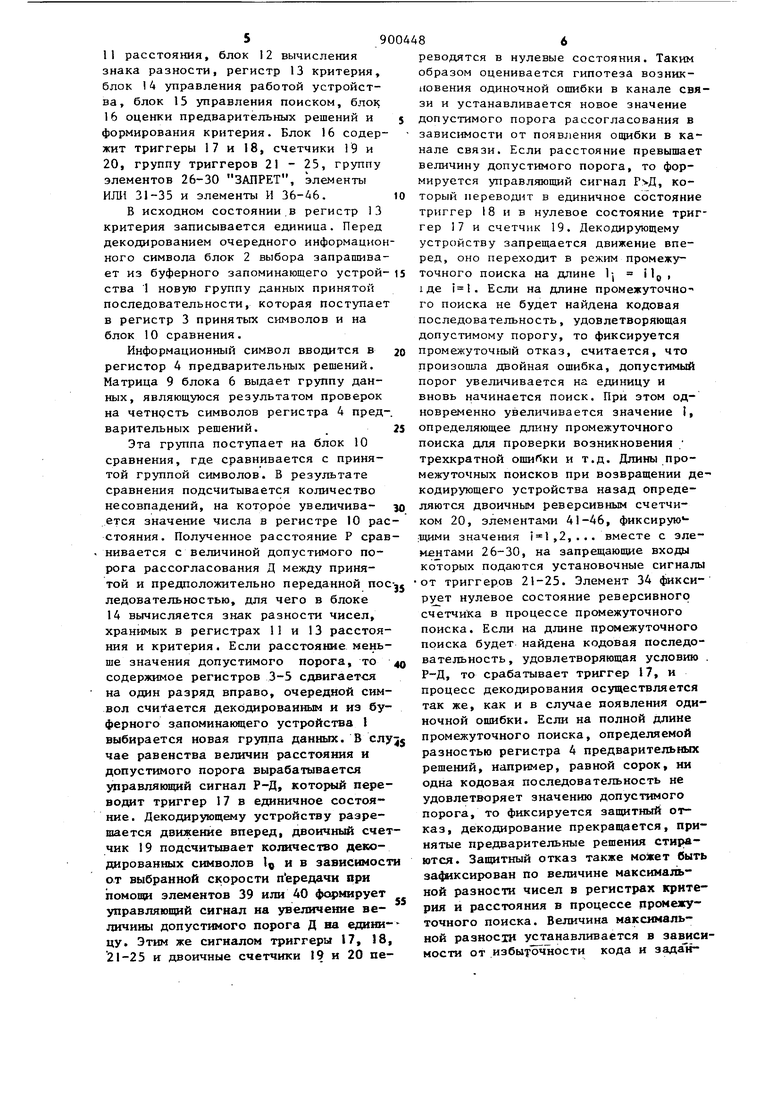

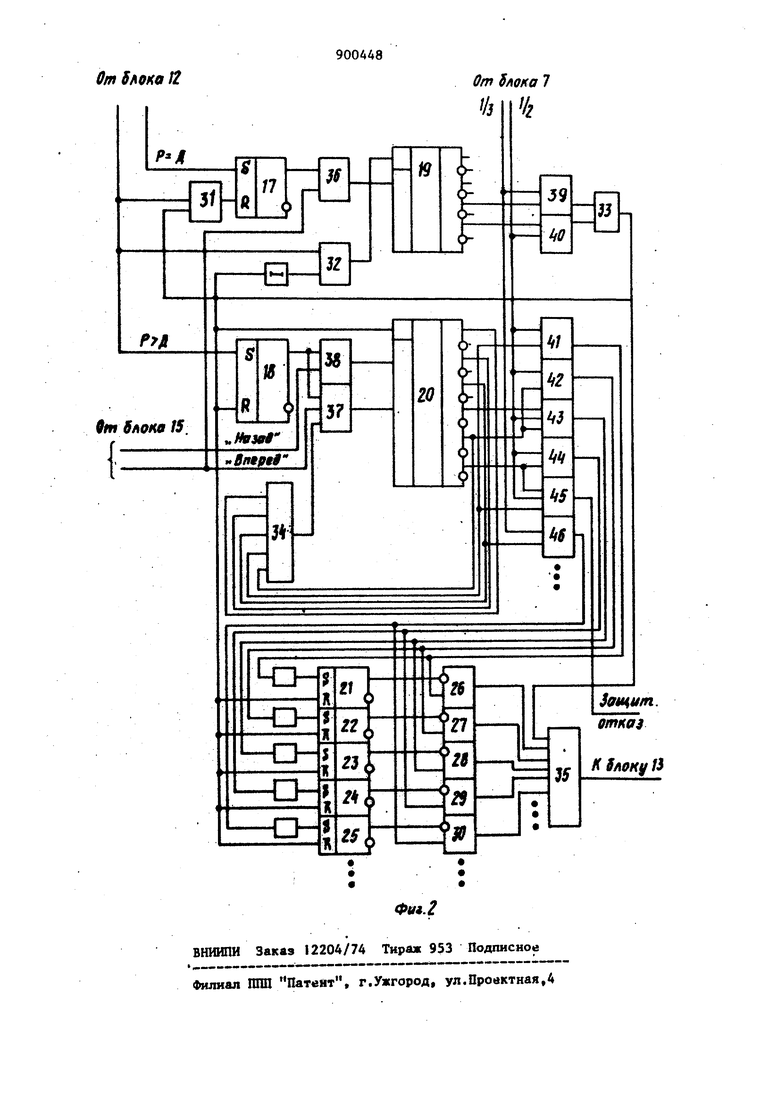

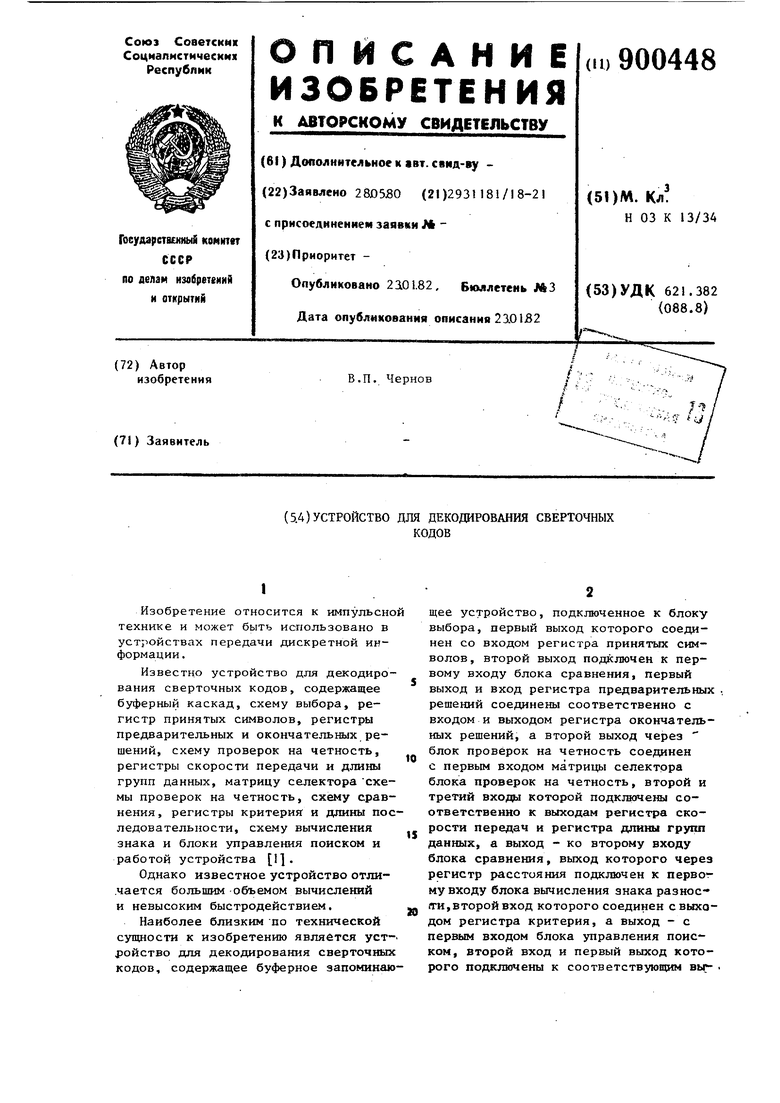

Изобретение относится к импульсно технике и может быть использовано в устройствах передачи дискретной информации. Известно устройство для декодирования сверточных кодов, содержащее буферный каскад, схему выбора, регистр принятых символов, регистр предварительных и окончательных решений, схему проверок на четность, регистры скорости передачи и длины групп данных, матрицу селектора схемы проверок на четность, схему сравнения, регистры критерия и длины пос ледовательности, схему вычисления знака и блоки управления поиском и работой устройства 1. Однако известное устройство отли.чается большим -объемом вычислений и невысоким быстродействием. Наиболее близким по технической сущности к изобретению является устройство для декодирования сверточных кодов, содержащее буферное запоминаю щее устройство, подключенное к блоку выбора, первый выход которого соединен со входом регистра принятых символов, второй выход подключен к первому входу блока сравнения, первый выход и вход регистра предварительных , решений соединены соответственно с входом и выходом регистра окончательных решений, а второй выход через блок проверок на четность соединен с первьм входом матрицы селектора блока проверок на четность, второй и третий входм которой подключены соответственно к выходам регистра скорости передач и регистра длины групп данных, а выход - ко второму входу блока сравнения, выход которого через регистр 1)асстояния подключен к первог му входу блока вычисления знака разнося-и, в торой вход которого соединен с выходом регистра критерия, а выход - с первым входом блока управления поиском, второй вход и первый выход которого подключены к соответствующим вьг- ходу и входу блока управления работо устройства, а второй выход - ко второму входу регистра предварительных решевдй Р . Однако у этого устройства отсутст вует согласование выбора критерия с уровнем ошибки в канале связи, что сказьшается на быстродействии. Целью изобретения является повышение быстродействия . Для этого в устройство для декоди рования сверточных кодов, содержащее буферное запоминающее устройство, подключенное к блоку выбора, первый выход и вход которого соответственно соединены с входом и выходом регистр принятых символов, второй выход подключен к первому входу блока сравнешя,первые выход и вход соединены соответственно с входом и выходом регистра окончательных решений, а второй выход через блок проверок на четность соединен с первым входом матрицы селектора блока проверок на четность, второй и третий входы которой подключены соответственно к выходам регист ра скорости передач и регистра длины групп данных, а выход - ко второму входу блока сравнения, выход которого через регистр расстояния подключен к первому входу блока вычисления зна ка разности, второй вход которого соединен с выходом регистра критерия а выход с первым входом блока управления поиском, второй вход и первый выход которого подключены к соответст вующим выходу и входу блока управления работой устройства, а второй выход - ко входу регистра предварительных решений, введен блок оценки предварительных решений и формирования критерия, входы которого соединены с первыми выходами регистра скорости передач, блока вычисления знака разности и третьим выходом блока управления поиском, выход подклктаен ко входу регистра критерия, а второй и третий выходы блока выбора соедапгены с входом регистра принятых символов и третьим входом регистра предварительных решений соответственно. Крсже того, блок оценки предварительных решений и формирования крите рия содержит первый триггер, единичный вход которого соединен с первой входной шиной, нулевой вход - с выхо . дом первого элемента ШН, первый вхо которого соединен со второй входной шиной и единичным входом второго триггеоа, который через второй элемент ИЛИ соединен с нулевым входом первого счетчика, единичный вход которого соединен с выходом первого элемента И, один вход которого соединен с выходом первого триггера, второй вход - с третьей входной шиной и первым входом второго элемента И, второй вход которого соединен с выходом второго триггера и первым входом третьего элемента И, второй вход которого соединен с четвертой входной шиной, выходы первого счетчика соединены с первыми входами соответствующих четвертого и пятого элементов И, вторые входы которых подключены к пятой и шестой входным пшнам соответственно, а выходы через третий элемент ШМ ко вторым входам первого и второго элементов ИЛИ, нулевым входам второго счетчика, второго триггера и группы из п триггеров, единичные входы которых соединены с первыми входами группы из п элементов ЗАПРЕТ и с соответствующими выходами группы из п элементов И, одни входы которых соединены с соответствующими пятой и шестой входной щиной,а другие - с выходами второго счетчика и входами четвертого элемента ИЛИ, выход которого соединен с третьим входом второго элемента И, выхода второго и третьего элементов И соединены с единичными входами второго счетчика, выходы группы из л триггеров соединены с соответствующими запрещающими входами группы из п эл 1еитов ЗАПРЕТ, выход третьего элемента ИЛИ соединен с первым входом пятого элемента ИЛИ, выход которого соедииен с выходной шиной, а другие входал пятого элемента ИЛИ подключены к соответствующим выходам группы из п элементов ЗАПРЕТ. На 4иг. 1 представлена блок-схема предложенного устройства; на фиг.2 функциональная электрическая схема . блока оценки предварительных решений i и формирования критерия. Устройство содержит буферное запоминакицее устройство 1, блок 2 выбора, регистр 3 принятых символов, регистры 4 и 5 предварительных и окончательных решений, блок 6 проверок на четность, регистр 7 скорости передачи, регистр 8 длины групп данных, матрицу 9 селектора блока проверок на четность, блока |0 сравнения,регистр 11 расстояния, блок 12 вычисления знака разности, регистр 13 критерия, блок 14 управления работой устройства, блок 15 управления поиском, блок 16 оценки предварительных решений и формирования критерия. Блок 16 содержит триггеры 17 и 18, счетчики 19 и 20, группу триггеров 21 - 25, группу элементов 26-30 ЗАПРЕТ, элементы ИШ1 31-35 и элементы И 36-46. В исходном состоянии,в регистр 13 критерия записывается единица. Перед декодированием очередного информацион ного символа блок 2 выбора запрашивает из буферного запоминающего устройства 1 новую группу данных принятой последовательности, которая поступает в регистр 3 принятых символов и на блок 10 сравнения. Информационный символ вводится в регистор 4 предварительных решений. Матрица 9 блока 6 выдает группу данных, являющуюся результатом проверок на четнрсть символов регистра 4 предварительных решений. Эта группа поступает на блок 10 сравнения, где сравнивается с принятой группой символов. В результате сравнения подсчитывается количество несовпадений, на которое увеличивается значение числа в регистре 10 рас стояния. Полученное расстояние Р срав нивается с величиной допустимого порога рассогласования Д между принятой и предположительно переданной noc ледовательностью, для чего в блоке 14 вычисляется знак разности чисел, хранимых в регистрах 11 и 13 расстояния и критерия. Если расстояние меньше значения допустимого порога, то содержимое регистров 3-5 сдвигаето на один разряд вправо, очередной символ c4HtaeTCH декодированным и из буферного запоминающего устройства 1 выбирается новая группа данных. В cny чае равенства величин расстояния и допустимого порога вырабатывается управляющий сигнал Р-Д, который переводит триггер 17 в единичное состояние. Декодирующему устройству разрешается движение вперед, двоичный счет чик 19 подсчитывает количество декодированных символов Ц и в зависимоста от выбранной скорости передачи при помощи элементов 39 или 40 фо4 мирует управляющий сигнал на увеличение величины допустимого порога Д на еднницу. Этим же сигналом триггеры 17, 18, 21-25 к двоичные счетчики 19 и 20 переводятся в нулевые состояния. Таким образом оценивается гипотеза возник1{овения одиночной опшбки в канале связи и устанавливается новое значение допустимого порога рассогласования в зависимости от появления ощибки в канале связи. Если расстояние превышает величину допустимого порога, то формируется управляющий сигнал , который переводит в единичное состояние триггер 18 и в нулевое состояние триггер 17 и счетчик 19. Декодирующему устройству запрещается движение вперед, оно переходит в режим промежуточного поиска на длине 1-| Q , 1 де . Если на длине промежуточно- го поиска не будет найдена кодовая последовательность, удовлетворяющая допустимому порогу, то фиксируется промежуточный отказ, считается, что произошла двойная ошибка, допустимый порог увеличивается на единицу и вновь начинается поиск. При этом одновременно увеличивается значение I, определяющее длину промежуточного поиска для проверки возникновения трехкратной ошибки и т.д. Длины промежуточных поисков при возвращении декодирующего устройства назад определяются двоичным реверсивным счетчиком 20, элементами 41-46, фиксирую тцими значения i l ,2,... вместе с элем нтами 26-30, на запрещаюоще входы которых подаются установочные сигналы от триггеров 21-25. Элемент 34 фиксирует нулевое состояние реверсивного счетчика в процессе промежуточного поиска. Если на длине промежуточного поиска будет найдена кодовая последовательность , удовлетворяющая условию . Р-Д, то срабатывает триггер 17, и процесс декодирования осуществляется так же, как и в случае появления одиночной ошибки. Если на полной длине промежуточного поиска, определяемой разностью регистра 4 предварительных решений, например, равной сорок, ни одна кодовая последовательность не удовлетворяет значению допустимого порога, то фиксируется защитный отказ, декодирование прекращается, принятые предварительные решения стираются. Защитный отказ также может быть зафиксирован по величине максимальной разности чисел в регистрах критерия и расстояния в процессе промежуточного поиска. Величина максимальной разности устанавливается в зависимости от избыточности кода и заданной вероятности noHBnteHHH необнаруживаемых ощибок. Уменьшение значений чисел, накопленных в регистрах расстояния и критерия, в процессе длительной работы декодирующего устройства может осуществляться различными способами. При этом важно поддерживать разность между ними, равную единице. Таким образом, в предложенном уст ройстве при достаточно высоком быстродействии осуществляется надежная работа. Формула изобретения 1. Устройство для декодирования сверточных кодов, содержащее буферное запоминающее устройство, подключенное к блоку выбора, первые выход и вход которого соединен соответственно с входом и выходом регистра принятых символов, второй выход подключен к первому входу блока сравнения, а третий выход соединен со вторым входом регистра предварительных рещений,первый выход и вход которого соединены соответственно с входом и выходом регистра окончательных рещений,а второй выход через блок проверок на четность соединен с первым входом матри цы селектора блока проверок на четность, второй и третий входы которой подключены соотиетственно к выходам регистра скорости передач и регистра длины групп данных, а выход - ко вто рому входу блока сравнения, выход ко торого через регистр расстояния под ключен к первому входу блока вычисления знака разности, второй вход ко торого соединен с выходом регистра критерия, а выход с первым входом бл ка управления поиском, второй вход и первый 1.ыход которого подключен к соответствующим выходу и входу блока управления работой устройства, а второй выход- к третьему входу регист ра передварительных решений,о т л и ч а ющее с я тем,что,с целью повышения быстродействия, введен блок оценки предварительных решений и формированря критерия,, входы которого соедине с первыми выходами регистра скорости пе редач,блока вычисления знака разности третьим выходом блока упр/1вления пои ком, а выход подключен к6 входу реги стра критерия. 2.Устройство по п. 1, о т л и чающееся тем, что блох оценки предварительных решений н фо ммирования критерия содержит первый триггер 8 единичный вход которого соединен с первой входной шиной, нулевой входс выходом первого элемента ИЛИ, первый вход 1 оторого соединен со второй шино.й и единичным входом второго триггера, который через второй входной элемент ИЛИ соединен с нулевьи входом первого счетчика, единичный вход которого соединен с выходом первого элемента И, один вход которого соединен с выходом первого триггера,второй вход - с третьей входной шиной и первым входом второго элемента И, второй вход которого соединен с выходом второго триггера и первым входом третьего элемента И, второй вход которого соединен с четвертой входной шиной, выходы первого счетчика соединены с первыми входами соответствующих четвертого и пятого элементов И, вторые входы которых Подключены к пятой и шестой входным шинам, соответственно, а выходы через третий элемент ИЛИ ко Вторым входам первого и второго элементов ИЛИ, нулевым входам второго счетчика, второго триггера и группы из п триггеров, единичные входы которых соединены с первыми входами группы из п элементов ЗАПРЕТ и с соответствующими выходами группы из п элементов И, один входы которых соединены с соответствующими пятой и шестой входной шиной, а другие с выходами второго, счетчика и входами четвертого элемента ИЛИ, выход которого со динен с третьим входом второго эл.емента И, выходы второго и третьего элементов И соединены с единичньми входами второго счетчика, ВЫХОДА группы из п триггеров -соединены .с. соответствующими запрещающими входами группы из п элементов ЗАПРЕТ, выход третьего элемента ИЛИ соединен с первым входом пятого элемента ИШ, выход которого соединен с выходной щиной, а другие входы пятого элемента ИЛИ подключены к соответствуюпщм выходам группы из п элементов ЗАПРЕТ. Источники информации, ринятые во внимание при экспертизе 1.Возенкрафт Дж., Рейффен Б., оследовательное декодирование. М., Л, 1963. 2.Авторское свидетельство СССР 222733, кл. Н 03К 13/24, 1968 прототип).

От SAOKO J2

От $лока 7

Ч) Чг

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ СВЕРТОЧНЫХ КОДОВ | 1967 |

|

SU222733A1 |

| УСТРОЙСТВО ДЛЯ ПОРОГОВОГО ДЕКОДИРОВАНИЯ СВЕРТОЧНЫХ КОДОВ | 1993 |

|

RU2081513C1 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ СВЕРТОЧНЫХ КОДОВ | 1971 |

|

SU297040A1 |

| Декодер мажоритарного двоичного кода | 1988 |

|

SU1566488A1 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ СВЕРТОЧНОГО КОДА | 1991 |

|

RU2015621C1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ LDPC-КОДОВ | 2013 |

|

RU2549134C1 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ ДВОИЧНЫХ КОДОВ ХЕММИНГА | 1999 |

|

RU2161369C1 |

| Пороговый декодер @ -ичного кода | 1989 |

|

SU1642589A1 |

| ДЕКОДЕР СВЕРТОЧНОГО КОДА | 1992 |

|

RU2085035C1 |

| Устройство цикловой синхронизации | 1984 |

|

SU1197122A1 |

Авторы

Даты

1982-01-23—Публикация

1980-05-28—Подача