Изобретение относится к цифровой вычислительной технике и может быть использовано в качестве устройства для контроля многоканальных импульсных последовательностей в системах с трехканальным резервированием повышенной надежности, например в электронных цифровых вычислительных машинах.

Известно устройство для контроля многоканальных импульсных последовательностей, содержащее одновибратор, частотомер, счетчик и мультиплексор.

Недостатком известного устройства является прекращение опроса каналов при пропадании сигналов в одном из каналов контролируемой импульсной последовательности. Кроме того, известное устройство не обеспечивает измерение периода следования одиночных импульсов или же пачки импульсов,

Наиболее близким к предлагаемому по технической сущности и достигаемому результату является устройство для контроля многоканальных импульсных последовательностей, которое содержит счетчик импульсов, демультиплексор, мультиплексор, управляемый блок задержки, триггер, два элемента ИЛИ и одновибратор. Недостатком известного устройства является низкая точность измерений периодов контролируемых импульсных последовательностей. Это обусловлено точностью работы управляемого блока задержки, который допускает погрешность 5-10% при измерении интервалов.

Цель изобретения - повышение точности функционирования устройства за счет селектирования сигналов по периоду их следования.

Предлагаемое устройство для контроля многоканальных импульсных последовательностей, содержащее первый канал, также содержит первый триггер синхронизации, счетчик числа контролируемых импульсов, элемент ИЛИ и мультиплексор, группа информационных входов которого является группой сигнальных входов канала.

В предлагаемое устройство введены два канала, идентичные первому, причем в каждый канал дополнительно введены второй и третий триггеры синхронизации, элемент НЕ, мажоритарный элемент, блок измерения частоты и регистр хранения кода режима, группа информационных входов которого соединена с первой группой информационных входов канала. Вторая груп- па информационных входов канала подключена к группе установочных входов счетчика числа контролируемых импульсов, а третья группа соединена с группой установочных входов блока измерения частоты, группа выходов которого является группой информационных выходов канала, вход запуска канала подключен к входу управления записью счетчика числа контролируемых импульсов, установочному входу второго триггера синхронизации, входу начальной установки блока измерения частоты, прямому входу элемента ИЛИ и синхровходу регистра хранения кода режима, выходы соответствующих разрядов которого соединены с адресными входами мультиплексо- ра, первый информационный вход мультиплексора соединен с шиной логического нуля, а выход мультиплексора подключен к входу элемента НЕ и синхровходу первого триггера синхронизации, информа- ционный вход которого соединен с выходом старшего разряда регистра хранения кода режима, а установочный вход подключен к выходу элемента ИЛИ, инверсный выход первого триггера синхронизации соединен с первым выходом сигналов синхронизации канала и первым входом мажоритарного элемента, второй и третий входы которого подключены к первому и второму синхров- ходам канала, а выход мажоритарного эле- мента соединен с установочным входом третьего триггера синхронизации и входом управления счетчика числа контролируемых импульсов, счетный вход которого подсоединен к выходу элемента НЕ, инверсный

выход сигнала переполнения счетчика подсоединен к информационному входу третьего триггера синхронизации, синхровход которого подключен к выходу элемента НЕ, прямой выход подключен к первому входу блокировки блока измерения частоты и второму выходу сигналов синхронизации канала, а инверсный выход - к синхровходу второго триггера синхронизации, информационный вход которого соединен с шиной логической единицы, а инверсный выход - с инверсным входом элемента ИЛИ, третий и четвертый синхровходы канала соединены с вторым и третьим входами блока измерения частоты, первая - третья группы информационных входов и группа информационных выходов каждого из каналов соединены с соответствующими группами информационных входов и выходов устройства. Группа сигнальных входов каждого из каналов подключена к соответствующей группе сигнальных входов устройства. Вход запуска устройства соединен с входами запуска каждого из каналов, первый выход сигнала синхронизации первого канала подключен к первым синхровходам второго и третьего каналов, второй выход сигнала синхронизации первого канала соединен с четвертым синхровходом второго канала и третьим синхровходом третьего канала, первый выход сигнала синхронизации второго канала соединен с первым синхровходом первого канала и с вторым синхровходом третьего канала. Второй выход сигнала синхронизации второго канала соединен с четвертым синхровходом первого и третьего каналов, первый выход сигнала синхронизации третьего канала соединен с вторыми синх- ровходами первого и второго каналов, второй выход сигнала синхронизации третьего канала соединен с третьими синхровходами первого и второго каналов.

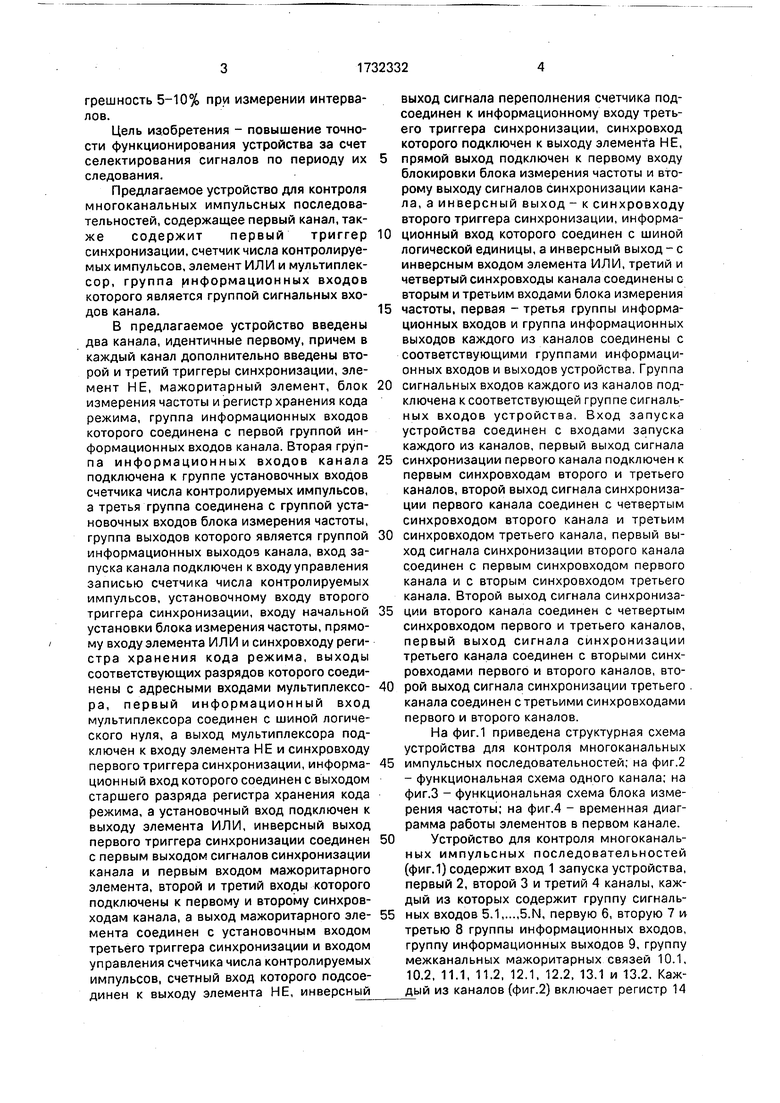

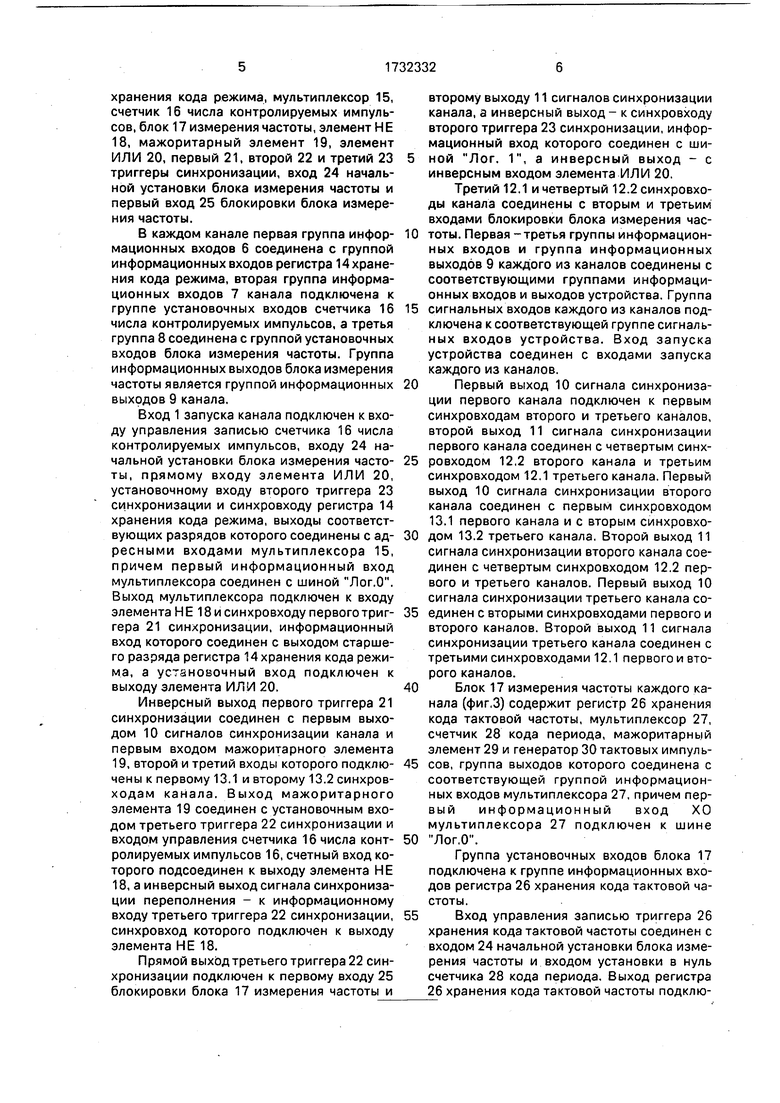

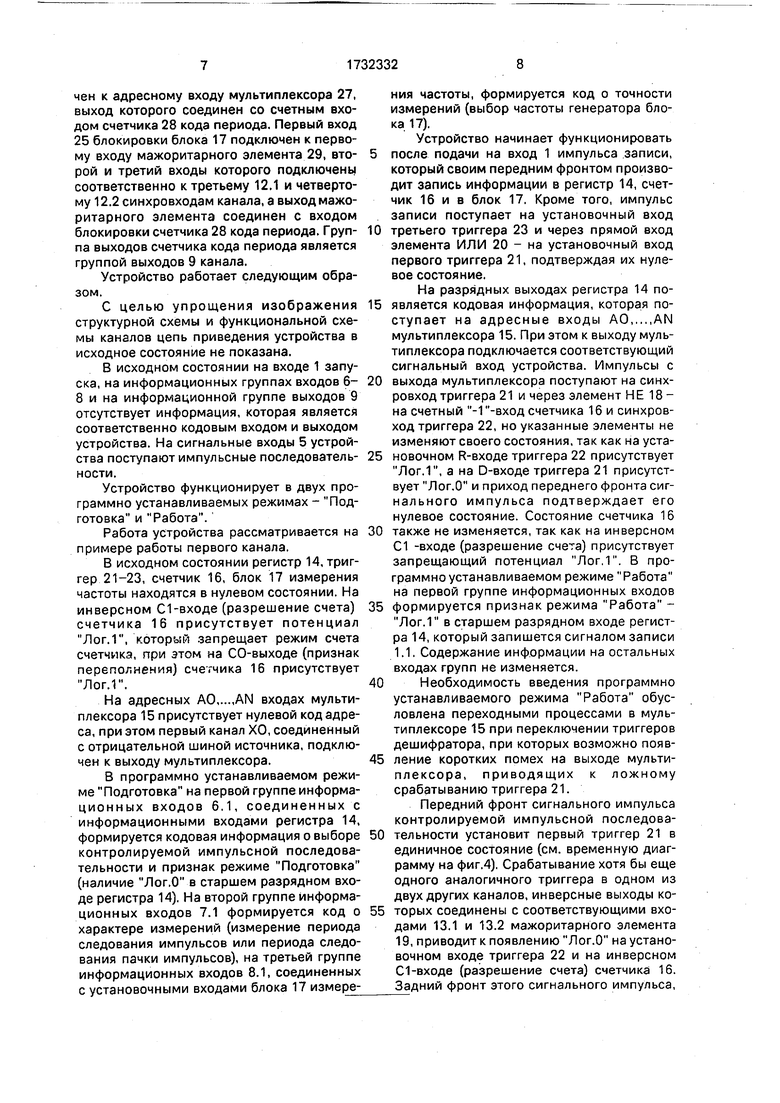

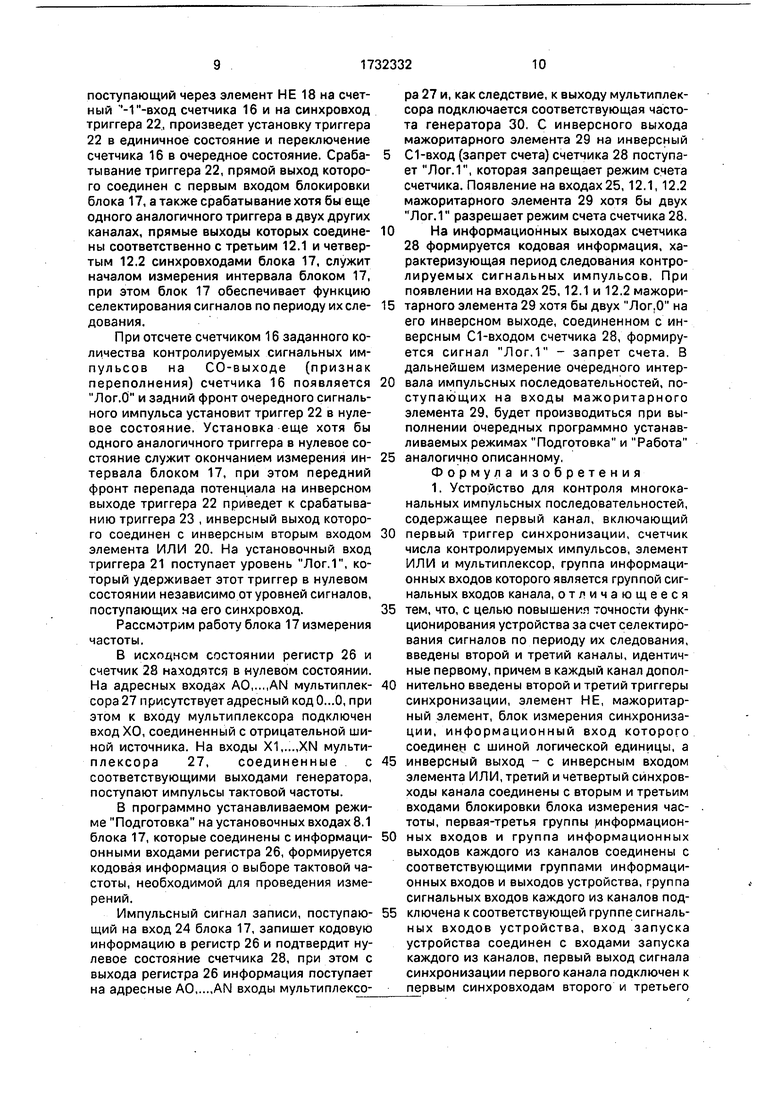

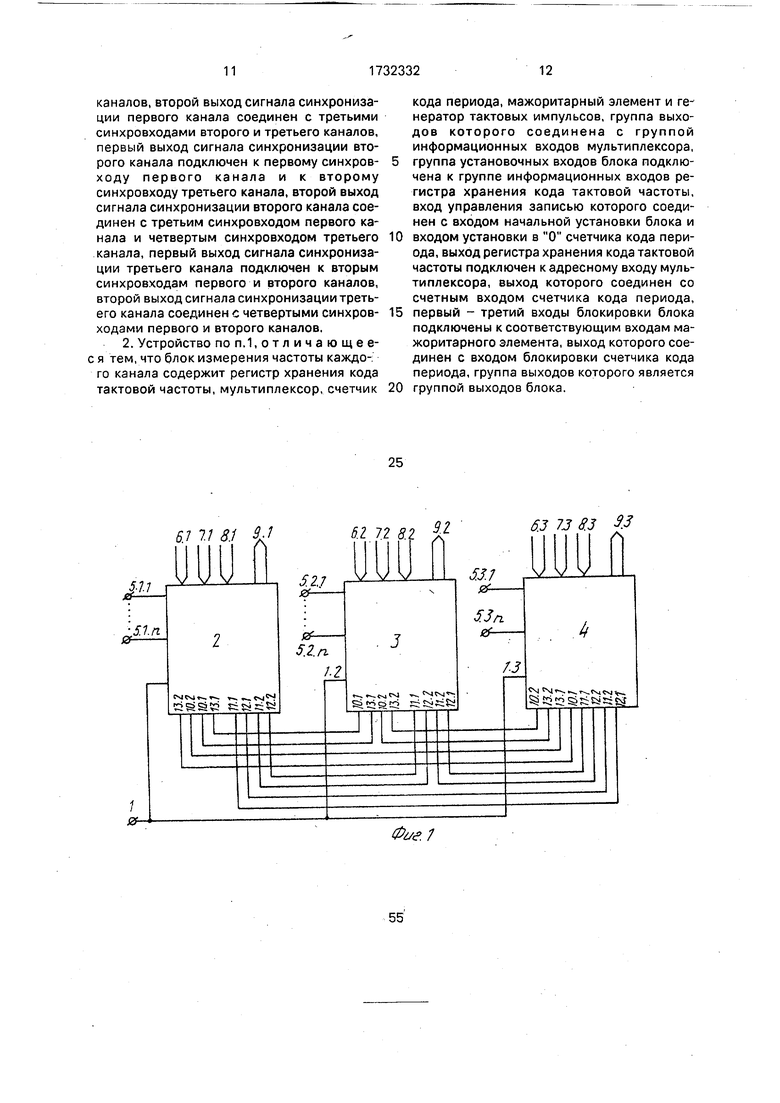

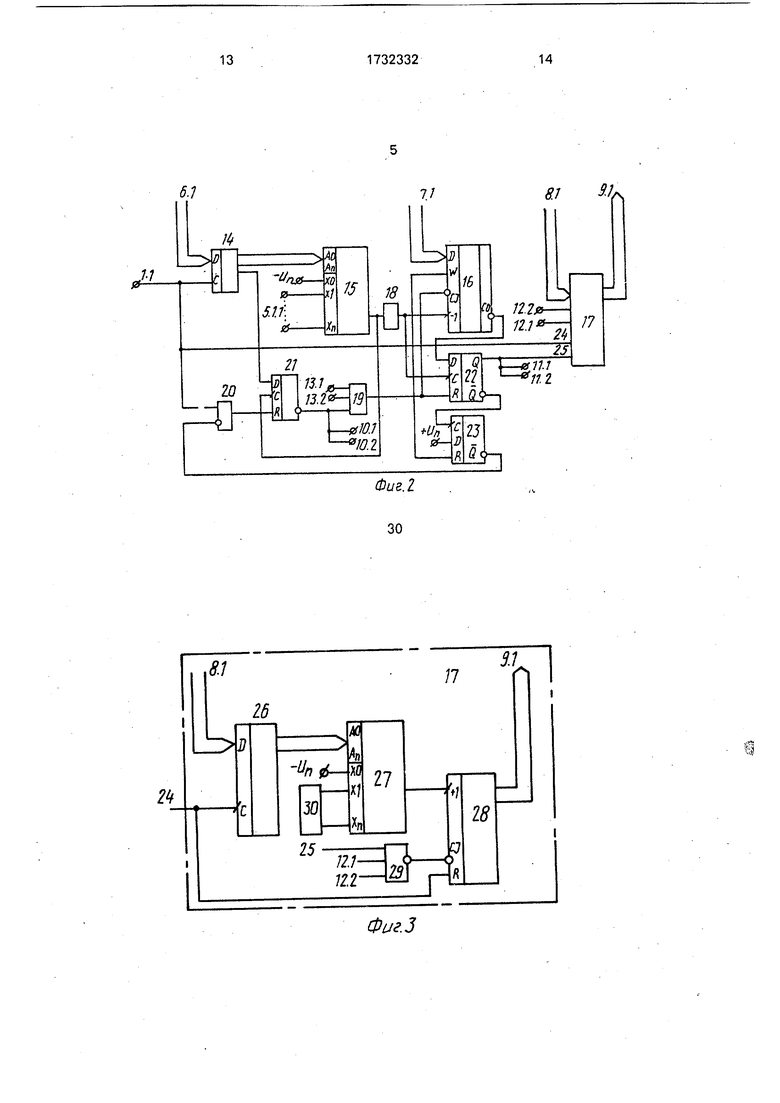

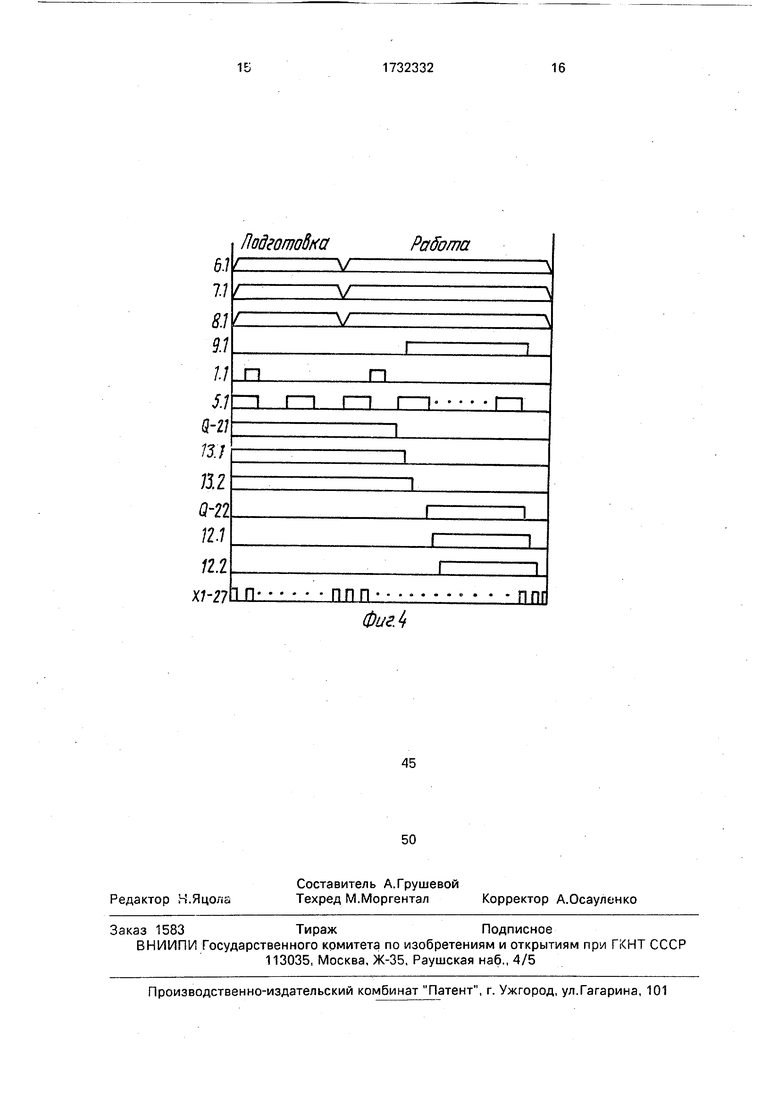

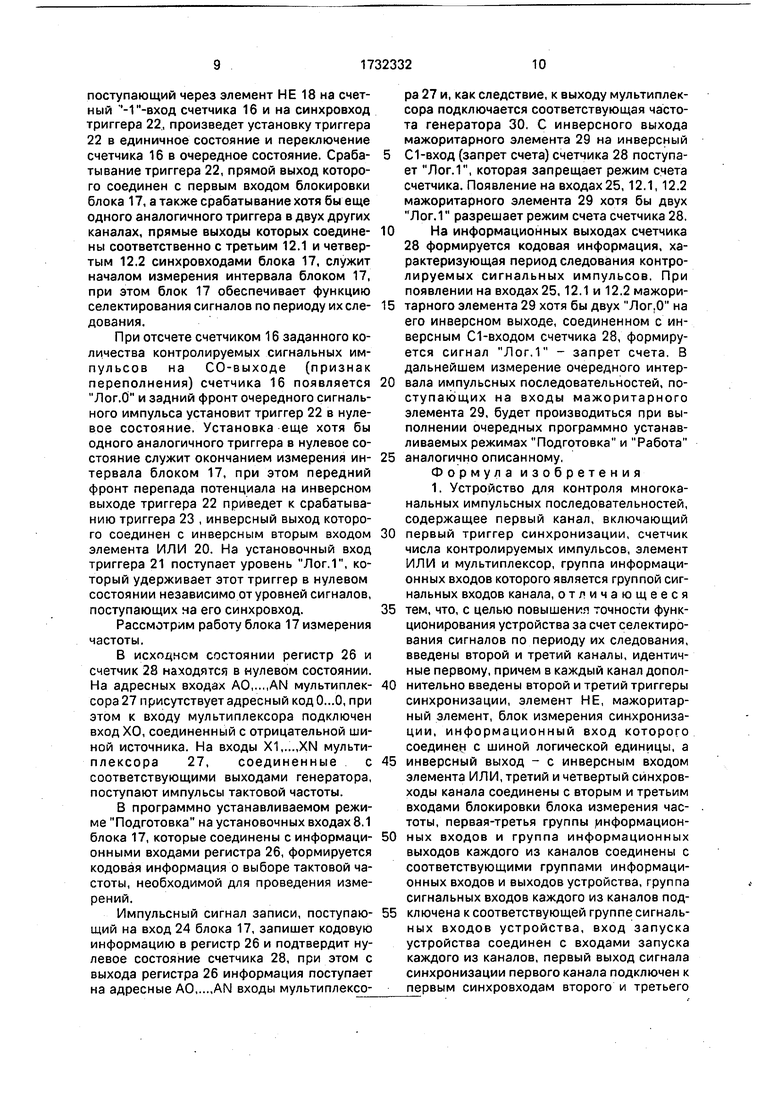

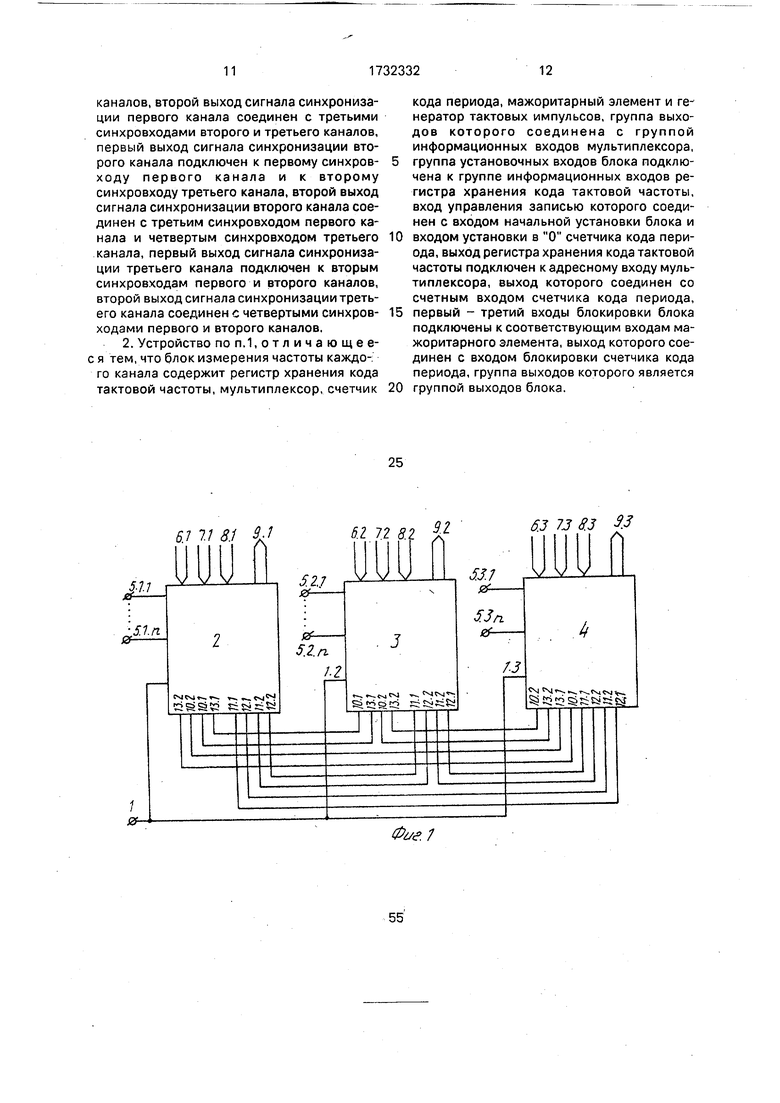

На фиг.1 приведена структурная схема устройства для контроля многоканальных импульсных последовательностей; на фиг.2 - функциональная схема одного канала; на фиг.З - функциональная схема блока измерения частоты; на фиг.4 - временная диаграмма работы элементов в первом канале.

Устройство для контроля многоканальных импульсных последовательностей (фиг.1) содержит вход 1 запуска устройства, первый 2, второй 3 и третий 4 каналы, каждый из которых содержит группу сигнальных входов 5.1,...,5.N, первую 6, вторую 7 и третью 8 группы информационных входов, группу информационных выходов 9, группу межканальных мажоритарных связей 10.1, 10.2, 11.1, 11.2, 12.1, 12.2, 13.1 и 13.2. Каждый из каналов (фиг.2) включает регистр 14

хранения кода режима, мультиплексор 15, счетчик 16 числа контролируемых импульсов, блок 17 измерения частоты, элемент НЕ

18,мажоритарный элемент 19, элемент ИЛИ 20, первый 21, второй 22 и третий 23 триггеры синхронизации, вход 24 начальной установки блока измерения частоты и первый вход 25 блокировки блока измерения частоты.

В каждом канале первая группа информационных входов 6 соединена с группой информационных входов регистра 14 хранения кода режима, вторая группа информационных входов 7 канала подключена к группе установочных входов счетчика 16 числа контролируемых импульсов, а третья группа 8 соединена с группой установочных входов блока измерения частоты. Группа информационных выходов блока измерения частоты является группой информационных выходов 9 канала.

Вход 1 запуска канала подключен к входу управления записью счетчика 16 числа контролируемых импульсов, входу 24 начальной установки блока измерения частоты, прямому входу элемента ИЛИ 20, установочному входу второго триггера 23 синхронизации и синхровходу регистра 14 хранения кода режима, выходы соответствующих разрядов которого соединены с адресными входами мультиплексора 15, причем первый информационный вход мультиплексора соединен с шиной Лог.О. Выход мультиплексора подключен к входу элемента Н Е 18 и синхровходу первого триггера 21 синхронизации, информационный вход которого соединен с выходом старшего разряда регистра 14 хранения кода режима, а установочный вход подключен к выходу элемента ИЛИ 20.

Инверсный выход первого триггера 21 синхронизации соединен с первым выходом 10 сигналов синхронизации канала и первым входом мажоритарного элемента

19,второй и третий входы которого подключены к первому 13.1 и второму 13.2 синхров- ходам канала. Выход мажоритарного элемента 19 соединен с установочным входом третьего триггера 22 синхронизации и входом управления счетчика 16 числа контролируемых импульсов 16, счетный вход которого подсоединен к выходу элемента НЕ 18, а инверсный выход сигнала синхронизации переполнения - к информационному входу третьего триггера 22 синхронизации, синхровход которого подключен к выходу элемента НЕ 18.

Прямой выход третьего триггера 22 синхронизации подключен к первому входу 25 блокировки блока 17 измерения частоты и

второму выходу 11 сигналов синхронизации канала, а инверсный выход- к синхровходу второго триггера 23 синхронизации, информационный вход которого соединен с шиной Лог. 1, а инверсный выход - с инверсным входом элемента ИЛИ 20.

Третий 12.1 и четвертый 12.2синхровхо- ды канала соединены с вторым и третьим входами блокировки блока измерения час0 тоты. Первая -третья группы информационных входов и группа информационных выходов 9 каждого из каналов соединены с соответствующими группами информационных входов и выходов устройства. Группа

5 сигнальных входов каждого из каналов подключена к соответствующей группе сигналь- ных входов устройства. Вход запуска устройства соединен с входами запуска каждого из каналов.

0 Первый выход 10 сигнала синхронизации первого канала подключен к первым синхровходам второго и третьего каналов, второй выход 11 сигнала синхронизации первого канала соединен с четвертым синх5 ровходом 12,2 второго канала и третьим синхровходом 12.1 третьего канала. Первый выход 10 сигнала синхронизации второго канала соединен с первым синхровходом 13.1 первого канала и с вторым синхровхо0 дом 13.2 третьего канала. Второй выход 11 сигнала синхронизации второго канала соединен с четвертым синхровходом 12.2 первого и третьего каналов. Первый выход 10 сигнала синхронизации третьего канала со5 единен с вторыми синхровходами первого и второго каналов. Второй выход 11 сигнала синхронизации третьего канала соединен с третьими синхровходами 12.1 первого и второго каналов.

0 Блок 17 измерения частоты каждого канала (фиг.З) содержит регистр 26 хранения кода тактовой частоты, мультиплексор 27, счетчик 28 кода периода, мажоритарный элемент 29 и генератор 30 тактовых импуль5 сов, группа выходов которого соединена с соответствующей группой информационных входов мультиплексора 27, причем пер- вый информационный вход ХО мультиплексора 27 подключен к шине

0 Лог.О.

Группа установочных входов блока 17 подключена к группе информационных входов регистра 26 хранения кода тактовой частоты.

5 Вход управления записью триггера 26 хранения кода тактовой частоты соединен с входом 24 начальной установки блока измерения частоты и входом установки в нуль счетчика 28 кода периода. Выход регистра 26 хранения кода тактовой частоты подключен к адресному входу мультиплексора 27, выход которого соединен со счетным входом счетчика 28 кода периода. Первый вход 25 блокировки блока 17 подключен к первому входу мажоритарного элемента 29, второй и третий входы которого подключены соответственно к третьему 12.1 и четвертому 12.2 синхровходам канала, а выход мажоритарного элемента соединен с входом блокировки счетчика 28 кода периода. Группа выходов счетчика кода периода является группой выходов 9 канала.

Устройство работает следующим образом.

С целью упрощения изображения структурной схемы и функциональной схемы каналов цепь приведения устройства в исходное состояние не показана.

В исходном состоянии на входе 1 запуска, на информационных группах входов 6- 8 и на информационной группе выходов 9 отсутствует информация, которая является соответственно кодовым входом и выходом устройства. На сигнальные входы 5 устройства поступают импульсные последовательности.

Устройство функционирует в двух программно устанавливаемых режимах - Подготовка и Работа.

Работа устройства рассматривается на примере работы первого канала,

В исходном состоянии регистр 14, триггер 21-23, счетчик 16, блок 17 измерения частоты находятся в нулевом состоянии. На инверсном С1-входе (разрешение счета) счетчика 16 присутствует потенциал Лог.1, который запрещает режим счета счетчика, при этом на СО-выходе (признак переполнения) счетчика 16 присутствует Лог.1.

На адресных АОAN входах мультиплексора 15 присутствует нулевой код адреса, при этом первый канал ХО, соединенный с отрицательной шиной источника, подключен к выходу мультиплексора.

В программно устанавливаемом режиме Подготовка на первой группе информа- ционных входов 6.1, соединенных с информационными входами регистра 14, формируется кодовая информация о выборе контролируемой импульсной последовательности и признак режиме Подготовка (наличие Лог.О в старшем разрядном входе регистра 14). На второй группе информационных входов 7.1 формируется код о характере измерений (измерение периода следования импульсов или периода следования пачки импульсов), на третьей группе информационных входов 8.1, соединенных с установочными входами блока 17 измерения частоты, формируется код о точности измерений (выбор частоты генератора блока 17).

Устройство начинает функционировать

после подачи на вход 1 импульса записи, который своим передним фронтом производит запись информации в регистр 14, счетчик 16 и в блок 17. Кроме того, импульс записи поступает на установочный вход

0 третьего триггера 23 и через прямой вход элемента ИЛИ 20 - на установочный вход первого триггера 21, подтверждая их нулевое состояние.

На разрядных выходах регистра 14 по5 является кодовая информация, которая поступает на адресные входы АОAN

мультиплексора 15. При этом к выходу мультиплексора подключается соответствующий сигнальный вход устройства. Импульсы с

0 выхода мультиплексора поступают на синх- ровход триггера 21 и через элемент НЕ 18- на счетный -1 -вход счетчика 16 и синхров- ход триггера 22, но указанные элементы не изменяют своего состояния, так как на уста5 новочном R-входе триггера 22 присутствует Лог.1, а на D-входе триггера 21 присутствует Лог.О и приход переднего фронта сиг- нального импульса подтверждает его нулевое состояние. Состояние счетчика 16

0 также не изменяется, так как на инверсном С1 -входе (разрешение счета) присутствует запрещающий потенциал Лог.1. В программно устанавливаемом режиме Работа на первой группе информационных входов

5 формируется признак режима Работа - Лог.1 в старшем разрядном входе регистра 14, который запишется сигналом записи 1.1. Содержание информации на остальных входах групп не изменяется.

0 Необходимость введения программно устанавливаемого режима Работа обусловлена переходными процессами в мультиплексоре 15 при переключении триггеров дешифратора, при которых возможно появ5 ление коротких помех на выходе мультиплексора, приводящих к ложному срабатыванию триггера 21.

Передний фронт сигнального импульса контролируемой импульсной последова0 тельности установит первый триггер 21 в единичное состояние (см. временную диаграмму на фиг.4). Срабатывание хотя бы еще одного аналогичного триггера в одном из двух других каналов, инверсные выходы ко5 торых соединены с соответствующими входами 13.1 и 13.2 мажоритарного элемента 19, приводит к появлению Лог.О на установочном входе триггера 22 и на инверсном С1-входе (разрешение счета) счетчика 16. Задний фронт этого сигнального импульса,

поступающий через элемент НЕ 18 на счетный - -1 -вход счетчика 16 и на синхровход триггера 22, произведет установку триггера 22 в единичное состояние и переключение счетчика 16 в очередное состояние. Срабатывание триггера 22, прямой выход которого соединен с первым входом блокировки блока 17, а также срабатывание хотя бы еще одного аналогичного триггера в двух других каналах, прямые выходы которых соединены соответственно с третьим 12.1 и четвертым 12.2 синхровходами блока 17, служит началом измерения интервала блоком 17, при этом блок 17 обеспечивает функцию селектирования сигналов по периоду их следования.

При отсчете счетчиком 16 заданного количества контролируемых сигнальных импульсов на СО-выходе (признак переполнения) счетчика 16 появляется Лог.О и задний фронт очередного сигнального импульса установит триггер 22 в нулевое состояние. Установка еще хотя бы одного аналогичного триггера в нулевое состояние служит окончанием измерения интервала блоком 17, при этом передний фронт перепада потенциала на инверсном выходе триггера 22 приведет к срабатыванию триггера 23 , инверсный выход которого соединен с инверсным вторым входом элемента ИЛИ 20. На установочный вход триггера 21 поступает уровень Лог.1, который удерживает этот триггер в нулевом состоянии независимо от уровней сигналов, поступающих на его синхровход.

Рассмотрим работу блока 17 измерения частоты.

В исходном состоянии регистр 26 и счетчик 28 находятся в нулевом состоянии. На адресных входах АОAN мультиплексора 27 присутствует адресный код 0...0, при этом к входу мультиплексора подключен вход ХО, соединенный с отрицательной шиной источника. На входы X1,...,XN мультиплексора 27, соединенные с соответствующими выходами генератора, поступают импульсы тактовой частоты.

В программно устанавливаемом режиме Подготовка на установочных входах 8.1 блока 17, которые соединены с информационными входами регистра 26, формируется кодовая информация о выборе тактовой частоты, необходимой для проведения измерений.

Импульсный сигнал записи, поступающий на вход 24 блока 17, запишет кодовую информацию в регистр 26 и подтвердит нулевое состояние счетчика 28, при этом с выхода регистра 26 информация поступает на адресные АОAN входы мультиплексора 27 и, как следствие, к выходу мультиплексора подключается соответствующая частота генератора 30. С инверсного выхода мажоритарного элемента 29 на инверсный

С1-вход (запрет счета) счетчика 28 поступает Лог.1, которая запрещает режим счета счетчика. Появление на входах 25,12.1,12.2 мажоритарного элемента 29 хотя бы двух Лог.1 разрешает режим счета счетчика 28.

0 На информационных выходах счетчика 28 формируется кодовая информация, характеризующая период следования контролируемых сигнальных импульсов. При появлении на входах 25,12.1 и 12.2мажори5 тарного элемента 29 хотя бы двух Лог.О на его инверсном выходе, соединенном с инверсным СЬвходом счетчика 28, формируется сигнал Лог.1 - запрет счета. В дальнейшем измерение очередного интер0 вала импульсных последовательностей, поступающих на входы мажоритарного элемента 29, будет производиться при выполнении очередных программно устанавливаемых режимах Подготовка и Работа

5 аналогично описанному.

Формула изобретения 1. Устройство для контроля многоканальных импульсных последовательностей, содержащее первый канал, включающий

0 первый триггер синхронизации, счетчик числа контролируемых импульсов, элемент ИЛИ и мультиплексор, группа информационных входов которого является группой сигнальных входов канала, отличающееся

5 тем, что, с целью повышения точности функционирования устройства за счет селектирования сигналов по периоду их следования, введены второй и третий каналы, идентичные первому, причем в каждый канал допол0 нительно введены второй и третий триггеры синхронизации, элемент НЕ, мажоритарный элемент, блок измерения синхронизации, информационный вход которого соединен с шиной логической единицы, а

5 инверсный выход - с инверсным входом элемента ИЛИ, третий и четвертый синхров- ходы канала соединены с вторым и третьим входами блокировки блока измерения частоты, первая-третья группы нформацион0 ных входов и группа информационных выходов каждого из каналов соединены с соответствующими группами информационных входов и выходов устройства, группа сигнальных входов каждого из каналов под5 ключена к соответствующей группе сигналь- ных входов устройства, вход запуска устройства соединен с входами запуска каждого из каналов, первый выход сигнала синхронизации первого канала подключен к первым синхровходам второго и третьего

каналов, второй выход сигнала синхронизации первого канала соединен с третьими синхровходами второго и третьего каналов, первый выход сигнала синхронизации второго канала подключен к первому синхров- 5 ходу первого канала и к второму синхровходу третьего канала, второй выход сигнала синхронизации второго канала соединен с третьим синхровходом первого канала и четвертым синхровходом третьего 10 канала, первый выход сигнала синхронизации третьего канала подключен к вторым синхровходам первого и второго каналов, второй выход сигнала синхронизации третьего канала соединен с четвертыми синхров- 15 ходами первого и второго каналов.

2. Устройство поп.1,отличающее- я тем, что блок измерения частоты каждого канала содержит регистр хранения кода тактовой частоты, мультиплексор, счетчик 20

кода периода, мажоритарный элемент и генератор тактовых импульсов, группа выходов которого соединена с группой информационных входов мультиплексора, группа установочных входов блока подключена к группе информационных входов регистра хранения кода тактовой частоты, вход управления записью которого соединен с входом начальной установки блока и входом установки в О счетчика кода периода, выход регистра хранения кода тактовой частоты подключен к адресному входу мультиплексора, выход которого соединен со счетным входом счетчика кода периода, первый - третий входы блокировки блока подключены к соответствующим входам мажоритарного элемента, выход которого соединен с входом блокировки счетчика кода периода, группа выходов которого является группой выходов блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО БУФЕРИЗАЦИИ И СИНХРОНИЗАЦИИ ДЛЯ ОБРАБОТКИ НЕПРЕРЫВНОГО СИГНАЛА | 1990 |

|

SU1812885A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

| Устройство для мажоритарного выбора сигналов | 1989 |

|

SU1656539A1 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

| Многоканальный программируемый преобразователь код-фаза | 1990 |

|

SU1742998A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| СБОЕУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2541839C2 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2536434C2 |

| МАГИСТРАЛЬНО-МОДУЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2564626C2 |

| Адаптивное устройство для сопряжения ЭВМ с каналами связи | 1987 |

|

SU1532938A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано в качестве устройства для контроля многоканальных импульсных последовательностей в системах с трехканальным резервированием повышенной надежности и точности, например в электронных цифровых вычислительных машинах. Цель изобретения - повышение точности функционирования устройства за счет се- лектирования сигналов по периоду их следования. Устройство содержит три идентичных канала, каждый из которых включает три триггера синхронизации, мультиплексор, счетчик числа контролируемых импульсов, регистр хранения кода режима, мажоритарный элемент, элемент НЕ, элемент ИЛИ, блок измерения частоты, который, в свою очередь, содержит регистр хранения тактовой частоты, мультиплексор, счетчик кода периода, генератор тактовых импульсов, мажоритарный элемент. Устройство обеспечивает контроль всех импульсных последовательностей, измерение периодов следования импульсных последовательностей. 1 з.п.ф-лы, 4 ил. (Л С

S.1 7.7 8.1 3.1

Y.«VJ«4

061 72 8.2 9J6.3 73 8.3 9.3

J

f-,.-, v CVJ54I -.

сйееэ

Фиг.

-и.

АС fin

п&-ко

X/

&и

Хп

21

20

0

ъ

MJ

19

-#Ю.1

.г

П

W

18

и

16

Cff

122 12.1

21)

/7

Q

Ч

-011.1

+Un

U

sf-V

Фиг.З

Фиг .4

| Устройство для контроля многоканальных импульсных последовательностей | 1982 |

|

SU1042171A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для контроля многоканальных импульсных последовательностей | 1985 |

|

SU1298721A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1992-05-07—Публикация

1989-12-04—Подача