(54) УСТРСЙСТВО ДЛЯ УПРАВЛЕНИЯ МНОГОФАЗНЬШ

ИНВЕРТОРОМ

выход первого элемента ИЛИ соединен с входами установки в «I а выход второго элемента ИЛИ соединен с входами установки в «О триггеров в данном канале.

Элементы эквивалентности реализуют логические функции эквивалентности

R QP+QP,

гдер - состояние первого из триггеров канула,

Р - состояние выхода мажоритарного элемента, управляемого по одному из входов от данного триггера,

R - состояние выхода схемы эквивалентности.

При синфазной работе всех трех каналов сигналы на выходе первого триггера и на выходе соответствующего мажоритарного элемента совпадают по времени, поэтому на вйходе элементов эквивалентности и на установочных входах всех триггеров (через элемент ИЛИ) поддерживается уровень «Лог. I , не препятствующий нормальному переключению триггеров.

При случайном сбое одного из каналов нарушается синфазность между сигналами на выходе триггера данного канала и на выходе мажоритарного элемента, поэтому на выходе элемента эквивалентности фор- мируется уровень «Лог. О, устанавливаю:.щий триггеры данного канала через один из элементо ИЛИ в некоторое наперед заданное положение. Такая установка триггеров в определенное положение происходит -ДО тех пор, пока состояние данного канала не станет вновь эквивалентно состояниям двух других каналов. Аналогичным образом производится первоначальная установка син фазности каналов, что исключает необходи мость использования специальной схемы начальной установки, каналов и одинаковое состояние.

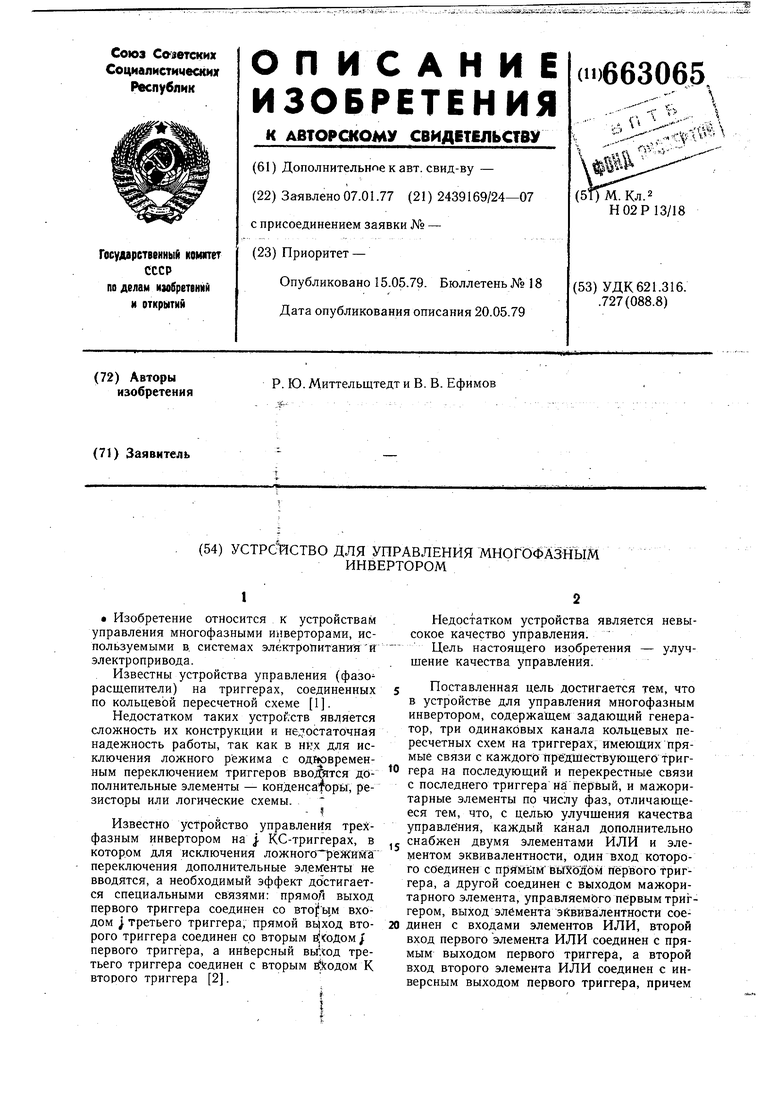

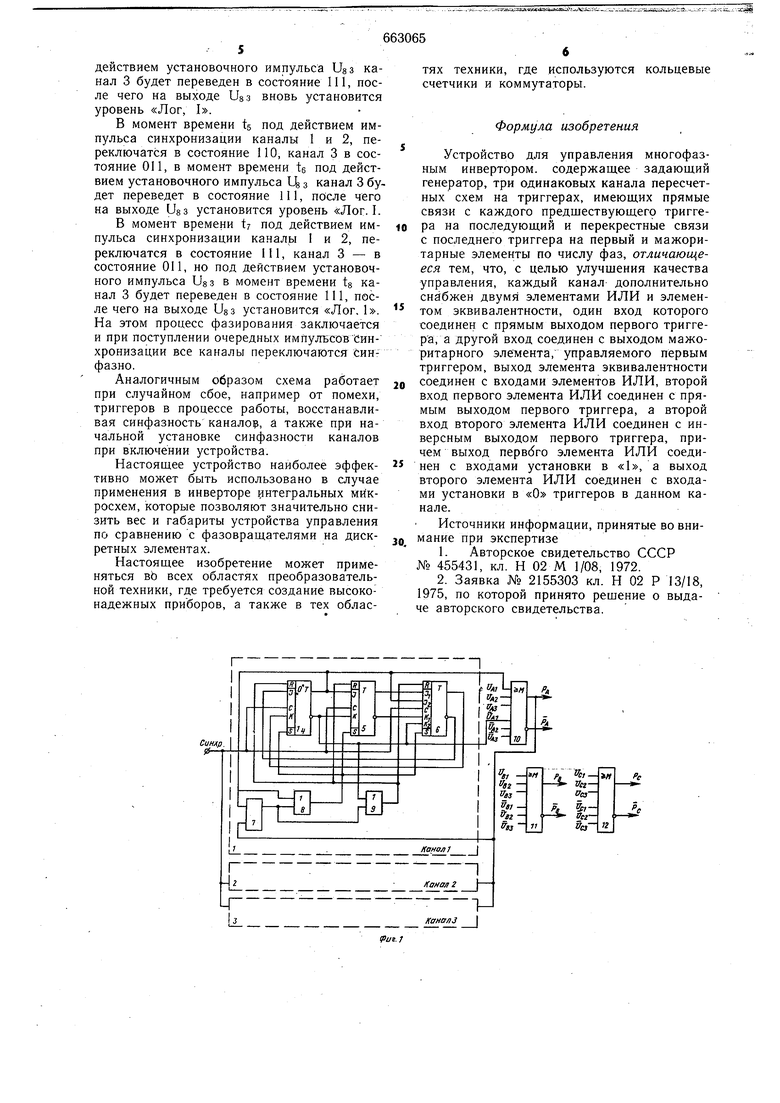

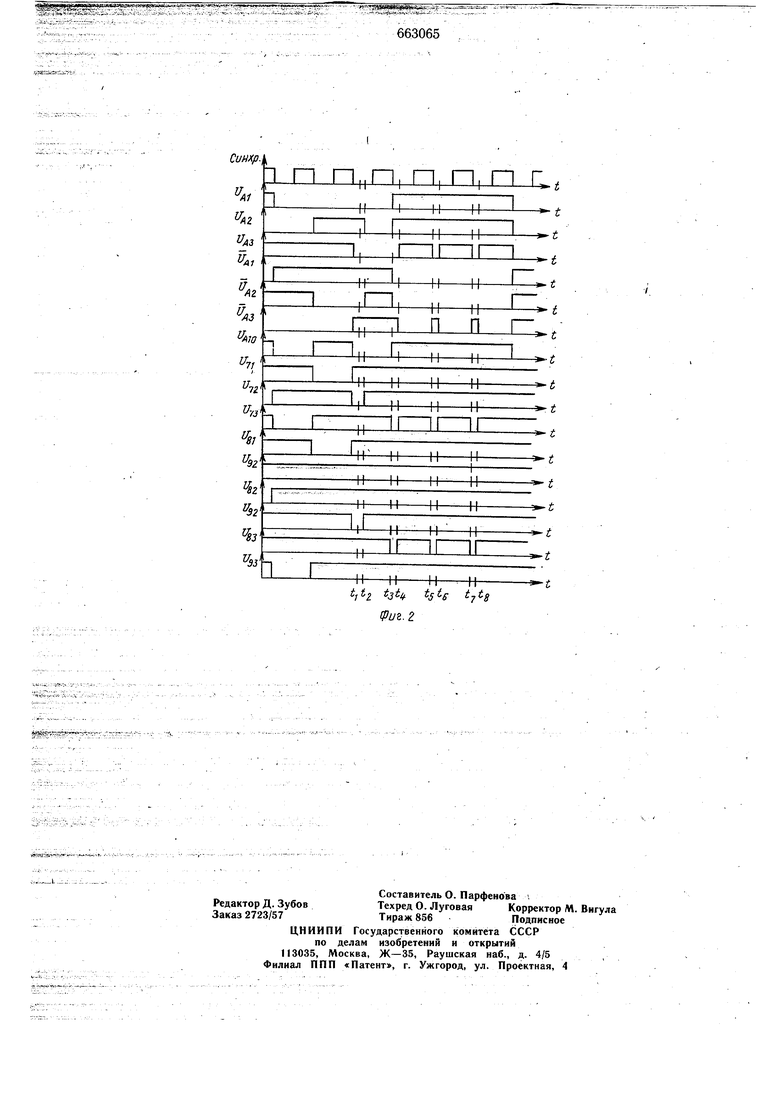

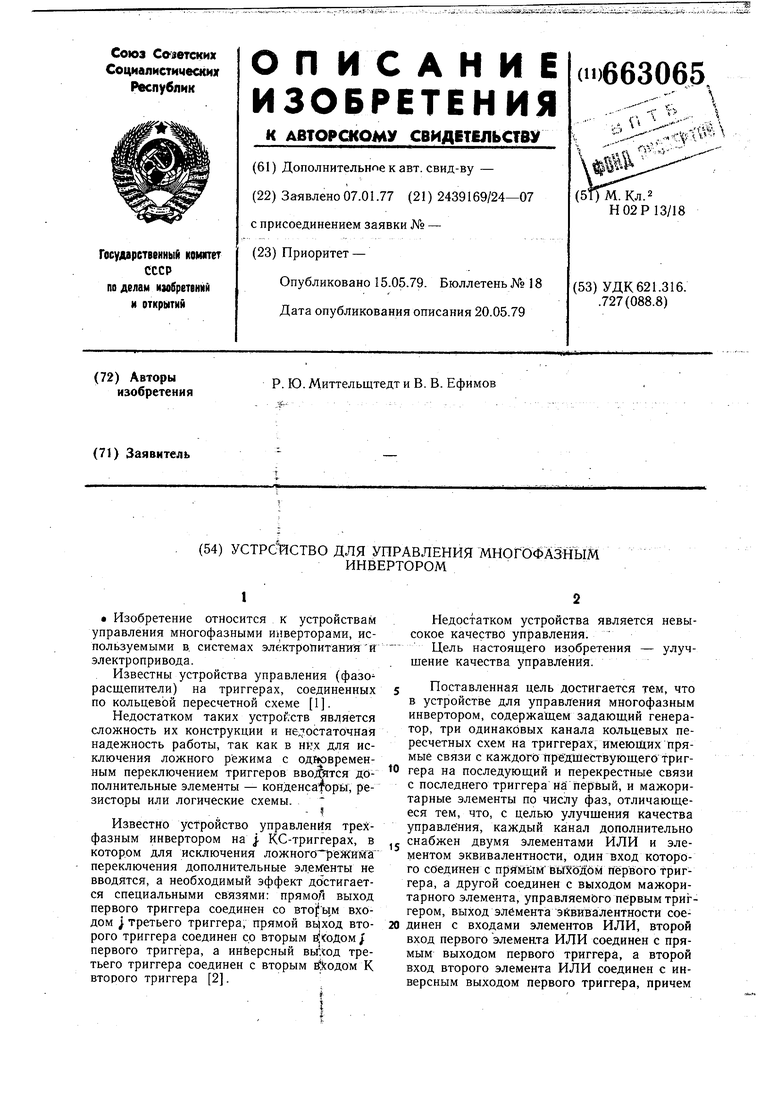

На фиг. 1 изображена схема устройства управления трехфазным инвертором; на фиг. 2 приведены эпюры напряжений на элементах устройства при работе схемы фазирования каналов.

Устройство управления содержит три одинаковых канала 1, 2 и 3, в каждый из которых входят три триггера 4, 5 и 6, элемент эквивалентности 7, два элемента ИЛИ 8 и 9 и три выходных мажоритарных элемента 10, 11 и 12.

Раздельные входы и К второго триггера соединены соответственно с прямым и инверсным выходами первого триггера, раздельные выходы и К третьего триггера соединены соответственно с прямым и инверсным выходами второго триггера, раздельные входы } и К первого триггера соединены соответственно с инверсным и прямым выходами третьего триггера, прямой выход первого триггера дополнительно соединен с вторым входом J третьего триггера, инверсный выход первого триггера дополнительно соединен с вторым входом К третьего триггера.

Каждая фаза выходного напряжения устройства управления формируется соответствующими двухтактными мажоритарныJ ми элементами (10, 11 и 12). на входы которых поступают прямые и инверсные сигналы с одноименных триггеров трех каналов.

Контроль и установка синфазности каналов осуществляются на первой фазе. С 0 этой целью прямой выход элемента 10 соединен с одним из входов элемента эквивалентности 7 в каждом канале, а другой вход элемента 7 соединен с прямым выходом триггера 4 того канала, в котором установ леи элемент 7. Выход элемента 7 соединен с одним из входов элементов ИЛИ 8 и 9 этого же канала, а вторые входы элементов 8 и 9 соединены с прямым и инверсным выходами триггера 4 этого канала.

В каждом канале выход элемента 8 сое0 динен с входами S установки в «I триггеров 4, 5 и 6, выход элемента 9 соединен с входами R установки в «О триггеров 4, 5 и 6.

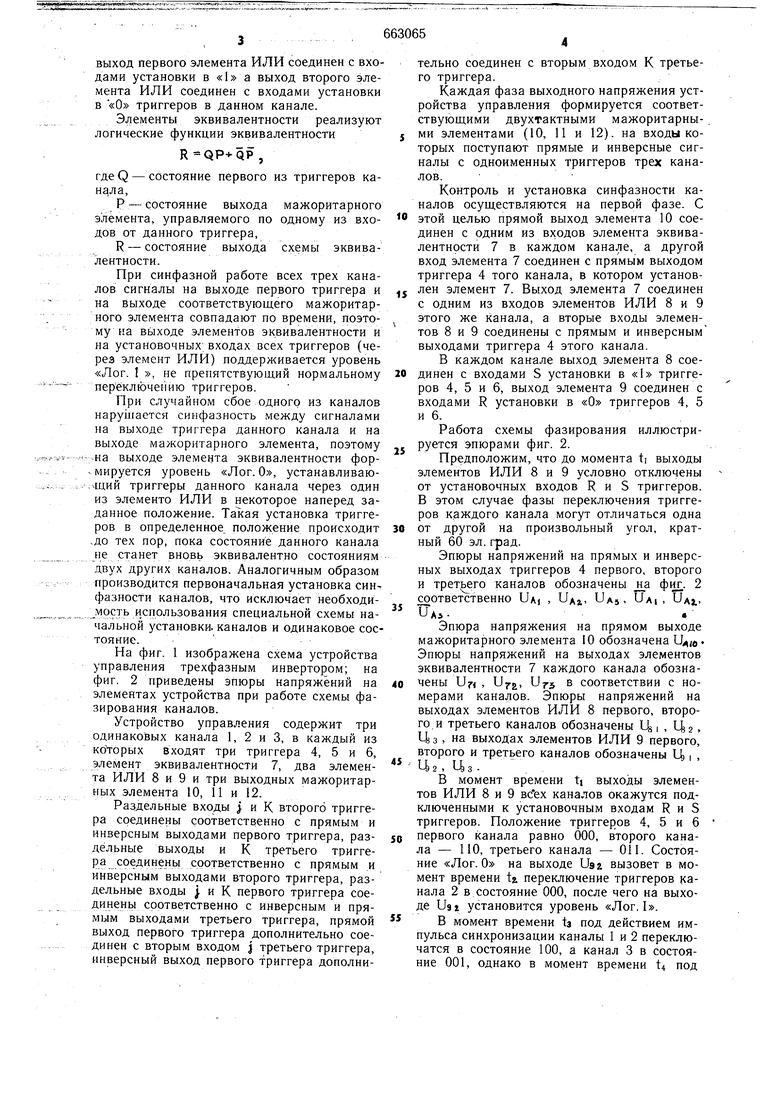

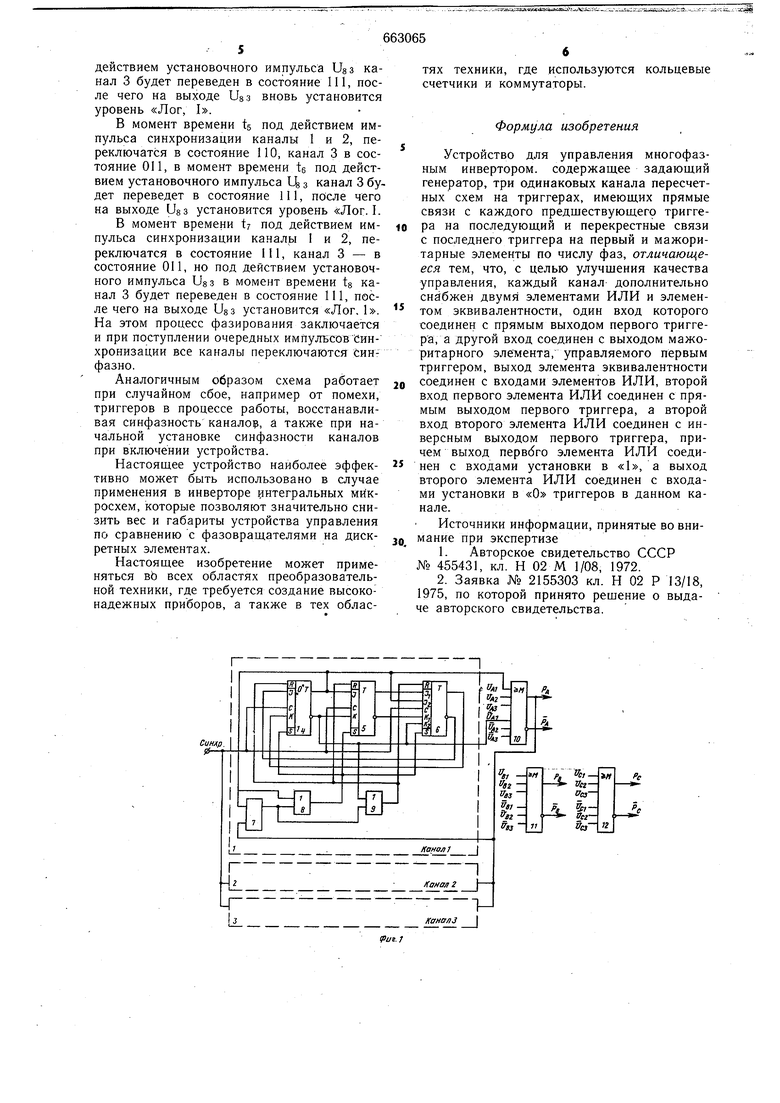

Работа схемы фазирования иллюстрируется эпюрами фиг. 2.

Предположим, что до момента ti выходы элементов ИЛИ 8 и 9 условно отключены от установочных входов R и S триггеров. В этом случае фазы переключения триггеров к.аждого канала могут отличаться одна 0 от другой на произвольный угол, кратный 60 эл. град.

Эпюры напряжений на прямых и инверсных выходах триггеров 4 первого, второго и третьего каналов обозначены фиг,. 2 соответственно UM , Ux, UAJ , UAJ , UAI, илз.

Эпюра напряжения на прямом выходе мажоритарного элемента 10 обозначена Ц(и . Эпюры напряжений на выходах элементов эквивалентности 7 каждого канала обозначены , . гй соответствии с номерами каналов. Эпюры напряжений на выходах элементов ИЛИ 8 первого, второго,и третьего каналов обозначены Ц, , Цг, Цз , на выходах элементов ИЛИ 9 первого, второго и третьего каналов обозначены Ц i ,

Цг. Цз- . .

В момент времени tj выходы элементов ИЛИ 8 и 9 всех каналов окажутся подключенными к установочным входам R и S триггеров. Положение триггеров 4, 5 и 6

0 первого канала равно 000, второго канала - 110, третьего канала - 011. Состояние «Лог. О на выходе Us г вызовет в момент времени tz, переключение триггеров канала 2 в состояние 000, после чего на выходе Usi установится уровень «Лог. I.

В момент времени ta под действием импульса синхронизации каналы 1 и 2 переключатся в состояние 100, а канал 3 в состояние 001, однако в момент времени t4 под

действием установочного импульса Ues канал 3 будет переведен в состояние 111, после чего на выходе Usa вновь установится уровень «Лог, I.

В момент времени tg под действием импульса синхронизации каналы 1 и 2, переключатся в состояние 110, канал 3 в состояние Oil, в момент времени te под действием установочного импульса Ц з канал 3 будет переведет в состояние 111, после чего на выходе USB установится уровень «Лог. I.

В момент времени t под действием импульса синхронизации каналь I и 2, переключатся в состояние 111, канал 3 - в состояние 011, но под действием установочного импульса Uss в момент времени ts канал 3 будет переведен в состояние 111, после чего на выходе Uss установится «Лог. 1. На этом процесс фазирования заключается и при поступлении очередных импульсов Синхронизации все каналы переключаются синфазно.

Аналогичным образом схема работает при случайном сбое, например от помехи, триггеров в процессе работы, восстанавливая синфазность каналор, а также при начальной установке синфазности каналов при включении устройства.

Настоящее устройство наиболее эффективно может быть использовано в случае применения в инверторе интегральных микросхем, которые позволяют значительно снизить вес и габариты устройства управления по сравнению с фазовращателями на дискретных элементах.

Настоящее изобретение может применяться вЬ всех областях преобразовательной техники, где требуется создание высоконадежных приборов, а также в тех областях техники, где используются кольцевые счетчики и коммутаторы.

Формула изобретения

Устройство для управления многофазным инвертором, содержащее задающий генератор, три одинаковых канала пересчетных схем на триггерах, имеющих прямые связи с каждого предществующегр триггера на последующий и перекрестные связи с последнего триггера на первый и мажоритарные элементы по числу фаз, отличающееся тем, что, с целью улучшения качества управления, каждый канал дополнительно снабжен двумя элементами ИЛИ и элементом эквивалентности, один вход которого соединен с прямым выходом первого триггера, а другой вход соединен с выходом мажоритарного элемента, управляемого первым триггером, выход элемента эквивалентности соединен с входами элементов ИЛИ, второй вход первого элемента ИЛИ соединен с прямым выходом первого триггера, а второй вход второго элемента ИЛИ соединен с инверсным выходом первого триггера, причем выход первбго элемента ИЛИ соединен с входами установки в «1, а выход второго элемента ИЛИ соединен с входами установки в «О триггеров в данном канале.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 455431, кл. Н 02 М 1/08, 1972.

2.Заявка № 2155303 кл. Н 02 Р 13/18, 1975, по которой принято рещение о выдаче авторского свидетельства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления многофазным инвертором | 1978 |

|

SU752749A1 |

| Устройство для управления @ -фазным инвертором | 1984 |

|

SU1248019A1 |

| Резервированное многоканальное устройство для формирования тактовых импульсов | 1978 |

|

SU767764A1 |

| Мажоритарно-резервированный делитель частоты | 1975 |

|

SU664299A1 |

| Резервированное устройство для синхронизации | 1984 |

|

SU1195489A1 |

| Устройство для контроля многоканальных импульсных последовательностей | 1989 |

|

SU1732332A1 |

| Многоканальное устройство синхронизации | 1988 |

|

SU1642473A1 |

| Резервированный счетчик импульсов | 1983 |

|

SU1125790A1 |

| РЕЗЕРВИРОВАННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 2022 |

|

RU2785274C1 |

| Резервированный делитель частоты | 1983 |

|

SU1109910A1 |

fc

J

Фиг. г

Авторы

Даты

1979-05-15—Публикация

1977-01-07—Подача