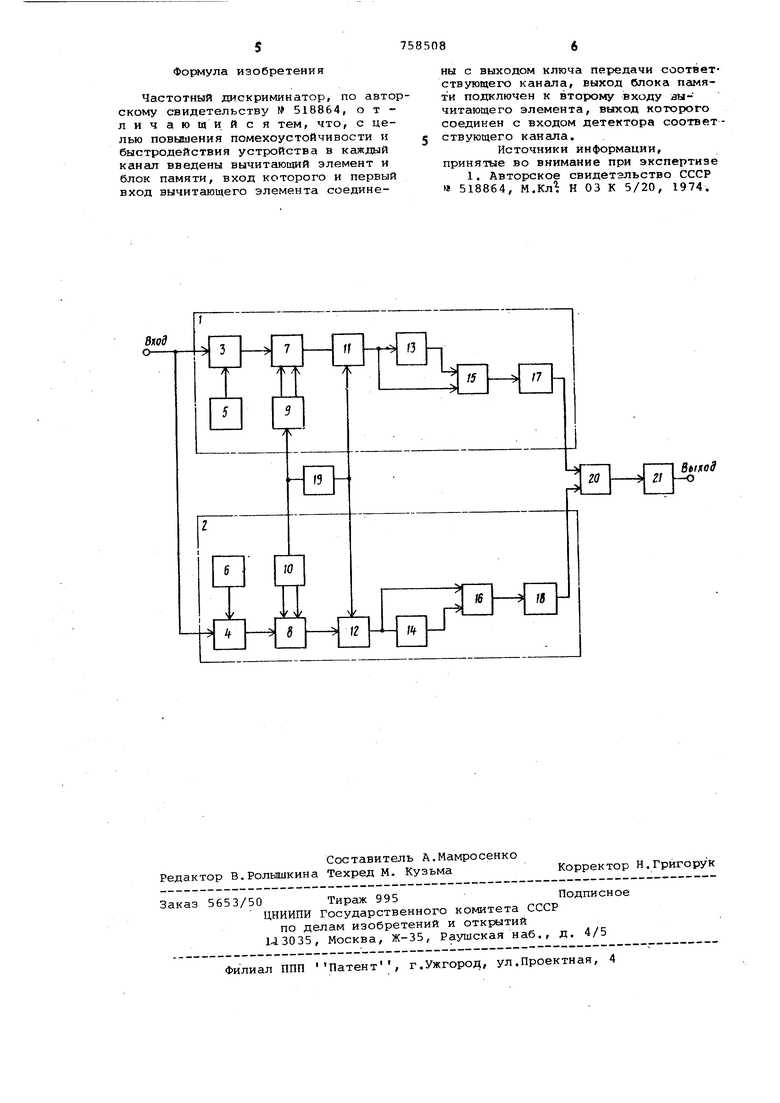

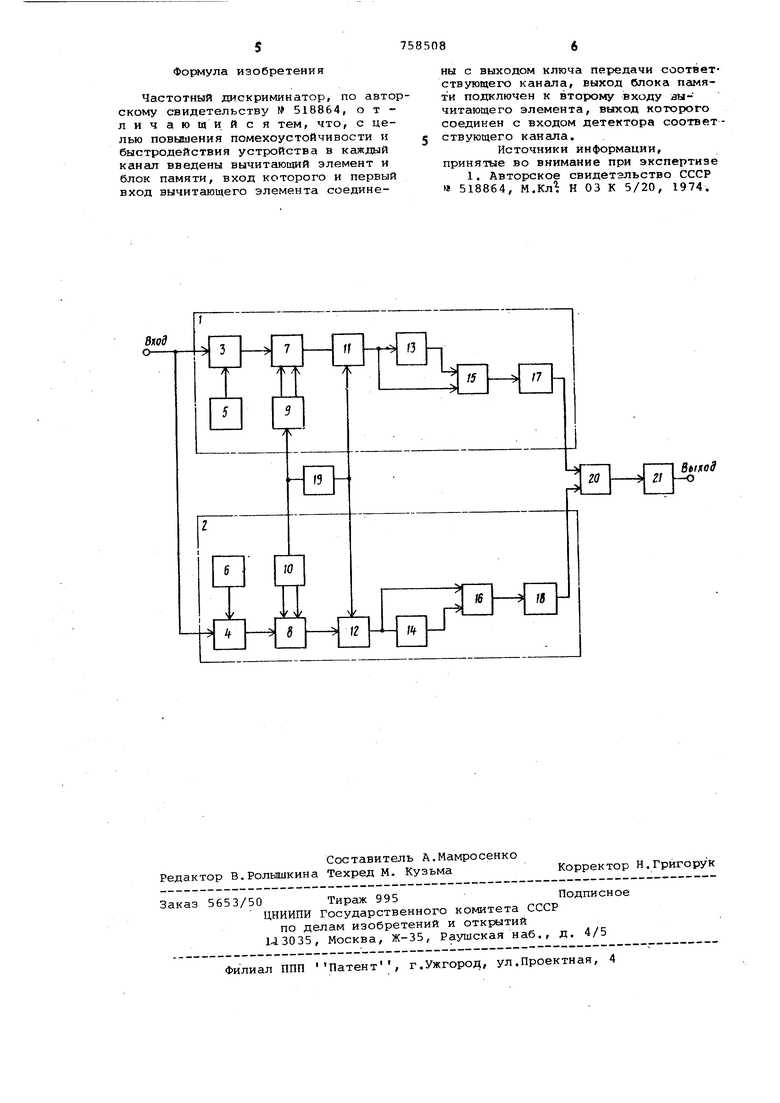

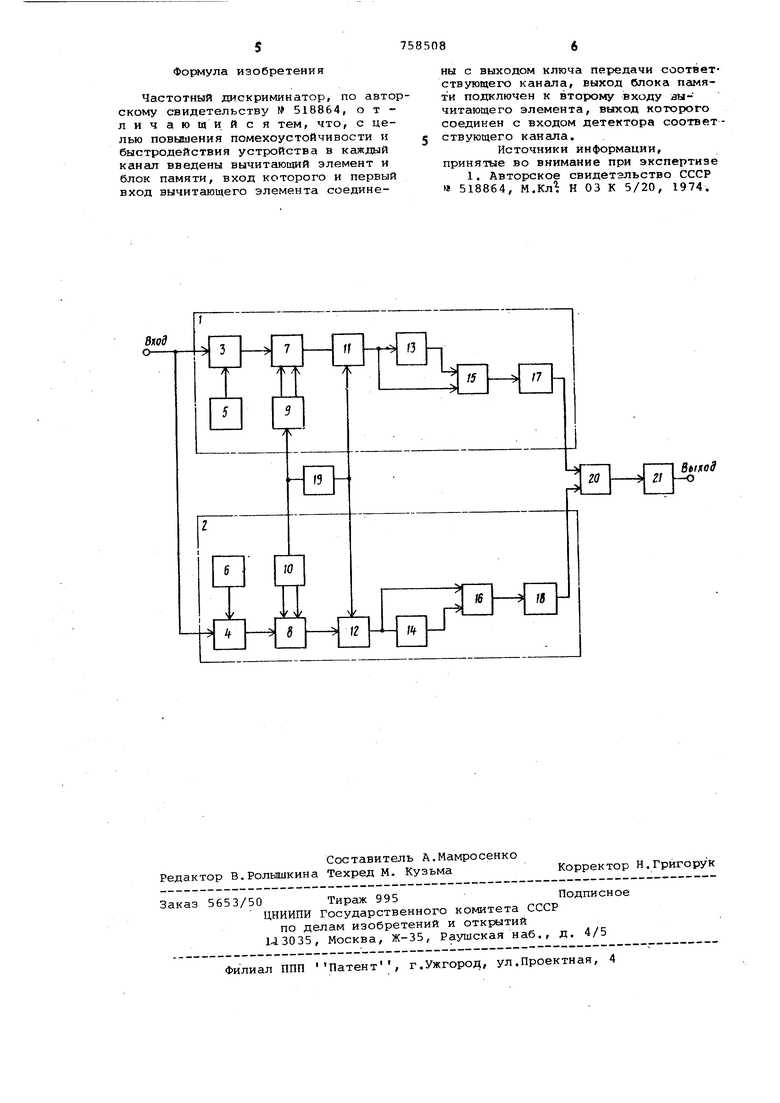

Изобретение относится к технике передачи дискретной информации по ка налам радио и электросвязи и может использоваться в многоканальных устройствах (модемах) передачи дискретной информации с ортогональными канальными сигналами для автоматической подстройки частоты (АПЧ). В основном авторском свидетельстве описан частотный дискриминатор,со держащий два параллельно соединенных канала, в каждом из которых первые входы перемножителей соединены с входной клеммой, вторые - с генератором опорных частот, а выходы - с входами интеграторов, выходы интегра торов соединены с входами компаратора, являющегося выходом устройства, первый выход устройтсва управления соединен с управляющими входами ключей сброса интеграторов, второй выхо - с управляющими входами ключей передачи, входы которых соединены с вы ходами интеграторов, а выходы ключей передачи - со входами детекторов выходы которых соединены со входами компаратора, выход, компаратора соединен с входом усреднителя, выход которого является выходом частотног .дискриминатора 1. Однако это устройство обладает недостаточно высокой помехоустойчивостью, так как результаты на выходах интергаторов зависят от смещения частоты и от информационных скачков фазы, приводящим к снижению помехоустойчивости частотного дискриминатора в целом. Кроме того, сигнал частотного смещения формируется по результатам обработки одного частотного подканала, что не позволяет добиться устойчивости дискриминатора по отношению к селективным замираниям и сосредоточенным по спектру помехам. Цель изобретения - повышение помехоустойчивости и быстродействия частотного дискриминатора. Это достигается тем, что в частотный дискриминатор по авт.св. 518864, содержащий два параллельносоединенных канала, в каждом из которых первые входы перемножителей соединены с входной клеммой, вторые - с генераторами опорных частот, а выходы - с .входами интеграторов, выходы интеграторов соединены с входами компаратора, являющегося выходом устройтсва, утсройство управления с ключами сброса -и передачи, детекторы и усреднитель. при этом первый выход устройствауправления соединен с управляющими вхо дами ключей сброса интеграторов второй выход - с управляющими входами кл чей передачи входы которых соединены выходами интеграторов, а выходы ключей передачи - с входами детекторов, ВЫХОДЫ) которых соединены с входами компаратора, а выход компаратора соединен с входом усреднителя, выход которого является выходом частотного дискриминатора, в каждый канал . введены вычитающий элемент и блок памяти, вход которого и первый вход вычитающего элемента соединены с выходом ключа, передачи cooT.BeTCTBjnoщего канала, выход блока памяти подключен к второму входу вычитающего элемента, выход которого соединен с входом детектора соответствующего ка нала, На чертеже представлена структурная электрическая схема частотного дискриминатора. Частотный дискриминатор содержит . каналы 1, 2, включающие соответствен но перемножители .3., 4, генераторы 5, 6 опорных частот, интеграторы 7, 8, ключи 9, 10, сброса; ключи И, 12 пе редачи, блоки 1.3, 14 памяти; вычитаю щие элементы 15, 16, детекторы 17 18 устройствоуправления ключами 19, ком паратор 20, усреднитель 21. Входом частотного дискриминатора являются объединенные первые входы перемножитёлей. 3 и 4, вторые входы которых подключены к генераторам 5 и б, а выходы через последовательные цепочки соответственно из интегратора 7, ключа 11, блока памяти 13, вычи тающего элемента 15, детектора 17 и интегратора В, ключа 12, блока памяти 14, вычитающего элемента 16, детектор 18 - к входам компаратора 20, выход которого связан через усреднитель 21 с выходом частотного дискриминатора. Первый выход устройства 19 управления ключами соединен через ключи 9 и 10 соответственно с управляющигл входами интеграторов 7 и 8, а второй выход с управляющими входами ключей 11 и 12. Частотный дискриминатор работает следующим образом. Частота генератора 5 канала 1 сдв нута на некоторую величину д в сторону увеличения, а генератора б кана ла 2 на ту же величину д сдвинута с сторону уменьшения относительно сред ней частоты f f равной., частоте одног из парцийнальных каналов,расположенн в центральной части спектра группово го сигнала. Рассмотрим случай, когда смещение частоты в канале связи отсутствует, Известно, что две выборки группового сигнала, взятые внутри одной по сылки и отстоящие на интервгш ортого нальности, равны между собой в силу 1ериодичности группового сигнала, если частота генератора ортогональна частотам парциальных сигналов, следовательно, разность, этих двух выборок будет равна нулю. Так как имеет место, сдвиг частоты Af генераторов 5и б, то условие ортогональности нарушено и разности выборок отличны от нуля. Это отличие (в обоих каналах 1 и 2 одинаковое по абсолютной величине, но противоположное по знаку) будет фиксироваться вычитающим элементов 15 в канале 1 путем вычитания напряжения выборки, взятой интегратором 7 в начале посылки и переписанной 6блок памяти 13, из напряжения выборки, взятой интергатором 7 в конце посылки и поступающей на вход вычитаю щего элемента 15 с выхода ключа передачи 11. Аналогичным образом работают во втором канале вычитающий элемент 16, интегратор 8, блок памяти 14, ключ передачи 12, что обеспечивает фиксацию разницы выборок противоположную по знаку фиксируемой разнице выборок в 1 канале. После выпрямления детекторами 17 и 18 выходных напряжений вьлчитающих элементов 15 и 16 будут получены два тока приблизительно одинаковые по . величине и по знаку. Компаратор 20 при этом отработает на выходе нулевой потенциал. Пусть имеет место такое смещение частоты в канале связи, что частота генератора 5 близка к ортогональной относительно частот парциальных каналов группового сигнала. При этом пари выборок на выходе интегратора 7становятся почти равными, а разность по абсолютной величине между парами выборок на выходе интегратора 8 увеличивается. Таким образом, на выходе детектора 17 устанавливается почти нулевой ток, а выходной ток детектора 18 увеличивается. Разность этих токов, измеренная компаратором 20, дает сигнал смещения частоты, абсолютная величина которого будет соответствовать абсолютному смещению частоты в канале связи, а знак укажет направление этого смещения. Усреднитель 21 усредняет во времени сигнал смещения частоты. В результате усреднения происходит на соплениё энергии сигнала расстройки частоты, т.е, повышается помехоустойчивость , частотного дискриминатора, Введение дополнительных элементов позволяет уменьшить чувст1ительность частотного дискриминатора к селективным замираниям сигнала и.сосредоточенным по спектру помехам, что приводит к повышению помехоустой чивости. и быстродействия.

Формула изобретения

Частотный дискриминатор, по авторскому свидетельству № 518864, о т л и ч а ю щи и с я тем, что, с целью повышения помехоустойчивости и быстродействия устройства в каждый канал введены вычитающий элемент и блок памяти, вход которого и первый вход вычитающего элемента соединены с выходом ключа передачи соответствующего канала, выход блока пгиляти подключен к второму входу аычитающего элемента, выход которого соединен с входом детектора соответствующего канала.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР tt 518864, М.Кл Н 03 К 5/20, 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| Частотный дискриминатор | 1977 |

|

SU708503A2 |

| Частотный дискриминатор | 1980 |

|

SU984020A1 |

| Частотный дискриминатор | 1974 |

|

SU518864A1 |

| Частотный дискриминатор | 1978 |

|

SU790252A1 |

| Устройство тактовой синхронизации | 1979 |

|

SU932642A1 |

| Демодулятор многоканального модема с амплитудно-фазоразностной манипуляцией | 1981 |

|

SU1019662A1 |

| АНАЛИЗАТОР СЛУЧАЙНЫХ ПРОЦЕССОВ | 1991 |

|

RU2012052C1 |

| Демодулятор многочастотных сигналов с амплитудно-фазовой модуляцией | 1983 |

|

SU1117856A1 |

| Устройство приема зондирующего сигнала | 1987 |

|

SU1566495A1 |

| Частотный дискриминатор | 1988 |

|

SU1676078A2 |

Авторы

Даты

1980-08-23—Публикация

1978-03-17—Подача