Изобретение относится -к автоматике и вычислительной технике и может быть использовано в составе аппаратуры для решения специальных задач. Известны устройства 1, содержащиедва генератора эталонных частот, два двоичных умножителя, дешифратор и запоминающее устройство и выполняющие задачу изменения выходной частоты в функции времени по кусочно-линейному закону, аппроксими рующеМу заданный закон изменения. Недостаток этих устройств состоит в ограничейных функциональных возможностях, что обусловлено нерациональной организацией хранения информации. Наиболее близким к изобретению является вычислительное устройство (2), для интерполяции, содержащее две пары последовательно соединенных счетчиков аргументов, запоминающее устройство, подключенное входами к потенциальным выходам первого и второго счетчиков аргументов, сумматор, регистры, схему сравнения и узел управления. Это устройство оперирует параллельными кодами, причем скорость развертывания аргументов ограничена необходимостью последовательного считывания из запоминающего устройства значений четырех ординат и последовательным выполнением алгоритма интерполяции для всех текущих значений аргументов. Цель изобретения - повышение быстродействия устройства. Это достигается тем, что в устройство, содержащее память, соединенную входами соответственно с выходами первого и второго счетчиков интервалов, сумматор, счетчик, соединенный входом с управляющим выходом первого счетчика интервалов, а управляющим выходом - со входом второго счетчика интервалов, и счетчик результата, введень два узла двоичных умножителей и элемент ИЛИ, причем выходы памяти подключены к соответствующим входам первого узла двоичных умножителей, импульсный вход которого является входом опорной частоты устройства, первый выход соединен со входом первого счетчика интервалов, второй выход - с первым входом сумматора, а третий выход - со вторым входом сумматора и первым входом элемента ИЛИ, подключенного выходом ко входу счетчика результата, выход которого является В1йходом устройства, выходы сумматора и счетчика подключены к соответствующим входам второго узла двоичных умножителей, соединенного выходом со вторым входом элемента ИЛИ.

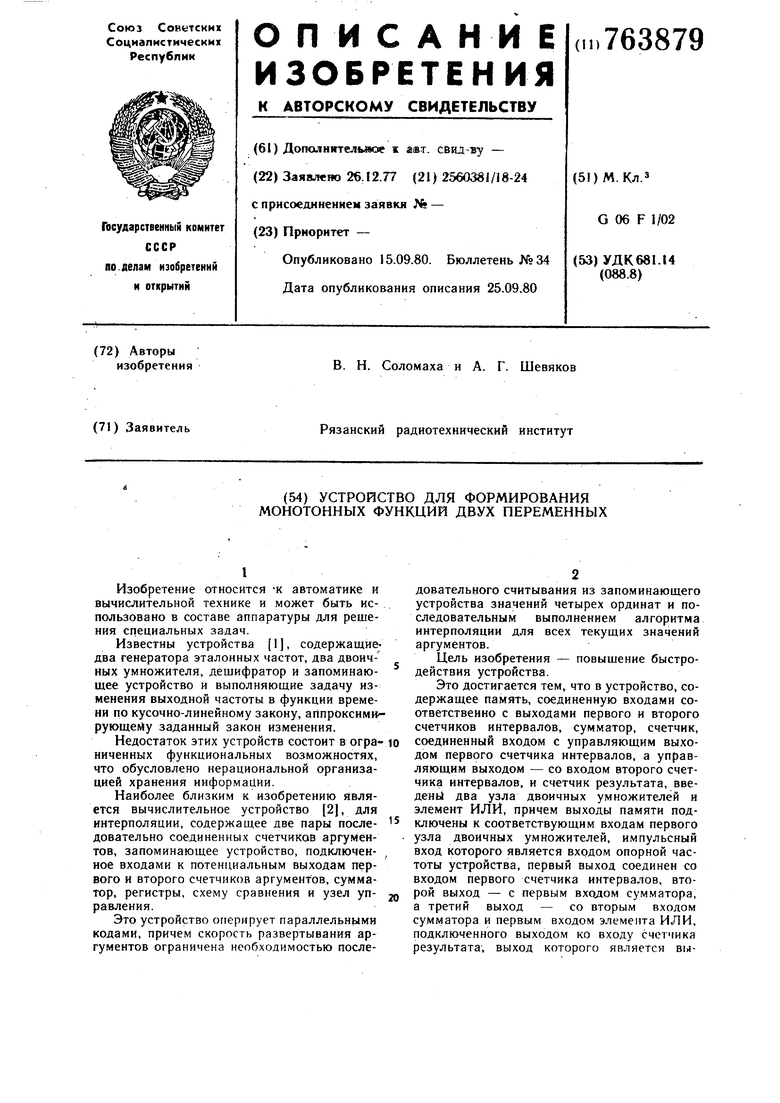

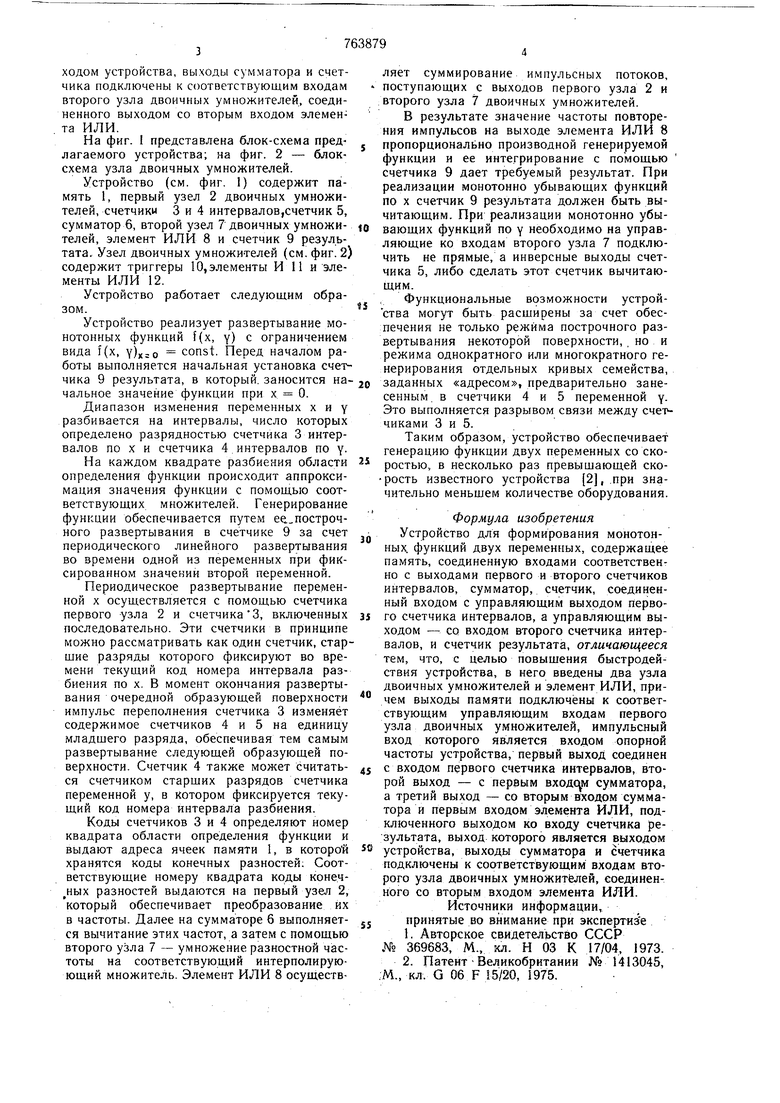

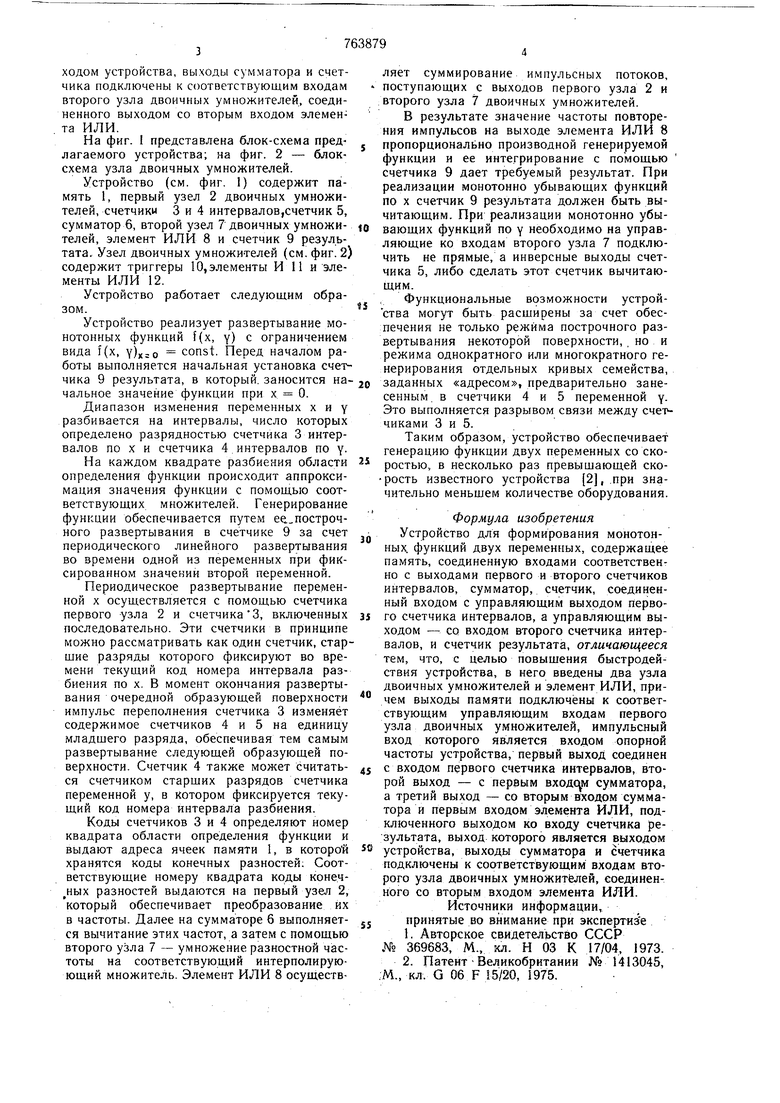

На фиг. I представлена блок-схема предлагаемого устройства; на фиг. 2 - блоксхема узла двоичных умножителей.

Устройство (см. фиг. 1) содержит память 1, первый узел 2 двоичных умножителей, счетчикм 3 и 4 интервалов,счетчик 5, сумматор б, второй узел 7 двоичных умножителей, элемент ИЛИ 8 и счетчик 9 результата. Узел двоичных умножителей (см. фиг. 2) содержит триггеры 10,элементы И 11 и элементы ИЛИ 12.

Устройство работает следующим образом.

Устройство реализует развертывание монотонных функций f(x, Y) с ограничением вида i(x, Y) const. Перед началом работы выполняется начальная установка сче-гчика 9 результата, в который, заносится начальное значение функции при х 0.

Диапазон изменения переменных х и у разбивается на интервалы, число которых определено разрядностью счетчика 3 интервалов по X и счетчика 4 интервалов по уНа каждом квадрате разбиения области определения функции происходит аппроксимация значения функции с помощью соответствующих множителей. Генерирование функции обеспечивается путем ее.,построчного развертывания в счетчике 9 за счет периодического линейного развертывания во времени одной из переменных при фиксированном значении второй переменной.

Периодическое развертывание переменной X осуществляется с помощью счетчика первого узла 2 и счетчика3, включенных последовательно. Эти счетчики в принципе можно рассматривать как один счетчик, старщие разряды которого фиксируют во времени текущий код номера интервала разбиения по X. В момент окончания развертывания очередной образующей поверхности импульс переполнения счетчика 3 изменяет содержимое счетчиков 4 и 5 на единицу младщего разряда, обеспечивая тем самым развертывание следующей образующей поверхности. Счетчик 4 также может считаться счетчиком старщих разрядов счетчика переменной у, в котором фиксируется текущий код номера интервала разбиения.

Коды счетчиков 3 и 4 определяют номер квадрата области определения функции и выдают адреса ячеек памяти 1, в KOTOpoti хранятся коды конечных разностей; Соответствующие номеру квадрата коды конеч ных разностей выдаются на первый узел 2, который обеспечивает преобразование их в частоты. Далее на сумматоре б выполняется вычитание этих частот, а затем с помощью второго узла 7 - умножение разностной частоты на соответствующий интерполируюющий множитель. Элемент ИЛИ 8 осуществляет суммирование импульсных потоков, поступающих с выходов первого узла 2 и второго узла 7 двоичных умножителей.

В результате значение частоты повторения импульсов на выходе элемента ИЛИ 8

пропорционально производной генерируемой функции и ее интегрирование с помощью счетчика 9 дает требуемый результат. При реализации монотонно убывающих функций по X счетчик 9 результата должен быть вычитающим. При реализации монотонно убывающих функций по Y необходимо на управляющие ко входам второго узла 7 подключить не прямые, а инверсные выходы счетчика 5, либо сделать этот счетчик вычитающим.

Функциональные возможности устройства могут быть расщирены за счет обеспечения не только режима построчного развертывания некоторой поверхности, , но и режима однократного или многократного генерирования отдельных кривых семейства,

0 заданных «адресом, предварительно занесенным, в счетчики 4 и 5 переменной у. Это выполняется разрывом связи между счет чиками 3 и 5.

Таким образом, устройство обеспечивает генерацию функции двух переменных со скоростью, в несколько раз превышающей скорость известного устройства 2,.при значительно меньшем количестве оборудования.

Формула изобретения Устройство для формирования монотонных, функций двух переменных, содержащее память, соединенную входами соответственно с выходами первого и второго счетчиков интервалов, сумматор, счетчик, соединенный входом с управляющим выходом первого счетчика интервалов, а управляющим выходом - со входом второго счетчика интервалов, и счетчик результата, отличающееся тем, что, с целью повыщения быстродействия устройства, в него введены два узла двоичных умножителей и элемент ИЛИ, причем выходы памяти подключены к соответствующим управляющим входам первого узла двоичных умножителей, импульсный вход которого является входом опорной частоты устройства, первый выход соединен

5 с входом первого счетчика интервалов, второй выход - с первым входс м сумматора, а третий выход - со вторым входом сумматора и первым входом элемента ИЛИ, подключенного выходом ко входу счетчика результата, выход которого является выходом устройства, выходы сумматора и счетчика подключены к соответствующим входам второго узла двоичных умножителей, еоединенного со вторым входом элемента ИЛИ. Источники информации,

J принятые во внимание при экспертизе

1.Авторское свидетельство СССР

№ 369683, М., кл. Н 03 К 17/04, 1973.

2.Патент Великобритании № 1413045, ;М., кл. Q Об F 15/20, 1975.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интерполятор поверхности | 1980 |

|

SU942040A1 |

| Устройство для вычисления обратных функций | 1980 |

|

SU942007A1 |

| Генератор функций | 1984 |

|

SU1275411A1 |

| Генератор функций | 1984 |

|

SU1241219A1 |

| Устройство для вычисления обратных функций | 1983 |

|

SU1109745A1 |

| Цифровой преобразователь координат | 1980 |

|

SU942004A1 |

| Число-импульсный функциональный преобразователь | 1980 |

|

SU924715A2 |

| Число-импульсное устройство для вычисления обратного тригонометрического тангенса | 1983 |

|

SU1092498A1 |

| Устройство для выбора частотных диапазонов передачи группового радиосигнала | 1982 |

|

SU1072277A1 |

| Интерполятор | 1984 |

|

SU1206805A1 |

ч..

ч

10

10

-и

fB

Авторы

Даты

1980-09-15—Публикация

1977-12-26—Подача