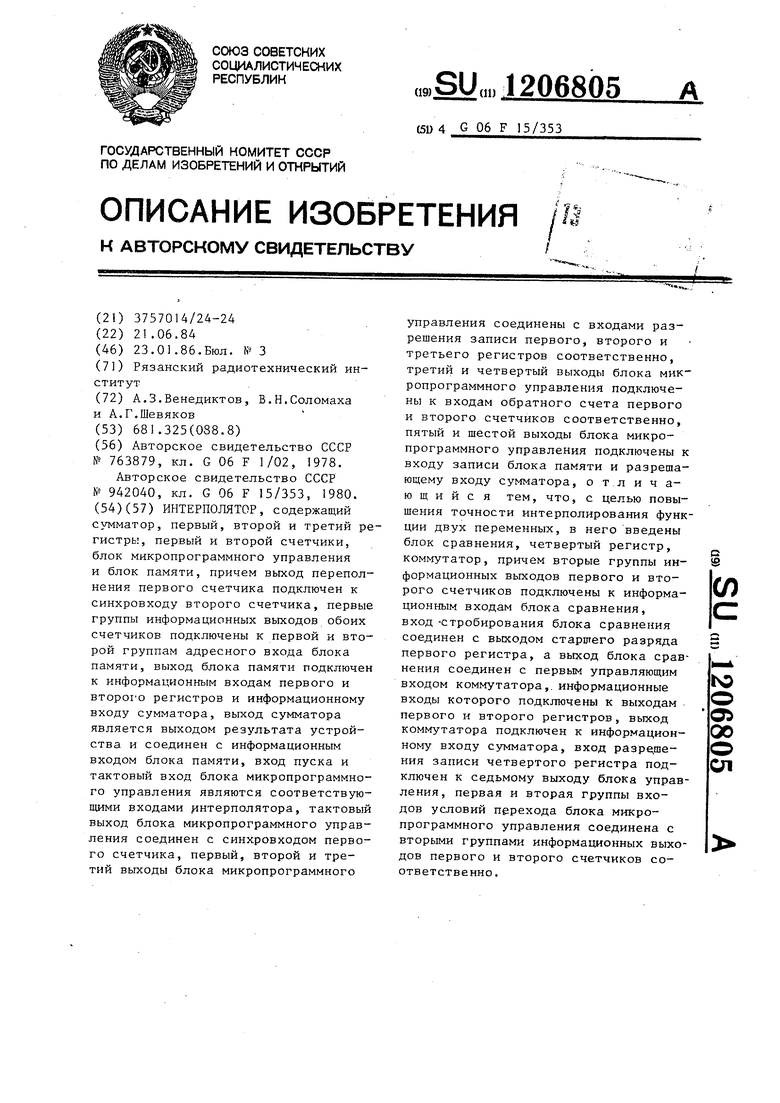

Изобретение относится к вычисши- тельной технике, автоматике и телемеханике и может быть использовано в качестве задающих устройств при сканировании двумерных функций, устройств линеаризации характеристик двухканальных измерительных преобразователей развертывающего типа и т.п.

Цель изобретения - повышение точности интерполирования поверхностей, заданных функциями двух переменных в узловых точках с равномерным разбиением их области определения.

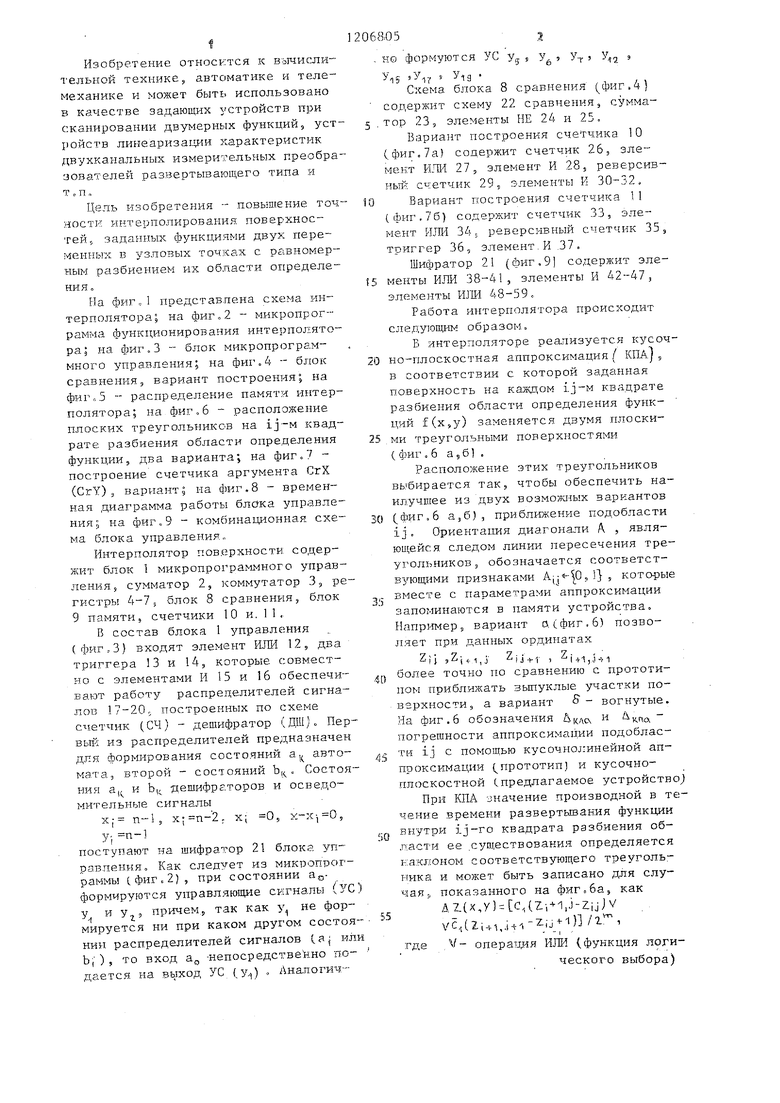

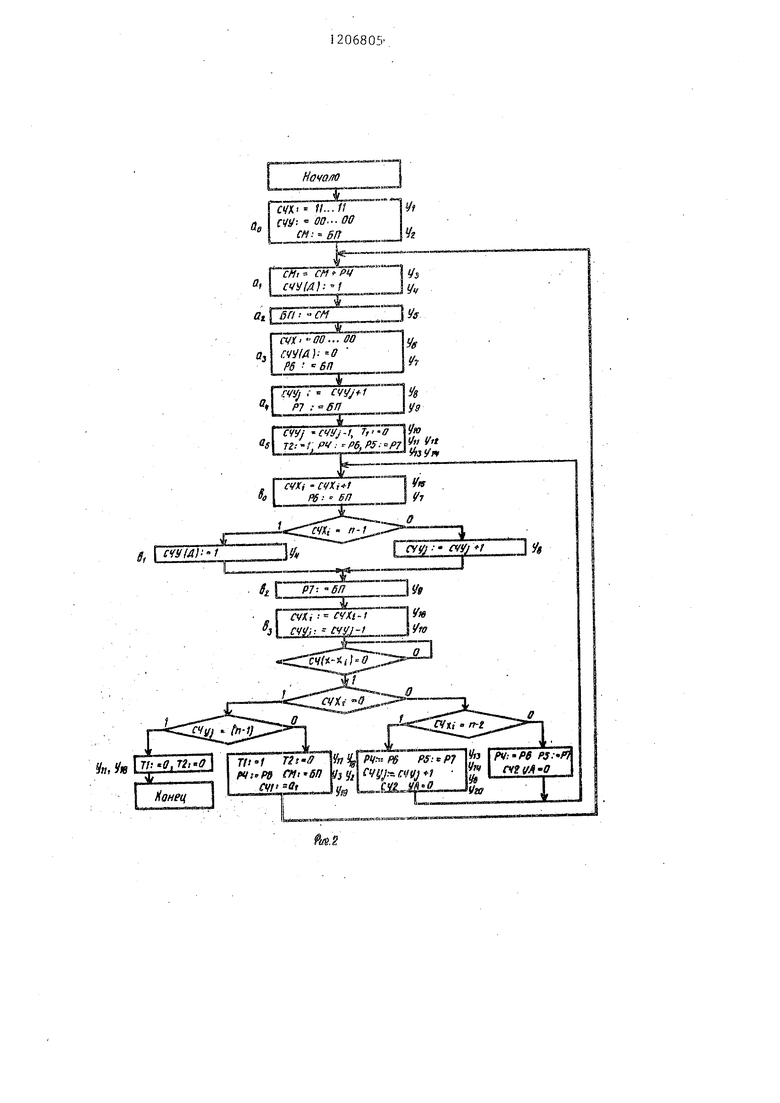

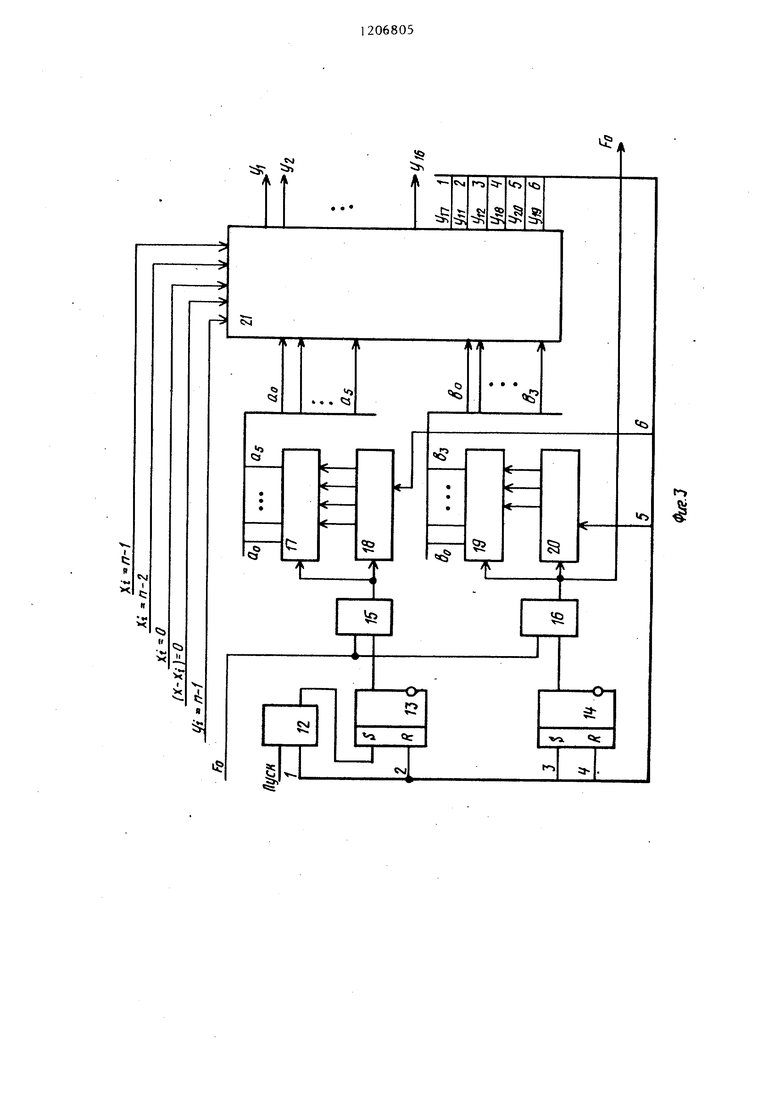

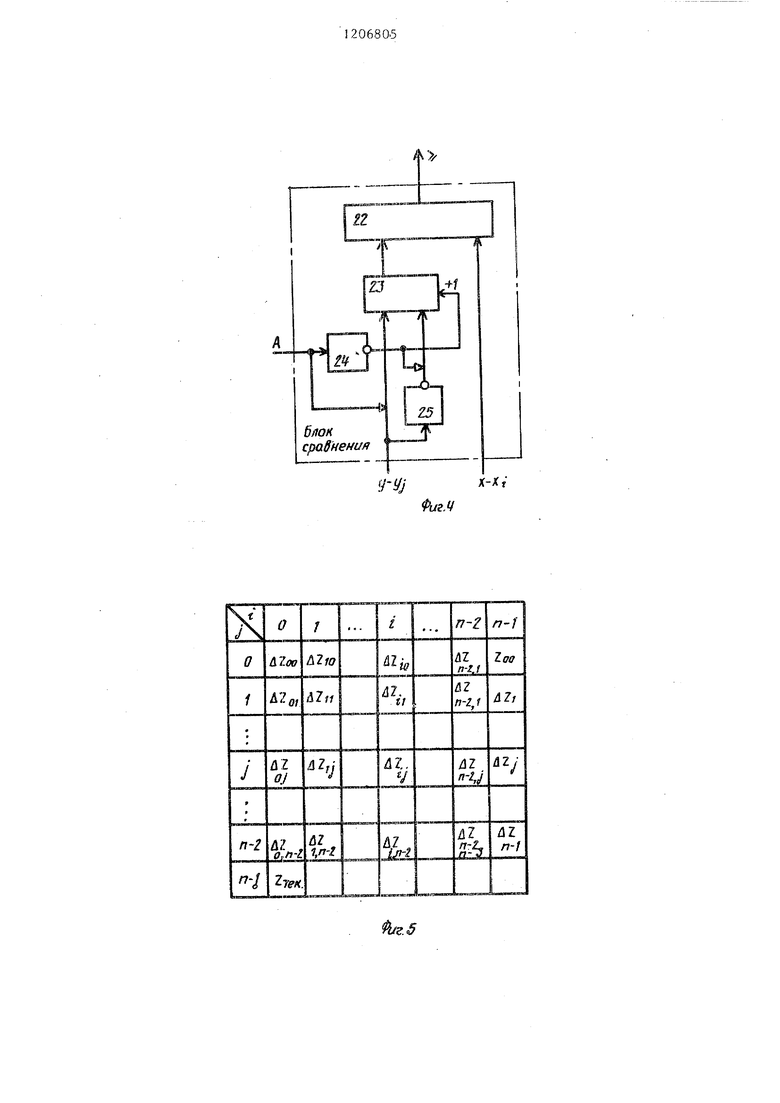

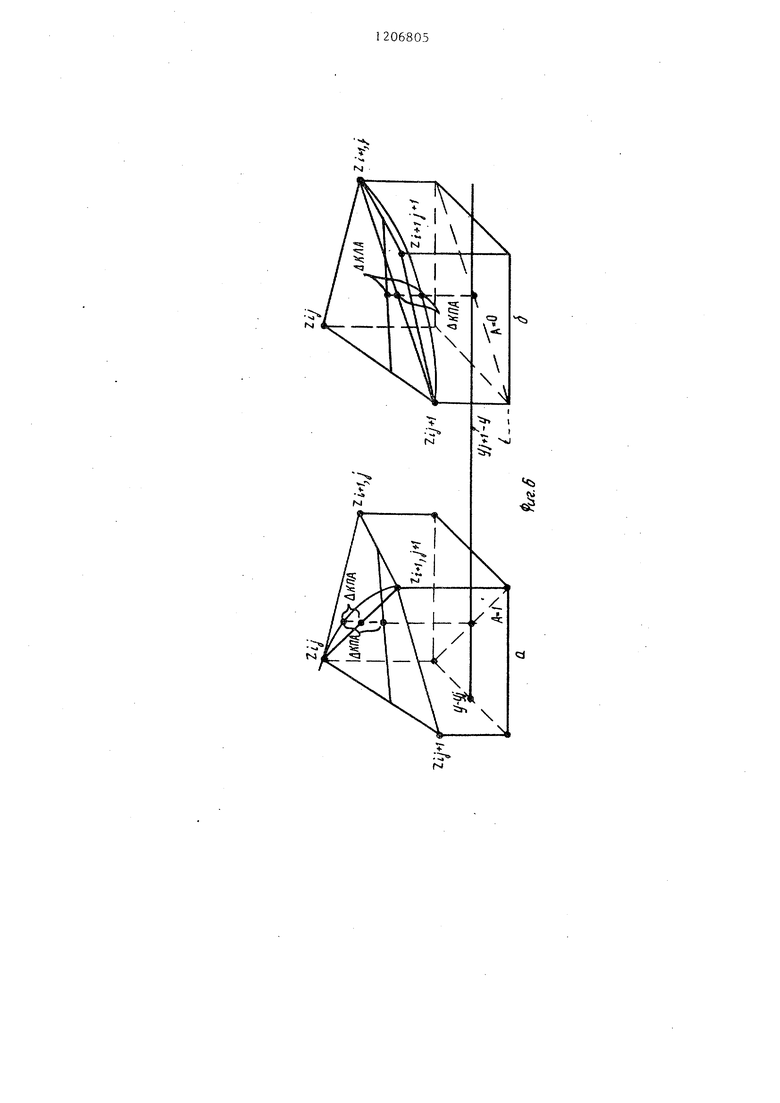

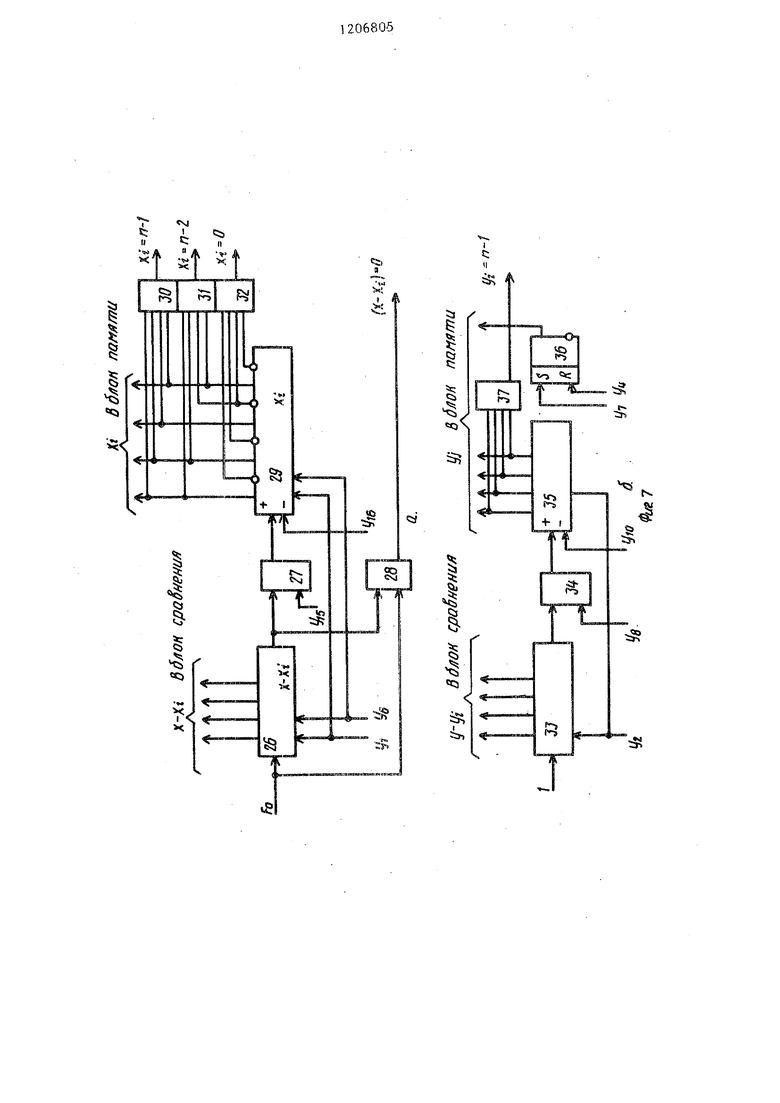

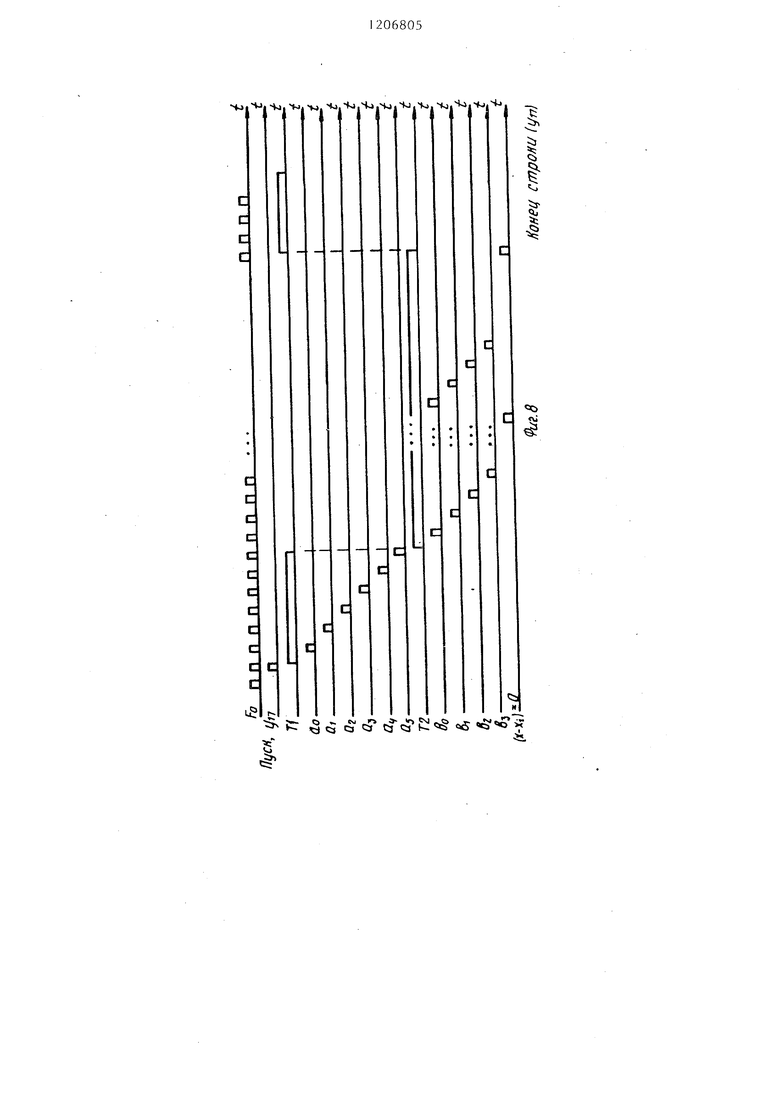

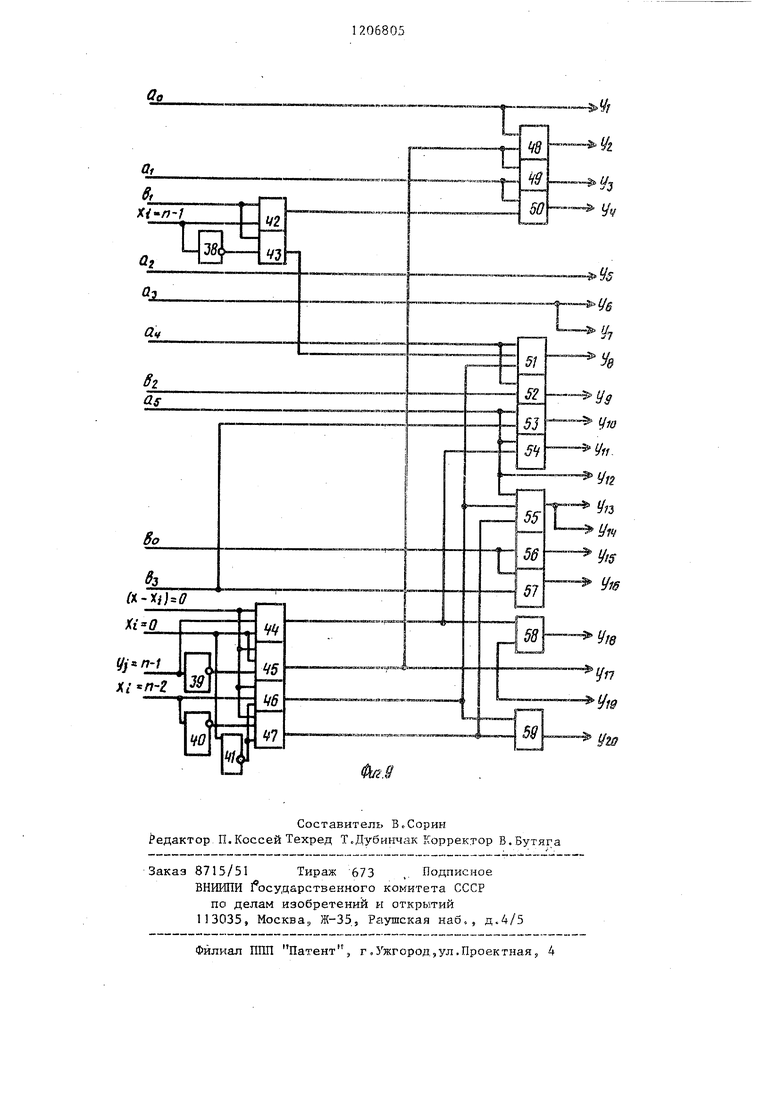

На фиг о 1 представлена схема интерполятора; на фиг.2 - микропрограмма функционирования интерполятора; на фиг.3 - блок микропрограммного управления; на фиг.4 - блок сравнения, вариант построения; на - распределение памяти интерполятора; на фиг,6 - расположение плоских треугольников на ij-м квадрате разбиения области определения функции, два варианта; на фиг.7 - построение счетчика аргумента СгХ (CrY)5 вариант; на фиг.8 - временная диаграмма работь блока управления; на фиг,9 - комбинационная схема блока управления..

Интерполятор поверхности содержит блок 1 микропрограммного управления, сумматор 2, коммутатор 3, регистры 4-75 блок 8 сравнения, блок 9 памяти, счетчики 10 и. 11„

В состав блока 1 управления ( фиг 3) входят элемент ИЛИ 12, два триггера 3 и 14, которые совм:ест- но с элементами И 15 и 16 обеспечивают работу распределителей сигналов 17-20,. построенных по схеме счетчик (СЧ) - дешифратор (ДШ)р Пер вьп4 из распределителей предназначен для формирования состояний а, автомата, второй - состояний Ъ,. Состояния а,, и bi дешифраторов и осведомительные сигналы

Х п-1 5 , х; 0, Х-Х-, 0,

У-, п-1

поступают на шифратор 21 блока управления. Как следует из микропрограммы фиг, 2), при состоянии формируются управляющие сигналы (УС у и у,,,, причем, так как у не формируется ни при каком другом состоя НИИ распределителей сигналов (а ил Ь,), то вход а„ -непосредственно подается на выход УС (у.,) ЛнапогичKQ формуются УС y,j , у , у У.

т « 9

1э 13

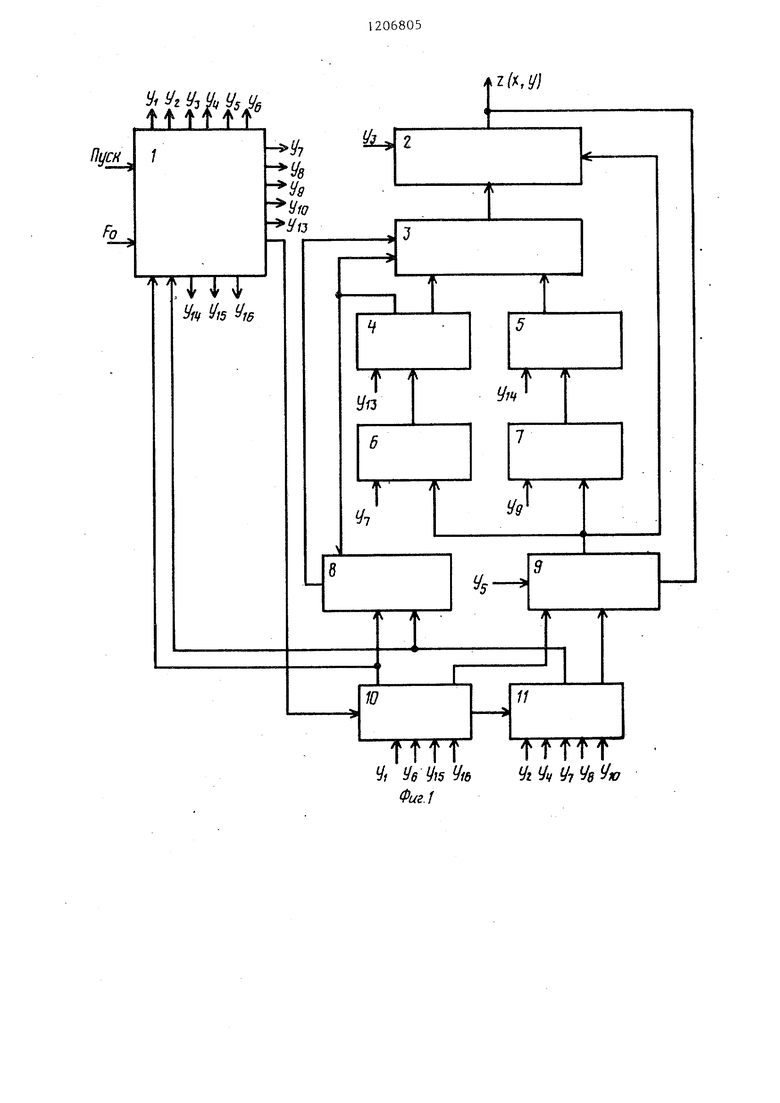

Схема блока 8 сравнения (фиг.4) содержит схему 22 сравнения, сумматор 23, элементы НЕ 24 н 25,

Вариант построения счетчика 10 (фиг.7а) содержит счетчик 26, элемент КШ 27, элемент И 28, реверсивный счетчик. 29, элементы И 30-32,

Вариант построения счетчика 11 (фиг.76) содержит счетчик 33, элемент ИЛИ 34, реверсивный счетчик 35, триггер 36, элемент . И .37.

Шифратор 21 (фиг,9) содержит элементы ИШ 38-41, элементы И 42-47, элементы ИЛИ .48-59,.

Работа интерполятора происходит следующим образом.

Б интерполяторе реализуется кусочно-плоскостная аппроксимация ( , в соответствии с которой заданная поверхность на каждом i.j-м ква.драте разбиения области определения функций (х,зО заменяется двумя плоскими треугольными поверхностями (фиг,6 а 5 б 1 .

Ра.сположение этих треугольников выбирается так, чтобы обеспечить наилучшее из двух возможных вариантов

(фиг.6 aj6), приближение подобласти ij. Ориентация диагонали А , явля- юи ейся следом линии пересечения тре- ут ольников, обозначается соответствующими признаками ,}, которые

вместе с параметрами аппроксимации запоминаются в памяти устройства. Напр1-1мер, вариант о, (Фиг., 6) позволяет при данных ординатах

у 7 . . 7 . . 7

-1 J э ( .( 1, J I J -Ц 5 U-1, ..1 -, 1

более точно по сравнению с прототипом приближать вьшуклые участки поверхности, а вариант S - вогнутые. На фиг .6 обозначения h,c и . погрешности аппроксимап.ии подобластк ij с помощью кусочно1:инейной аппроксимации (прототип) и кусочно- плоскостной с.предлагаемое устройство) При КПА значение производной в течение времени развертывания функции

внутри ij-ro квадрата разбиения области ее .существования определяется 17:аклоном соответствующего треугольника и может быть записано для случая s показанного на фиг.ба, как A.Z(x,y)C,(,J ZijjV

VC,(Zi-,,,.,) где V- операщля ИЛИ (функция логического выбора)

Сд fO, при (X-Xj)(y - yj; ;

11 , при (x-x i);(y - yj) . 2 - шаг аппроксимации.

и задает принадлежность точки с ко- фиг.6 б, выражение производной по ординатами х и у одному из треуголь- 5 имеет вид

A2U,Y) ,J-Z-,;)VCj(Zu,,,,-Zij,,)

Го, если (, x-x,)и учитьшая, что рассмотренные случаи

С л. ,г,т- расположения треугольников разли.1, если (x-x;)Cy-yj) Вводя обозначения

А i j Z i -1, j ij 1 ij+i 2.i.,j.-Zjjj i

10

чаются соответствующим значением признака Ajj«-- 0,l}, получаем общее выражение для вычисления значения производной на ij-м квадрате разбиения .

(О

AZ(X,V)AijCA2ijV ;jCuZij+iVAijC&Z;j iV (1)

VAijCUZ;j /Z ,

0.ecrt«(x-X;)i:Aij(y-yj)VAij(yj4i-y);

l,etftH(x-Xi)AjjCy-Yj)VAij() .

1 управления (фиг.З) в соответстгАс С ;

Это выражение и-положено в основу реализации устройства.

Управление процессом построчного развертывания осуществляется с помощью последовательно включенных счетчиков аргументов С 10 и 11, младшие разряды которых фиксируют величины {х-х)и(у - yj) соответственно, а старшие - коды номеров квадратов разбиения ij (х, и yj ). Формирование значения CG{0,1} осуществляется с помощью блока 8 сравнения, к входам схемы 22 сравнения подключается код (х-х;)-и прямой или дополнительный код (У у/). Формирование дополнительного кода (y-yJ) - У осуществляется с помощью сумматора 23, к которому в зависимости от признака Ajj подключается прямой или обратный (.инверсный) код y-yj . Кроме того, на вход переноса младшего разряда сумматора 23 подключается блок 1 в случае формирования дополнительного кода.

На фиг.З показано распределение блока 9 памяти. В ячейках, адреса которых задаются значениями х; ,у , хранятся: Zoof-начальное значение функций; dZjj - величины приращений для построчного развертывания f(x,y); AZj- - величины приращений для вычисления значений функции в начале каждой строки; ячейка для хранения текущего значения функ- ции в начале строки.

Функционирование устройства осуществляется по сигналам у - у блока

ВИИ с микропрограммой (фиг.2).

В исходном состоянии (перед гене- 2, рированием функции) в сумматор 2 интерполятора из блока 9 памяти передается начальное значение функции (XQ,уд). Дпя этого блок управления по состоянию а,

присваивает

30

35

40

счетчикам 10 и 11 адрес ячейки памяти, где хранится значение Z. Далее содержимое сумматора 2 передается в ячейку блока 9 памяти, где хранится текущее значение функции в начале строки (.). Адрес этой ячейки задается с помощью дополнительного разряда счетчика 11 (состояния а, . Затем счетчик 10 обнуляется, в счетчике 11 сбрасьгоается дополнительный разряд и следует обращение к блоку

А Zoi и &Z,

45

У памяти за величинами , которые помещаются соответственно в регистры 6 и 7. Завершающим действи- ем процесса подготовки к развертьша- нию является передача содержимого регистров 6 и 7 в регистры 4 и 5 соответственно и перевод интерполятора из режима подготовки в режим развер- тьшания соответствующей строки поверхности. Это достигается с помощью .триггеров управления 1 блока, первый из которых отключает первый распределитель, а второй включает второй, и, кроме того, подключает тактовую частоту FJ, к входу счетчика 10 и уп- 55 равляющему входу сумматора 2. Таким образом, в счетчике 10 фиксируется из менение аргумента X , а в сумматоре 2 к начальному значению Z начинают

50

1206805Л

НИКОВ iJ-гокавдрата разбив - , ния.

Для случая,показанного на

чаются соответствующим значением признака Ajj«-- 0,l}, получаем общее выражение для вычисления значения производной на ij-м квадрате разбиения .

(О

1 управления (фиг.З) в соответстка

ВИИ с микропрограммой (фиг.2).

В исходном состоянии (перед гене- 2, рированием функции) в сумматор 2 интерполятора из блока 9 памяти передается начальное значение функции (XQ,уд). Дпя этого блок управления по состоянию а,

присваивает

счетчикам 10 и 11 адрес ячейки памяти, где хранится значение Z. Далее содержимое сумматора 2 передается в ячейку блока 9 памяти, где хранится текущее значение функции в начале строки (.). Адрес этой ячейки задается с помощью дополнительного разряда счетчика 11 (состояния а, . Затем счетчик 10 обнуляется, в счетчике 11 сбрасьгоается дополнительный разряд и следует обращение к блоку

А Zoi и &Z,

У памяти за величинами , которые помещаются соответственно в регистры 6 и 7. Завершающим действи- ем процесса подготовки к развертьша- нию является передача содержимого регистров 6 и 7 в регистры 4 и 5 соответственно и перевод интерполятора из режима подготовки в режим развер- тьшания соответствующей строки поверхности. Это достигается с помощью триггеров управления 1 блока, первый из которых отключает первый распределитель, а второй включает второй, и, кроме того, подключает тактовую частоту FJ, к входу счетчика 10 и уп- равляющему входу сумматора 2. Таким образом, в счетчике 10 фиксируется из менение аргумента X , а в сумматоре 2 к начальному значению Z начинают

прибавляться с частотой F приращения U Zoj или AZoJi-i . За счет это го обеспечивается развертьюание (х,у). Выбор одно из двух регистров 4 и 5, в которые занесены AZoj и u,Zoj , осуществляется с помощью коммутатора 3 и блока 8 сравнения в соответствии с выражением п1. При этом значение признака A-,j хранится в дополнительном разряде вместе с приращением UZ-,j и после выборки его из блока 9 памяти будет находиться в дополнительном- разряде регистра 4. Содержимое этого разряда и подключается ко входам блока 8 сравнения и коммутатора 3.

Параллельно с развертыванием (к,у) на i-M интервале разбие .ния по X обеспечивается чтение приращений uZi + ,,ij и т.е. для следующего интервала, которые помещаются в регистры 6 и 7.

При появлении импульса переполнения (СЧХ - Х| 0j анализируются условия

(CHXiT CO) Л (СЧХ; ) - соответствующее переходу на следующий интервал разбиения по X . В этом случае содержимое регистров 6 и 7 передается в регистры 4 и 5, а процесс развертывания и выборки приращений для следующего интервала разбиения по Л продолжается; - (СчХ. ) Л (СчХ-, ) п-2) - соответствующее переходу на последний ш1тервал разбиения по X . Действия аналогичны предыдушему случаю, яа исключением того, что, в регистр 6

помещается приращение uZj, а на входе БП устанавливается адрес ординаты Z-re (Сч УСД) ;

(СчХ| 0) Л(СчУ| 4 п-1) - соответствующее переходу к развертыванию

следующей строки. Дня этого в СМ2 записывается из блока 9 памяти Z-y-g в регистр 4 содержимое регистра 6 (uZ.j ) осуществляется вычисление нового значения функции в начале следующей строки (состояние а) и за-, пись нового значения Z в БП 9 (состояние а,) . Далее повторяются действия по выбору приращений &Zc3j и UZoj (состояния аJ, а ц и переход к началу развертывания следующей строки (состояние ;

(.СчХ ; ф 0) ( СчУ;) п- 1) - соответствующее окончанию развертьшания по- верхности. В этом случае работа устройства заканчивается-.

л f ф л

(/f УгУчУтУвУю Фиг.1

LCVyj . nj 6П

§, I ГУУЩ. /

8t г PI- -бп

niiiifiiaj Mil III iiiiiiIllMl

fi г

3 ,:

ЧпЧЛРЧ- т ftf;e/ 7 i jSikvj / f /{(

fe L..Ml

/S Уз

ffyji.- /f

| название | год | авторы | номер документа |

|---|---|---|---|

| Интерполятор поверхности | 1980 |

|

SU942040A1 |

| Цифровой квадратичный интерполятор | 1985 |

|

SU1290354A1 |

| Генератор функций | 1984 |

|

SU1241219A1 |

| Интерполятор | 1988 |

|

SU1541557A1 |

| Генератор функций | 1984 |

|

SU1275411A1 |

| Интерполятор | 1987 |

|

SU1413602A1 |

| Устройство для автоматического управления (его варианты) | 1984 |

|

SU1249481A1 |

| Устройство для отображения информацииНА эКРАНЕ ТЕлЕВизиОННОгО пРиЕМНиКА | 1979 |

|

SU842933A1 |

| Круговой интерполятор | 1986 |

|

SU1352461A1 |

| Интерполятор функций двух аргументов | 1984 |

|

SU1247893A1 |

//

6ffOf(

С1)а6нения

Z3

f

X-Xf

ы

| Устройство для формирования монотонных функций двух переменных | 1977 |

|

SU763879A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Интерполятор поверхности | 1980 |

|

SU942040A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-01-23—Публикация

1984-06-21—Подача