Устройство относится к области автома тйкИ; вычислительной техники и может использоваться в системах обработки информации. Известны быстродействующие параллельные аналоге -цифровые преобразователи, где квантование сигнала осуществляется одновременно с помощью набора компараторов, включенных параллельно по отношению к источнику сигнала 1J. К недостаткам подобного типа преобразователей следует отнести удвоение объема оборудоваиия с добавлением каждого нового разряда Известен аналого-цифровой, , преобразователь содержащий п компараторов и 2 - 1 дифференциальных каскадов на транзисторах, первые базы которых подключены к входной клемме преобразователя, а вторые -к резисторному делителю, подключенному к источнику напряже ния смещения, а в каждом разряде прямой выход дифференциального каскада соединен с инверсным выходом соседнего диффершциального каскада и подключен к инвертирующему входу компаратора, к которому через резистор подключен выход источника коллекторного напряжения 2.. К недостаткам подобного АЦП следует отнести недостаточно высокое быстродействие и точность, обусловленные использованием сигнала одной полярности, снимаемого с одного из выходов дифференциальных пар транзисторов и подаваемого на вход порогового устройства. Целью изобретения является повышение быстродействия и точности аналого-цифрового преобразователя. Цель достигается тем, что в аналого-цифро.вой преобразователь, содержащий п компараторов и 2 - 1 дифференциальных каскадов на транзисторах, первые базы которых подключены к входной клемме преобразователя, а вторые - к резисторному делителю, подключенному к источнику напряжения смещения, а в каждом разряде прямой выход дифференциального каскада соединен с инверсным выходом соседнего дифференциального каскада и подключен к инвертирующему входу компаратора, к кото роМу через резистор подключен выход источника коллекторного напряжения, введены п допол37

нительных источников коллекторного напряжения и п дополнительных резисторов, первые выводы которых соединены с выходами п дополнительных источников коллекторного напряжения, а вторые подключены к неинвертирующим входам соответствующих компараторов разряда, а в каждом разряде инверсный выход дифференциального каскада соединен с прямым выходом соседнего дифференциального каскада и подключен к неинвертирующему входу компаратора данного разряда.

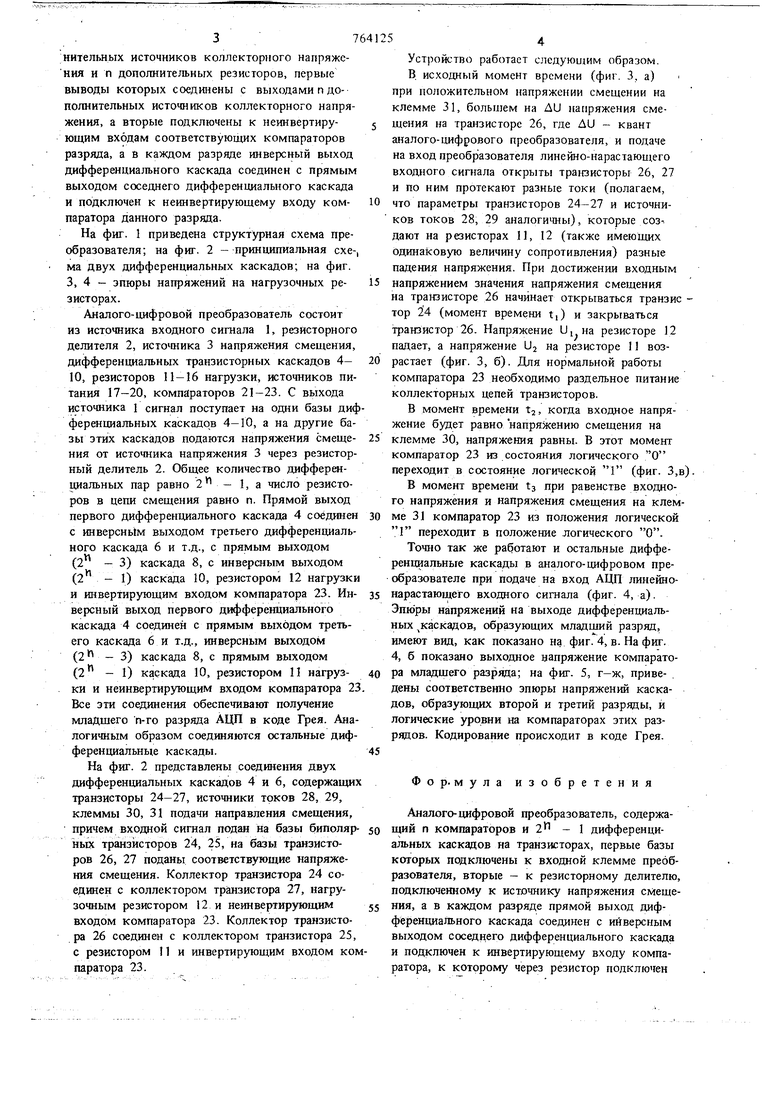

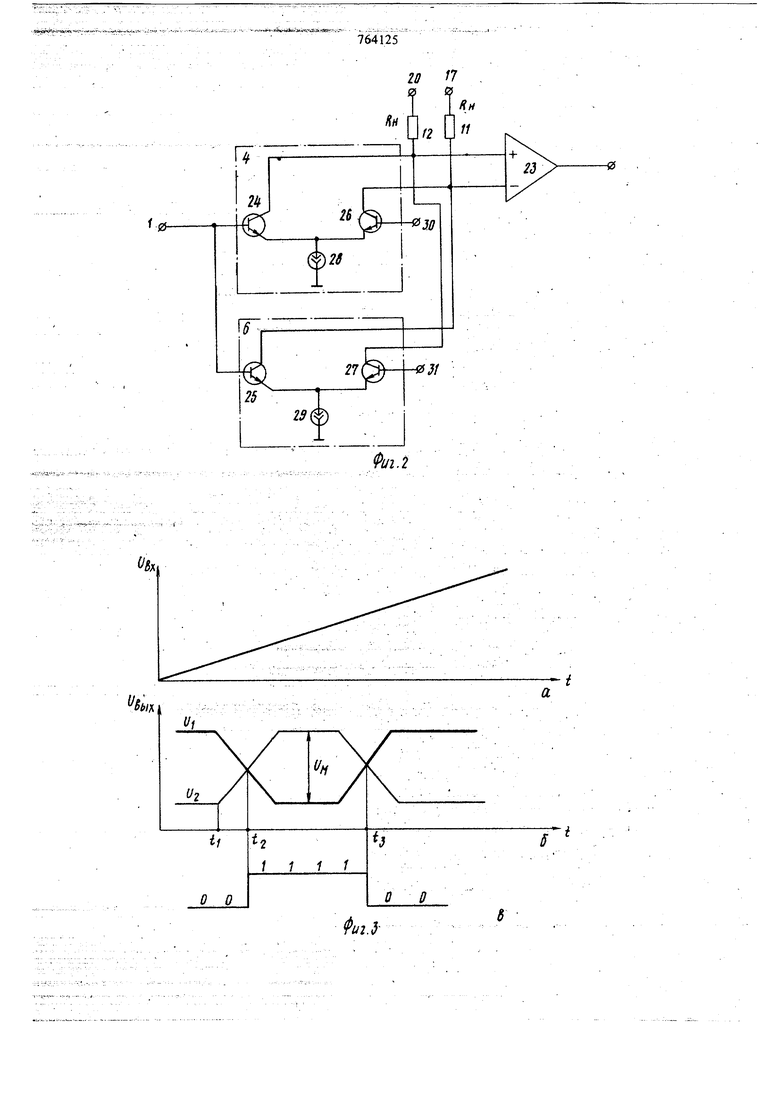

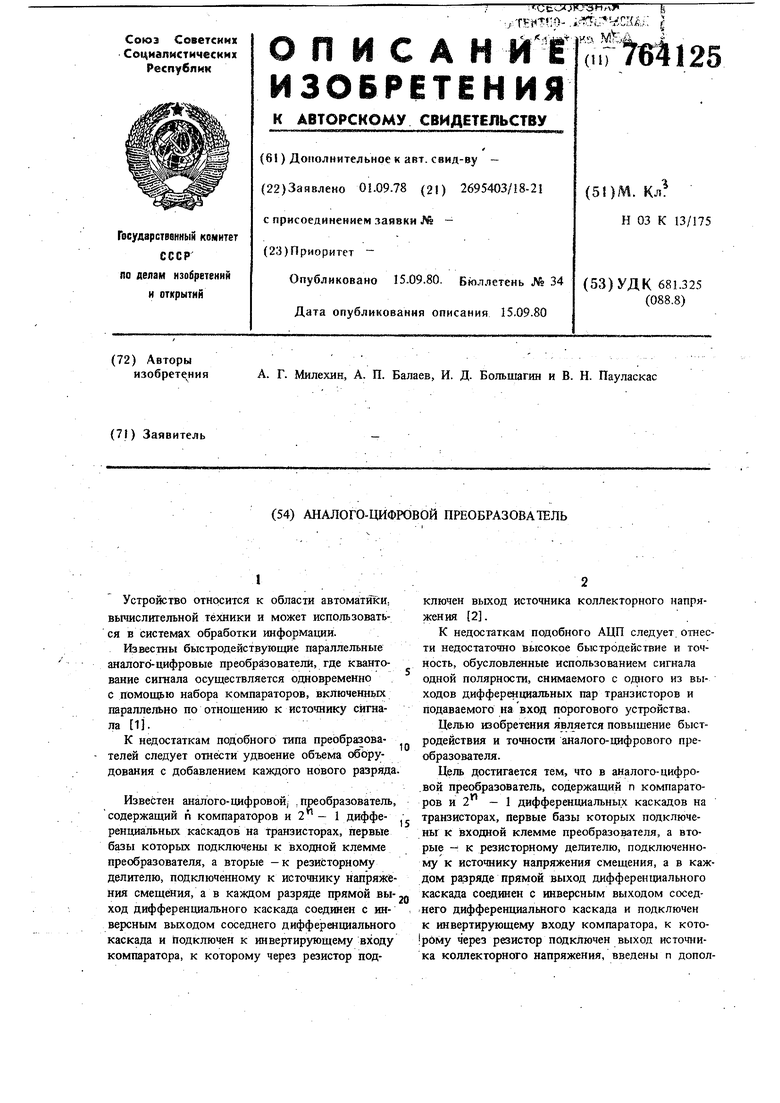

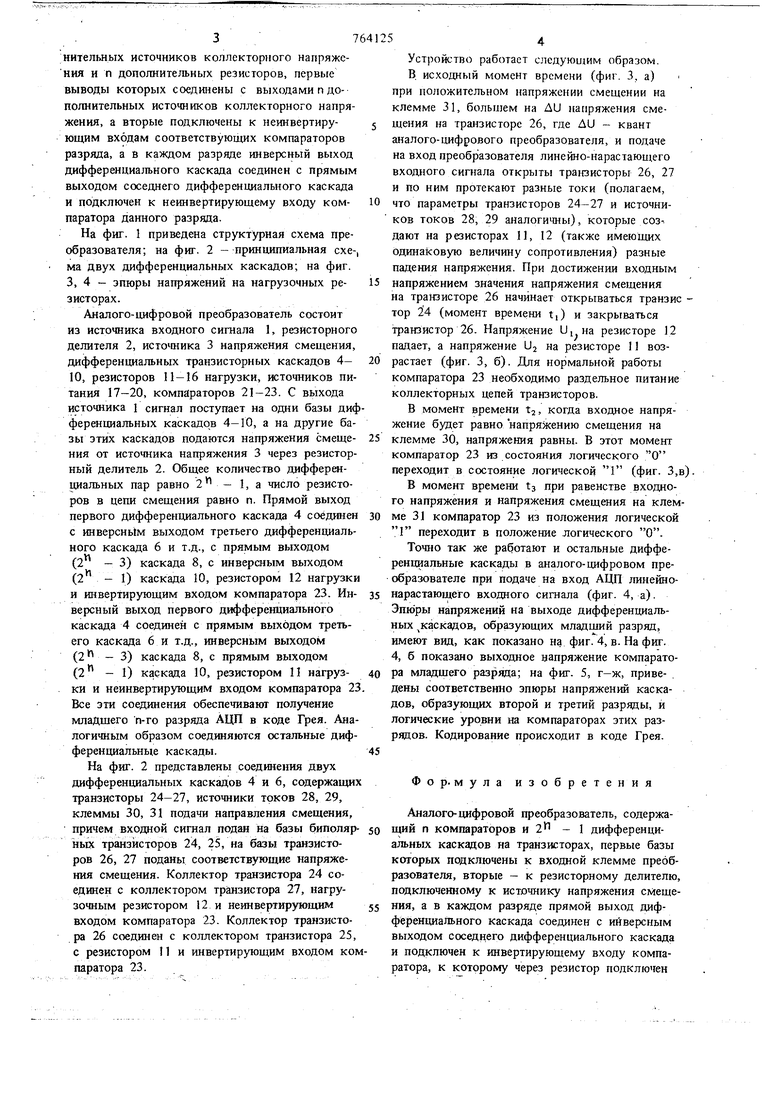

На фиг. 1 приведена структурная схема преобразователя; на фиг. 2 - принципиальная схема двух дифференциальных каскадов; на фиг. 3, 4 - эпюры напряжений на нагрузочных резисторах.

Аналого-цифровой преобразователь состоит из источника входного сигнала 1, резисторного делителя 2, 3 напряжения смещения, дифференциальных транзисторных каскадов 4- 10, резисторов 11-16 нагрузки, источников питания 17-20, компараторов 21-23. С выхода источника 1 сигнал поступает на одни базы дифференциальных каскадов 4-10, а на другие базы этих каскадов подаются напряжения смещения от источника напряжения 3 через резисторный делитель 2. Общее количество дифференциальных пар равно 2 - 1, а число резисторов в цепи смещения равно п. Прямой выход первого дифференциального каскада 4 соединен с инверснь1м выходом третьего дифференциального каскада 6 и т.д., с прямым выходом

3) каскада 8, с инверсным выходом

(2

(2 - 1) каскада 10, резистором 12 нагрузки и инвертирующим входом компаратора 23. Инверсный выход первого дифференциального каскада 4 соединен с прямым выходом третьего каскада 6 и т.д., инверсным выходом (21 - 3) каскада 8, с прямым выходом (2 - 1) каскада 10, резистором II нагрузки и неинвертирующим входом компаратора 23 Все эти соединения обеспечивают получение младшего п-го разряда АЦП в коде Грея. Аналогичным образом соединяются остальные дифференциальные каскады.

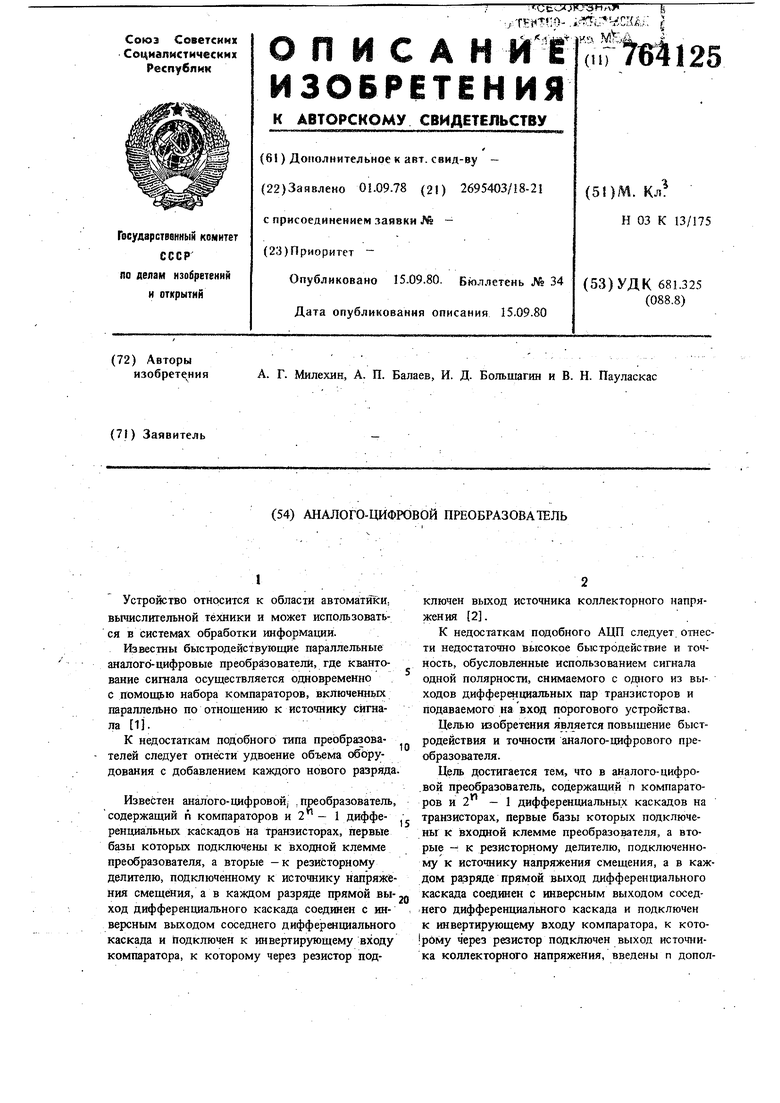

На фиг. 2 представлены соединения двух дифференциальных каскадов 4 и 6, содержащих транзисторы 24-27, источники токов 28, 29, клеммы 30, 31 подачи направления смещения, причем входной сигнал подан на базы биполярных транзисторов 24, 25, на базы транзисторов 26, 27 поданы соответствующие напряжения смещения. Коллектор транзистора 24 соединен с коллектором транзистора 27, нагрузочным резистором 12 и неинвертирующим входом компаратора 23. Коллектор транзистора 26 соединен с коллектором транзистора 25, с резистором 11 и инвертирующим входом компаратора 23.

4

Устройство работает следующим образом.

В. исходный момент времени (фиг. 3, а) при положите.т.ном напряжении смещении на клемме 31, большем на Ди напряжения смещения на транзисторе 26, где Ди - квант аналого-цифрового преобразователя, и подаче на вход преобразователя линейно-нарастающего входного сигнала открыты транзисторы 26, 27 и по ним протекают разные токи (полагаем, что параметры транзисторов 24-27 и источников токов 28, 29 аналогичны), которые создают на резисторах 11, 12 (также имеющих одинаковую величину сопротивления) разные падения напряжения. При достижении входным напряжением значения напряжения смещения на транзисторе 26 начинает открываться транзис тор 2:4 (момент времени t,) и закрываться транзистор 26. Напряжение Ui на резисторе 12 падает, а напряжение U на резисторе 11 возрастает (фиг. 3, б). Для нормальной работы компаратора 23 необходимо раздельное питание коллекторных цепей транзисторов.

В момент времени t, когда входное напряжение будет равно напряжению смещения на клемме 30, напряжения равны. В этот момент компаратор 23 из состояния логического О переходит в состояние логической 1 (фиг. 3,в).

В момент времени tj при равенстве входного напряжения и напряжения смещения на клемме 31 компаратор 23 из положения логической I переходит в положение логического О.

Точно так же работают и остальные дифференциальные каскады в аналого-цифровом преобразователе при подаче на вход АЦП линейнонарастающего входного сигнала (фиг. 4, а). Эпюры напряжений на выходе дифференциальных каскадов, образующих младщий разряд, имеют вид, как показано на фиг. 4, в. На фиг. 4, б показано выходное напряжение компаратора младщего разряда; на фиг. 5, г-ж, приведены соответственно эпюры напряжений каскадов, образующих второй и третий разрады, и логические уровни на компараторах этих разрядов. Кодирование происходит в коде Грея.

Фор. мула изобретения

Аналого-цифровой преобразователь, содержацдий п компараторов и 2 - I дифференциа. каскадов на транзисторах, первые базы которых подключены к входной клемме преобразователя, вторые - к резисторному делителю, подключенному к источнику напряжения смещения, а в каждом разряде прямой выход дифференциального каскада соединен с инверсным выходом Соседнего дифференциального каскада и подключен к инвертирующему входу компаратора, к которому через резистор подключен

выход источника коллекторного напряжется, о т л и ч а К1 in и и с я тем, что, с целью повышения быстродействия и точности устройства, в него введены п дополнительных источников коллекторного напрйжения и п дополнительных резисторов, первые выводы которых соединены с выходами п дополнительных источников коллекторного напряжения, а вторые подключены к неинвертирующим входам соответствующих компараторов разрядов, а в каждом разряде инверсный выход дифференциального каскада соединен с прямым выходом со седнего диффершциального каскада и подключен к неинвертирующему входу компаратора данного разряда.

Источники информации, принятые во внимание при экспертизе

1.Бахтияров Г. Д. и др. Аналого-цифровые преобразователи. Зарубежная радиоэлектроника, 1975, № I.

2.Патент Японии N 51-39508, кл. D 98 (5) F 1 (прототип).

Г7

2«

.

10.

10 /7

KH 11

n

fj 0

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1980 |

|

SU921075A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU828404A1 |

| Аналого-цифровой преобразователь с компенсационным интегрированием | 1986 |

|

SU1432773A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU815902A1 |

| Транзисторный ключ с защитой от перегрузки | 1986 |

|

SU1348993A1 |

| Импульсный стабилизатор постоянного напряжения | 1990 |

|

SU1712945A1 |

| ПИКОВЫЙ ДЕТЕКТОР | 2009 |

|

RU2409818C1 |

| Аналого-цифровой преобразователь последовательного приближения | 1981 |

|

SU1018228A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ЦИФРОВОЙ КОД ОТКЛОНЕНИЯ | 1992 |

|

RU2074396C1 |

| Стробируемый компаратор напряжения | 1988 |

|

SU1628194A1 |

В 0 ГТ 1 f T 0 0

(/,

(/2

0000 If, ; 7i/«J

Ж

J

Авторы

Даты

1980-09-15—Публикация

1978-09-01—Подача