Гж:

шашщей способности и снижение входного тока. Введение в стробируемый компаратор второго дифференциального каскада t1 позволяет значительно гни- зить входные токи первого дифференциального каскада 1 и увеличить его коэффициент усиления в р ежиме слел -нчя. а в режиме запоминания - коэффициент усиления в цепи положительной обрат- ной связи. В результате этого повышается разрешающая способностьс Громе того, стробируемый компаратор напряжения содержит первую и вторую динамические нагрузки 2, 3, два буферных каскада 4, 5, третья и четвертая динамические нагрузки 6, 7, два элемента 8, 9 смещения, стробируемый дифференциальный каскад 10, динамические нагрузки 12, 13, 16 и 17, третий и четвертый элементы 14, 15 смещения, две шины 18, 19 питания, входную шину 20, шину 21 опорного напряжения, выходные шины 22, .23, строби- рующую шину 24. 2 ил

| название | год | авторы | номер документа |

|---|---|---|---|

| БИПОЛЯРНО-ПОЛЕВОЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2583760C1 |

| ОПТИЧЕСКИЙ ПЕРЕДАТЧИК | 2018 |

|

RU2677112C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2015 |

|

RU2613842C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ «ПЕРЕГНУТОГО» КАСКОДА И КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРОВ | 2022 |

|

RU2773907C1 |

| Буферный усилитель на К-МОП транзисторах | 1984 |

|

SU1220118A1 |

| Широкополосный стробоскопический преобразователь | 1984 |

|

SU1250962A1 |

| КМДП-компаратор с регенерацией | 1988 |

|

SU1614106A1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННОЙ КРУТИЗНОЙ НА ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2021 |

|

RU2770915C1 |

| Операционный усилитель | 1989 |

|

SU1695491A1 |

| ДВУХТАКТНЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2390909C1 |

Изобретение относится к нмпульс- ноп технике и может быть использовано в радиотехнических устройствах, в частности в универсальном испытательном оборудовании контроля параметров цифровых интегральных схем, в скоростных аналого-цифровых преобразователях. 1ель изоРретения - повышение раяре«-Ј

Изобретение относится к импульсной технике и может быть использовано в радиотехнических устройствах широкого назначения, в частности, в универсальном испытательном оборудовании контроля параметров сверхскоростных цифровых интегральных схем для оценки отклика испытуемого узла tn стимулирующее воздействие, в ана заторах логических состояний дчя регистрации изменения логического состояния в исследуемом узле циг-j вого блока, в скоростных аналого- цифровых преобразователях и т„д.

Цель изобретения - повышение разрешающей способности за счет увели- чения коэффициента усиления и снижение входного тока.

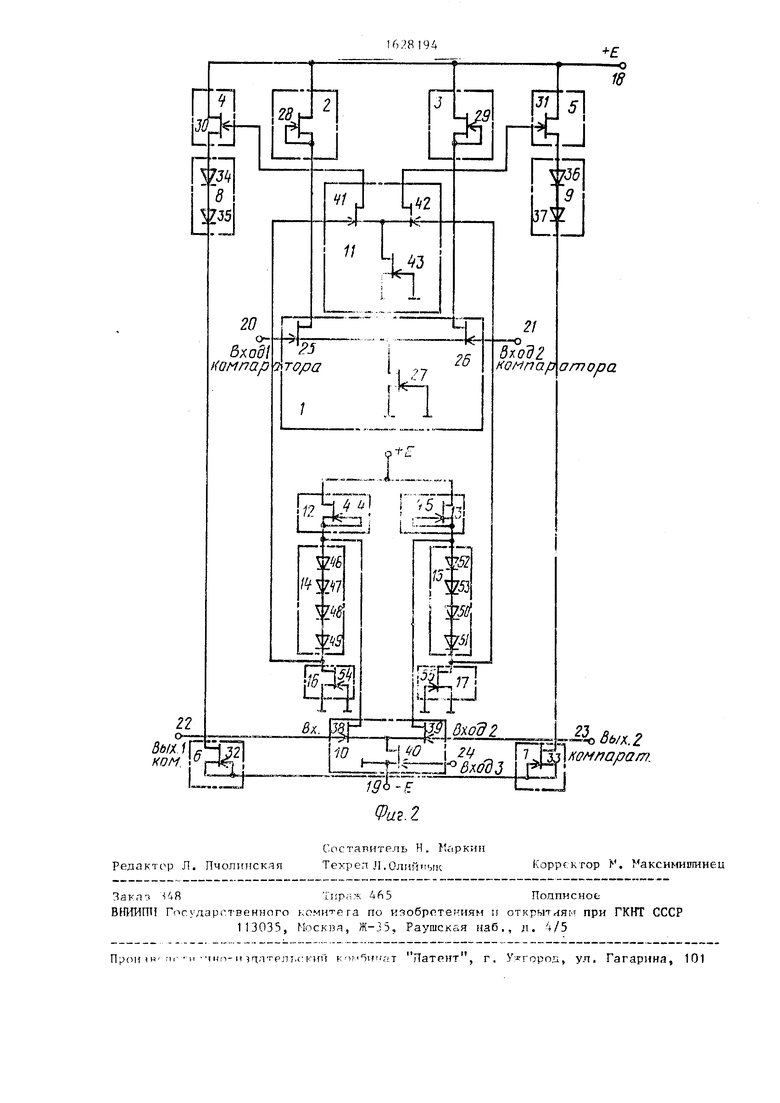

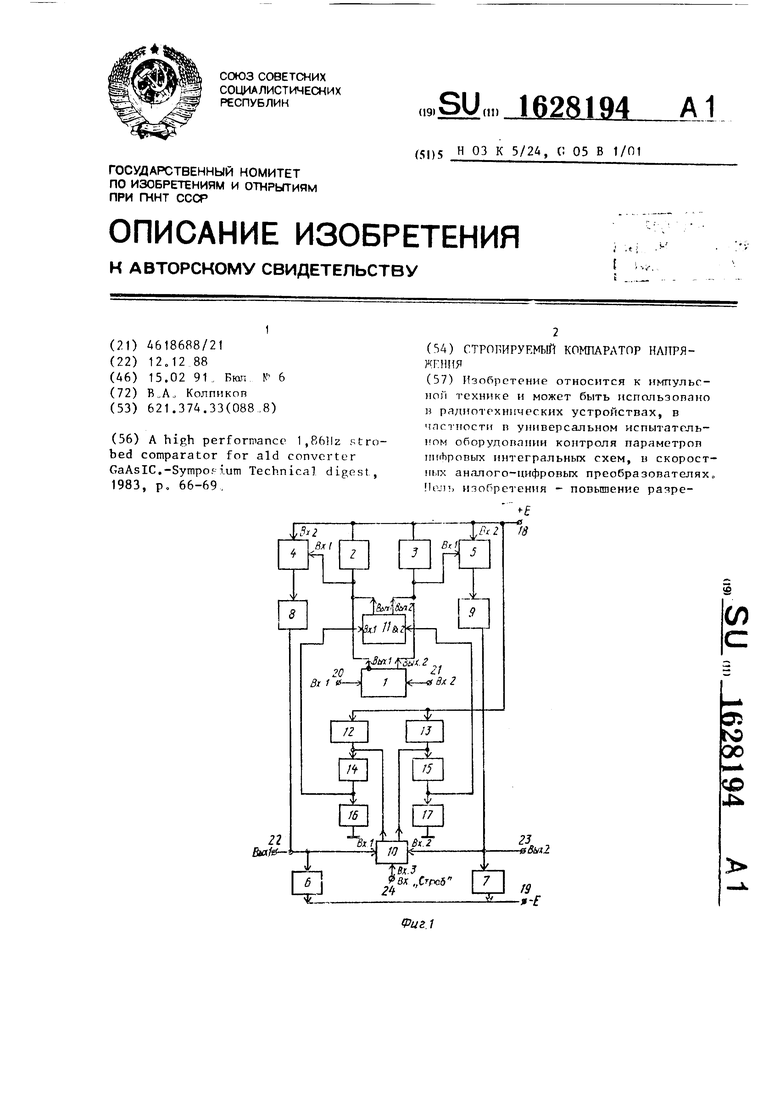

На фиг. 1 представлена блок-схема стробируемого компаратора напряжения; на фиг„ 2 - одна из его технических реализаций

Стробируемый компаратор напряжения содержит первый дифференциальный каскад 1, первую 2 и вторую 3 динамические нагрузки, два буферных каскада 4 и 5, третью 6 и четвертую 7 динамические нагрузки, два элемента 8 и 9 смещения, стробируемый дифференциальный каскад 10, второй дифференциальный каскад 11, две динамические нагрузки 12 и 13 стробируемого диф- Аеренциального каскада, третий 14 и четвертый 15 элементы смещения, динамические нагрузки 16 и 17 третьего 14 и четвертого 15 элементов смещения первую 18 и вторую 19 шины питания, входную шину 20, шину 21 опорного напряжения, выходные шины 22 и 23 и стробируюшую шину 24, при -этом вхо5

0

35

40

45 50 55

ды дифЛеренциатьного каскада I подключены соответственно к входной шине 20 (вх. 1 компаратора) и опорной шине 21 (вх. 2 компаратора) устройства. Динамические нагрузки 2 и 3 включены между первой липой 18 питания +Е и инвертирующим и неинвертируючгим выходами первого дифференциального каскада 1, Вторые входы первого 4 и второго 5 буферных каскадов подключены к первой шине 18 питания тЕ, а их первые входы - к инвертирующему и неинвсртиру- шщему выходам первого дифференциального каскада 1. Первый 8 и втором 9 элементы смещения уровня напряжения включены между выходами первого 4 и второго 5 буферных каскадов и первой 22 и второй 23 выходными шинами устройства. Выходы первой 6 и второй 7 динамических нагрузок буферных кс с- кадов подключены к второй шине 19 питания - Е, а их входы - к первой 22 и второй 23 выходным шинам устройства. Первый и второй входы отро- оируемого дифференциального каскада 10 подключены к выходным шинам 22 и 23 устройства, а его третий вход - к шине 24 стробирования устройства (Ех„ 3). Первая 12 и вторая 13 динамические нагрузки стробируемого дифференциального каскада 11 включены между первой шиной 18 питания +Е и инвертирующими выходами стробируемого дифференциального каскада 10 для его 1 ервого и второго входов. Третий 1- и четвертый 15 элементы смешения уровня напряжения включены между выхотами динамических нагрузок 12 и 13 пробируейогс дифференциального каскяпа 10 и входами дннамичес

ких нагрузок 16 и 17 третьего 14 и четвертого 15 элементов смешения уроп ня напряжения, к которым подключены первый и второй входы второго дифференциального каскада 11. Выходы динамической нагрузки 16 и 17 третьего 14 и четвертого 15 элементов смещения уровня напряжения подключены к общем шине устройства Инвертирующие для первого и второго входов выходы второго дифференциального каскада 11 подключены к инвертирующему и нгиняег тирукяцему выходам первого дифЛерен- циального каскада 1 соответственно.

Описание работы компаратора приведено для варианта по схеме Фиг. 2

В этой схеме первый дифференциальный каскад 1 выполнен на транзисторах 25-27, динамические нагрузки и 1 - на транзисторах 28 и 29 в диодном включении, буферные усилители 4 и 5 - на транзисторах 30 и 31, динамические нагрузки 6 и 7 - на транзисторах 32 и 33, элементы 8 и 9 смещения - на последовательно соединенных диодах 34, 35 и 36, 37 соответственно, стро- биру-емый дифференциальный каскад 10 - на транзисторах 38-40, второй дифференциальный каскад 11 - на трапписто- рах 41-43, дина гические нагрузки 12 и 13 - на транзисторах 44 и 45 в диодном включении, третий 14 и четвертый 15 элементы смещения - на последовательно включенных диодах 46-49 и 50- 53, динамические нагрузки 16 и 17 - на транзисторах 54 и 55 в диодном включении.

Компаратор работает следующим образом.

В режиме слежения компаратора напряжение на шине 24 стробирования

истрое-ив где ио напряжение отсечки транзистора 40. В этом случае транзисторы 38 и 39 стробируемого дифференциального каскада 10 не активны и на затворах транзисторов 41 и 42 второго дифференциального каскада 11 устанавливаются одинаковые напряжения, величины которых больше максимального входного напряжения компаратора. Второй дифференциальный каскад 11 осуществляет токовую подпитку динамических нагрузок на транзисторах 28 и 29 первого дифференциаль- ного каскада 1, , предварительно устанавливает рабочую точку динамических нагрузок первого дифференциального каскада 1 в крутой области их

162810

5

5

0

5

0

5

0

5

0

вольт-амперных хярактеристин.При одинаковых напряжениях на входах компаратора (на входах первого дифференциального каскада) Ивм U 6Х через динамические нагрузки на транзисторах 28 и 29 дополнительно протекают токи первого дифференциального каскада 1, которые устанавливают рабочую точку динамических нагрузок на пологой ветке ее вольт-амперной характеристики. Таким образом, в первом дифференциальном каскаде 1 устанавливается режим наибольшего усиления, а в компараторе - режим максимальной разрешающей способности. При изменении напряжения на одном из входов компаратора, например Ч8Х , URX + &1I, где UU - величина изменения напряжения, происходит перераспределение токов в транзисторах 25 и 26 первого дифференциального каскада 1: ток в транзисторе 25 увеличивается, а в транзисторе 26 уменьшается, Это приводит к изменению падений напряжения на динамических нагрузках первого дифференциального каскада 1: возрастает падение напряжения на динамической нагрузке на транзисторе 28 и уменьшается падение напряжения на динамической нагрузке на транзисторе 29. При этом уменьшается напряжение сток-исток транзистора 41 второго дифференциального каскада 11 и его рабочая точка перемещается в крутую область его вольт-амперной характеристики Следствием этого является уменьшение величины тока подпитки динамической нагрузки на транзисторе 28 и стабилизация падения напряжения на ней, в то время как рабочая точка траьзистора 25 первого дифференциально: о каскадл 1 компаратора находится на пологой ветке его вольт- амперной характеристики„ Таким образом, введение в прототип второго дифференциального каскада 11 на транзисторах 41-43 позволяет значительно снизить входные токи первого диФЛе- ренциального каскада 1, а значит, и входные токи компаратора и увеличить его коэффициент усиления в режиме слежения.

В режиме запоминания компаратора напряжение на шине 2Д стробирования U строБ а 0, При этом открывается транзистор 40 и активизируются транзисторы 38 и 39 стробируемого дифференциального каскада 10. Транзисторы 38 и 39 стробируемого дифференциального каскада 10, динамические нагрузки на транзисторах 44 и 45 стрпбируе- мого дифференциального каскада 10, третий 14 н четвертый 15 плементы, уровня смещения напряжения на диодах 46-49 и 50-53, второй дифференциальный каскад 11 на транзисторах 41-43, динамические на транзисторах 28 и 29 первого днфферен-- циапьного каскада 1, первый и второй буферные каскады на транзисторах 3D и 31, первый 8 и второй 9 элементы смещения уровня напряжения па диодах 34, 35 и 36, 37 образуют триггер с за кцутой положительной обратной связью Например, если в режиме гчежения компаратора его входные напряжения U&V I 1 е г. 1 тогда PI о выходные напряжения иеыу t gbiKZ- fP переходе в режим запоминания компаратора транзистор 38 стробируемого дисЬференциапь ного каскада 10 начинает закрываться, а транзистор 39 - открываться Падение напряжения на динамической нагруз на транзисторе 44 стробируемого дифференциального каскада 10 уменьшается, а на динамической нагрузке на транзисторе 45 увеличивается, Тто приводит к открыванию транзистора 39 второго дифференциального каскапя 11 и закрыванию транзистора 42 ттого каскадаt Ток подпитки динамической нагрузки на транзисторе 28 первого дифференциального каскада 1 увепичи- влется, а ток подпитки динамической нагрузки на транзисторе 29 первого дифференциального кгскада 1 уменьшается о Это вызывает увеличение падения напряжения на динамической нагрузке, на транзисторе 28 первого днфЛерен- 1гиального каскада 1 и уменьшение падения напряжения на динамической нагрузке на транзисторе 29 первого дпсЬ- ференциального каскада 1, а также уменьшение напряжения сток-исток транзистора 41 второго дифференциального каскада 11 и увеличение напряжения сток-исток транзистора 42 этого каскада. Таким образом, происходит еще большее уменьшение выходного напряжения UBbix.i и увеличение напряжения U бык.2 „ При дальнейшем уменьшении напряжения UBb|Xi1 и увеличении напряжения иВЬ1Х12 происходит уменьшение напряжения сток-исток каскада на транзисторах 30 и 31, первый 8 и второй 9 элементп смещения уровня напряжения на диодах 34-37 образуют тригiер с замкнутой положительной обратной связью Например, если в режиме слежения компаратора его входные напряжения И ах 1 твх. г тогда его выходные напряжения U Вь|( , l 6tix,2« При перехоле в режим запоминания компаратора транзистор 38 стробируемого дифференциального каскада 10 начинает закрываться, а транзистор 39 - открываться. Падение напряжения на динамической нагрузке на транзисторе 44 стробируемого дифференциального каскада 10 уменьшается, я на динамической нагрузке на транзисторе 45 увеличивается Это приводит к открьшанию транзистора 41 второго дифференциального каскада 11 и закрыванию транзит 42 этого каснач.а. То: подпитки динамической нагрузки на транзисторе 28 первого дифференциального каскада 1 увепичивается, а ток подпитки динамической нагрузки на транзисторе 29 первого дифференциального каскада 1 уменьшается. Это вызывает увеличение падения напряжения на динамической нагрузке на транзисторе 28 первого дифференциального каскада 1 ) уменьшение п 1г1ения напряжения на динамической нагрузке на транзисторе 29 первого дифференциального каскада 1, а также уменьшение напряжения сток исток транзистора -, второго дифференциального каскада 11 и увеличение напряжения сток-исток транзистора 42 этого каскада Таким образом, происходит еще большее уменьшение выходного напряжения Ue,bix,, и увеличение напряжения Ирь|)(. , . При дальнейшем уменьшении напряжения Ugbtx и увеличении напряжения происходит уменьшение на яжения сток-исток транзистора 41 второго дифференциального каскада 11. При этом его рабочая точка перемещается из пологой области в крутую область РГО вольт-амперной характеристики, ограничивая изменение токов транзисторов 41 и 42 второго дифференциального каскада 11 и, соответственно, напряжений на выходе компаратора„ Таким образом, положительная обратная связь фиксирует схему в состоянии, в котором она находилась в момент открывания транзнстрра АО (и8ЫУф, 1W ( ил ивых.| иВЬ1М)„ Но при этом рабочая точка транзистора 23 первого дифференциального каскада находится в пологой области его вольт-амперной характеристики и его

напряжение затвор-исток отрицательно Поэтому отсутствует ток затвора 1ран- знстора 23 первого дифференциального каскада компаратора и его входной ток определяется только током утечки затвора,

. Кроме того, введение второго дифференциального каскада 11 на транзисторах 41-43 позволило увеличить в режиме слежения компаратора транзистора 41 второго дифференциального каскада 11. При этом его рабочая точка перемещается из пологой области в крутую область его вольт-амперной характеристики, ограничивая изменение токов транзисторов 41 и 42 второго дифференциального каскада 11 и, соответственно, напряжений на выходе компаратора. Таким образом, положительная обратная связь фиксирует схему в состоянии, в котором она находилась Р момент открывания транзистора 40 О вых.1 1 вы г или 1:0ых,1 U..,„„), Но при этом рабочая точка

В Ы -Z

транзистора 23 первого дифЛеренцилль ного каскада находится в пологой области его вольт-амперной характеристки и его напряжение затвор-исток отрицательно. Поэтому отсутствует ток затвора транзистора 23 первого дшь- ференциального каскада компаратора и его входной ток определяется тольк током утечки затвора.

Кроме того, введение второго дифференциального каскада 11 на транзисторах 41-43 позволяет увеличить в режиме слежения компаратора коэффициент усиления первого дифференциального каскада на транзитторс 25- 27, а в режиме запоминания комплратора - коэффициент усиления в цепи положительной обратной связи, В результате этого повышается разрешающая способность компаратора„

Формула изобретения

Стробируемый компаратор напряжения, содержащий стробируемый дифференциальный каскад, два элемента смещения уровня напряжения, два буферных каскад 50 с динамическими нагрузками и дифференциальный каскад с динамическими

0

Q . 5

,.

5

0

5

0

нагрузками, включенными соответственно между первой шиной питания компаратора напряжения и инвертирующим и неинвертирующим выходами дифференциального каскада, первый вход которого подключен к входной шине компаратора напряжения, а второй вход - к шине опорного напряжения компаратора напряжения, первые входы первого и второго буферных каскадов подключены соответственно к инвертирующему и неинвертирующему выходам дифференциального каскада, а вторые входы - к первой шине питания компаратора напряжения, элементы смещения уровня напряжения включены соответственно между выходами буферных каскадов и выходными шинами компаратора напряжения, к которым подключены соответственно входы динамических нагрузок буферных каскадов, выходы которых соединены с второй шиной питания компаратора напряжения, первый и второй входы стробируемого дифференциального каскада подключены к выходным шинам соответственно, а третий вход подключен к шине стробирования компаратора напряжения, отличаю- щ и и с я тч М, что, с целью повышения разрешающей способности, снижения выходного тока, в него впечены второй дифференциальный каскл;т и две цепочки, каждая из каторг.-, состоит m последола /ельно сосдиненшгх динамической нагрузки cTpo6npvevoro дифференциального каскада, г темента смещения уровня напряжения и его динамической нагрузки, выход каждой из которых подключен к общей шине компаратора нгпряжения, а к входам подключены соответственно первый и второй входы второго дифференциал ь- ного каскада, выходы которого соединены соответственно с инвертирующим и неинвертирующим выходами первого дифференциального каскада, входы динамических нагрузок стробируемого дифференциального каскада подключены к первой шине питания компаратора напряжения, а к выходам подключены соответственно инвертирующие выходы стробируемого дифференциального каскада.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для соединения пучка кисти с трубкою или втулкою, служащей для прикрепления ручки | 1915 |

|

SU66A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1991-02-15—Публикация

1988-12-12—Подача