1

Изобретение относится к вычислительной технике и может быть использовано при построении устройств перера-ботки двоичной информации на цилиндрических магнитных доменах (ЦМД).. 5

Известен мно1 оразрядн,ый .рвоичный комбинационный сумматор (МДКф содержащий слой магнитооднооснб о материала с ЦМД, на поверхности которого расположёны логические.элементы 10 (ЛЭ), аннигиляторы и генераторы ЦМД и каналы продвижения ЦМД ij. .

Недостатком этого МДКС является его относительная сложность.

Наиболее близким к изобретению 15 является МДКС, который содержит слой магнитоодноосного материала с ЦМД/ на поверхности которого расположены Р (где Р - число разрядов операндов) основных логических эле- 20 ментов И-исключающее ИЛИ с двумя входами и тремя выходами, второй вход каждого из которых соединен с соответствующими каналами ввода операндов, а третьи выходы взаимосвяза- 25 ны с аннигиляторами ЦМД, и выходной регистр, сое.цинвнный с перввви выходом основного логического элемента И - исключающее ИЛИ младшего разря да С23;Недостатками этого сумматора являются невысокое быстродействие, составляю&хее (Р+3,5) такта при сложении Р-разрядных операндов (такт время одного полного оборота вектора магнитного поля управления), а также последовательная форма представления результата сложения при параллельной форме представления операндов .

Цель изобретения - повышение быстродействия МДКС.

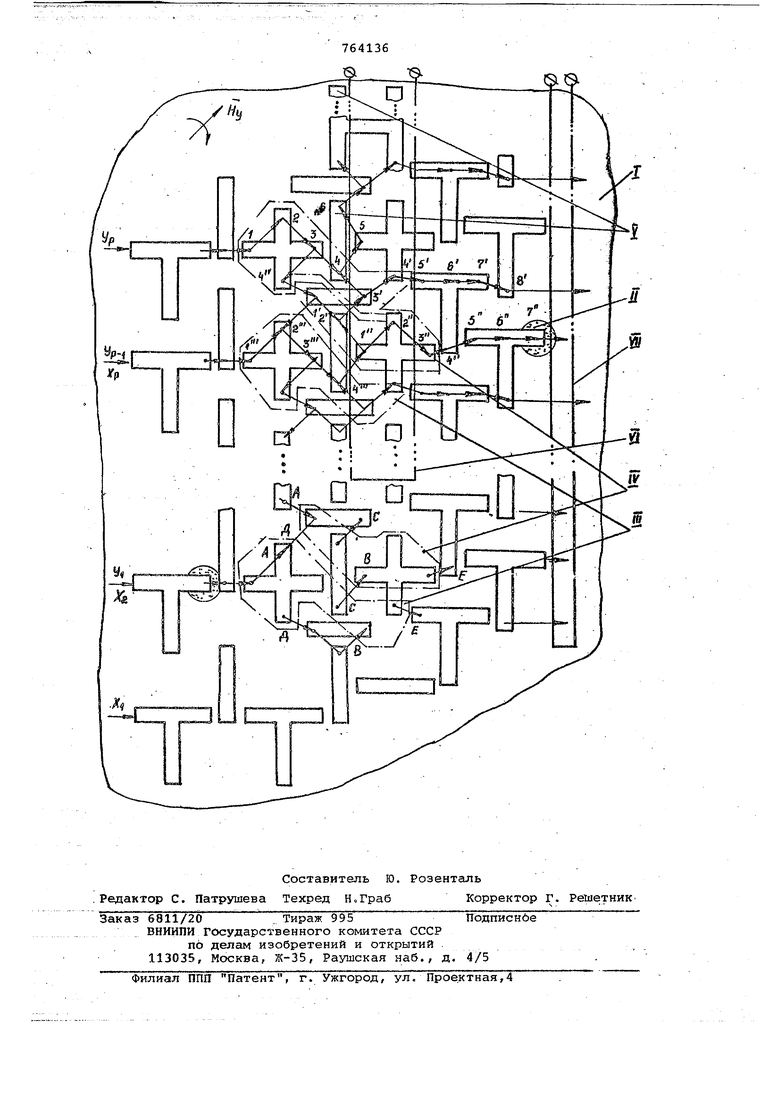

Поставленная цель достигается, тем, что МКДС соДержит Р-1 дополнительный ЛЭ И-исключающее ИЛИ, каждый из которых расположен между смежными основными логическими элементами (ОЛЭ) И-исключакнцее ИЛИ, и токовую шину магнитосвязанную с Р/2, если Р - четное число, или Р-1/2,если Р - нечетное число, ОЛЭ И-исключающее ИЛИ младших разрядов и выходным регистром, причем первый вход ОЛЭИисключающее ИЛИ старшего разряда соединен со вторым выходом того жё элемента, первый вход и второй выход каждого ОЛЭ И-исключающее ИЛИ и каждого из ДЛЭ И-исключающее ИЛИ соединены соответственно с первым выходом и вторым входом предьщущего. длэ Й-й 5ключЪю1цее ЙЯЙ и п1редед . ОЛЭ И йсключающее ИЛИ, третий вы- ,, ход каждого ДЛЭ И-исключающее ИЛИ с р едйМед с антагилятором ЦМД, а ти1а выход каяодого из бЛЭ Й-йсклю чающее ИЛИ через аннигилятор ЦМД боединей с сортветствующим выходом су№1атора. .. . на. чертеже изображена принципиаль ная схема предложенного МДКС... МКДС содержит слоймагнитродноос,ного материала 1 с ЦМД i),,на пове рхноОтИ которого расположены ОЛЭ Ш .и ДЛЭ 5 И-исключающее ИЛИ с двумя входамиИ TlSeiviiH 1йходами, на первом йзПШё 1Г1$ШШ 11Ш пё|ШШШа 1ель ная функция (ПФ)неравнозначность,., а На втором и третьем - ПФ КонъйнкД1ИЯ, выходной регистр., токовая и.аннигиляторы ЦМД :vЦифрами 1,2,3 ; и т. д. обозначены позиции, занимаемые ЦМД во время их прохождения внутри сумматора, а буквами Х. и У Т с 58:Ф1гё &твуйЩиё )а&рйды и 11|ШШШЙ;Шё поступают. Работа МДКС протекает следующим , образом.;:: .v;.. ; . ; -;.- ;. На параллельные входы Х, У,, ...,, Ур-1 , Хрсумматора поступают разряды Ху (1 К Р|:первОгр операнда, с ;адержкой на такт на входы У, Х|,.. yp.yJXpJ Ур сугФ атора поступают разряды Уу втЬрйгОЬпёранда, причём -Йтаршйе первого и второго :°Ш1 1ШН Йос упШ|Т на входы 5(и.У(, Ул.Чбрёз 1,5 tакта с й эмёнта поступления первого операнда на входы МДКС рба сп а1 а1емых сводят ЬГ1 а:э1рЯд к Шзряду на расстояние, доетаточное для взаимодействия ЦМД в ОЛЭ их бдноименйых разрядов. В тече ние первого полутакта, прошедшего с момента сближёййгй операндов, в результате взаимодействия доменов н vfecfe первого иэ них остается сЛоао - ч тетШййзг сумм, но сдвинутое на пол - р-|ГэЭя в-стороМуйШ1да1ВГрКЭ|5й-до-в ЙКДС по отношению к своему начально му положению. На месте второго операнда к этому времени остается слов переносов, сдвинутое на полразряда в сторону старших разрядов i Мдй; по бЧНошенйю к своему начгшьному поло жению, в за полтакта, прошедшего с начала суммирования, слово чаЬти 1НЫХ сумм сдйинулсйь tio отнсяие к слову переносов так одноименные разряда сблизили на 1расстоянйе,; 6статд й&едля взаимодействия в них доменов ,аходящихся ДЛЭ. В течение второ )поГл $гтакта первого такта слож|егая слЪво. частичных угШ переьтЪ Жразрядного суммирования по модулю 2 взаимодействует с ЦМД слова перенос в ДЛЭ, в результате чего образуется новое слово 4acjrH4Hict cy№i и новое слово переносов , сдйинутыед0уг от ; носительно друга на разряд так, что ЦМД их одноименных разрядов сблизились для взаимодействия в ОЛЭ. Продесс суммирования завершается в моЙШт времени, когда слово переносов обращается в ноль. В течение всего процесса суммирования ЦМД неиспользуемых переносов с соответствующих выходов ОЛЭ и длэ уничтожаются аннигилятором ЦМД 1, Токовая шина VI необходима для инициирования вывода рез льтата суммирования в параллельной форме через выходы Р/2 младших ОЛЭ| и из выходного регистра. В этом чаеимпуя с стирания в аннигилятор ( не подается и результат суммирования не уничтожается. . Процесс образования результата сложения и переноса в более старший разряд рассмотрим подробно на при- . мереР-го ОЛЭ и 1Р-1)-го ДЛЭ. В момент времени, когда ЦМД, соответствукмций Р-му разряду второго операнда, поступа ет на вход Р-го ОЛЭ (позиция 2), ЦМД, собтветствуннций Р-му. разряду первогб операнда, поступает на другой вхЬд Р-го ОЛЭ (позиция 7) . Отслеживай полисаf возникающие на концах аппликаций под действием магнйтногр поля управления, иш, перемещаются по каналам 2-3 и 2-3 соответ ственно. 5S взаимного отталкивания ЦМД И.З позиций 3 и 3 перейдут, в позиции 4 и 4. соответственно, реализуя тем самым перенос в болёе, старший (Р-1)-ый разряд (позиция 4 1 и ноль на выходе Р-гр ОЛЭ (позиция 4), цВД не1й№1Шльэуё1 01 о переноса из позиции 4 по каналу -б;;7-8 поступает в аннигилятор доменов WPi При нгшичии переноса .в более старцшй разряд ЦМД из позиции 4 /выход Р-го ОЛЭ/.поступаёт в позицию Г (вход (Р-1)-го ДЛЭ}, откуда, взаимодействуя с ЦМД (P-l)-го разряда cJibfia частичных сумм, появляющегося в позиции l (вход (Р-1)-to ДЛЭ) из позиции (выход (Р-1)-го ОЛЭ), поступит в позицию 2 (вход ()-го ( :ОЛЭ), 1; ёаШиЭуй т еж eaMiaM перенос в ,стаЕЯ11ий (р-2)-ой разряд сумматора и Ho;iib на выходе (Р-1) -го ДЛЭ (позиция 2 ) / щед неиспользуемого переноса из позиции l постурт1т в позицию и по каналу - 3-4 - 5 б - в анни.гилятор ЦМД .yib Если в Р-ом разряде одного из двух операндов ЦМД отсутствует, то присутствующий в Р-С)М раГзрядё другого Ъпё ранда ЦМД, не испытывая отталкивающего воздействий, ИЗ позиции 3 (или з ) ч1& « ёТй6рть такта поступит в позицию 4, 1с)ёалйзуя тем самым единицу на выходе Р-го ОЛЭ. nepeH itfSW«aM случае-равен йулю, так как ЦМД в позиции поступает. Если же Щ4Дпбяйй Сй толькЬ на рднрм из входов (Р-1)-го ДЛЭ (в позиции l или же в позиции 1) то, не испыты : вая отталкивающеговоздействия второго ЦМД, он переместится в позицию 2, регшизуя единицу на выходе ДЛЭ и отсутствие переноса в более старший разряд (позиция 2), Случай с двумя нулями, поступающими на входы ЛЭ, не рассматривается ввиду тривиальности .ситуации. Быстродействие выполнения операци суммирования двух Р-разрядных опера дов в предложенном МДКС составляет 0,5 (Р+3) такта(1,5 такта для сближения операндов и О,5 Р тактов на выполнение сложения), что в (Р+3,5)/ /0,5 (Р+3) раз превосходит аналогичный показатель известного устройства Формула изобретения Многоразрядный двоичный ксмибинацйонный сумматор, содержащий слой магнитоодноосного материала с цилиндрическими магнитными доменами. на поверхности которого расположены Р (где Р - число разрядов операнд основных логических элементов И исключающее ИЛИ с двумя входами и тремя выходами, второй вход каждого из которых соединен .с соответствуюищми Каналами ввода операндов, а третьи выходы взаимосвязаны с аннигиляторами цилиндрических магнитных доменов, и выходной регистр, соединенный с первым выходом основного логического элемента И-исключающее ИЛИ младшего разряда, отлича щ и и с я тем, что, с целью повышения быстродействия, он содержит Р Г дополнительный логический элемент И-исключанхцее ИЛИ, каждый ид которых расположен между смежш «с основными логическими элементами Иисключающее ИЛИ, и токовую шину, магиитосвязанную с РХ2, если Р четное число, или Р -1/2, еслиР- нечетное число, основными логическими элементами И-исключающее ИЛИ младших разрядов и выходным регистром, причем первый вход основного логического элемента И-исключающее ИЛИ старшего разряда соединен со вторым того же элемента, первый вход и второй выход каждого основного логического элемента И-исключающее ;ИЛИ и каждого из дополнительных логических элементов И-исключающее ИЛИ соединены соответственно с первым выходом и вторым входом предыдущего дополнительного логического элемента И-исключающее ИЛИ и предыдущего основного логического элемента И-исключающее ИЛИ, третий выход каждого дополнительного логического элемента И-исключающее ИЛИ соединен с аннигилятором цилиндрических магнитных доменов, а третий выход каждого из основных логических элементов И-исключающее ИЛИ через аннигилятор цилиндрических магнитных доменов соединен с соответствующим выходсм сумматора. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 520623, кл. 6 11 С 19/00, 1976; 2.Авторское свидетельство СССР по заявке К 2490279/18-24, 27.05.77 ( прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Комбинационный двоичный сумматор | 1980 |

|

SU1040604A2 |

| Накапливающий двоичный сумматор | 1979 |

|

SU907811A2 |

| Комбинационный двоичный сумматор | 1980 |

|

SU1040605A2 |

| Комбинационный двоичный сумматор | 1978 |

|

SU797077A1 |

| Накапливающий двоичный сумматор | 1979 |

|

SU911738A2 |

| Комбинационный двоичный сумматор | 1978 |

|

SU951710A2 |

| Комбинационный двоичный сумматор | 1979 |

|

SU959281A2 |

| Комбинационный двоичный сумматор | 1978 |

|

SU907810A2 |

| Накапливающий двоичный сумматор | 1978 |

|

SU766017A1 |

| Комбинационный двоичный сумматор | 1978 |

|

SU744993A1 |

Авторы

Даты

1980-09-15—Публикация

1978-07-12—Подача