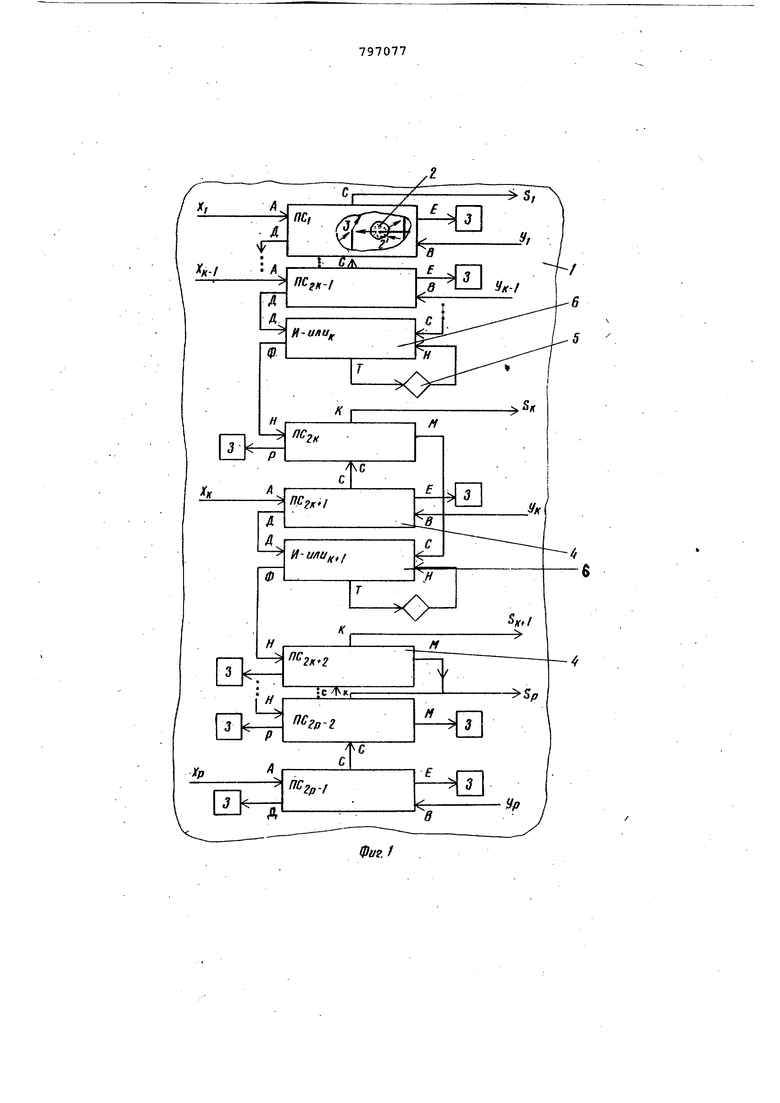

чающее ИЛИ подключены к аннигиляторам доменов. На фиг. 1 и 2 изображена схема предлагаемого КДС. КДС содержит слой магнитоодноосного материала 1 с ЦМД 2, на поверхности которого расположены анни гиляторы 3 доменов и 2Р-1 ЛЭ 4 И-Исключаю1Дее ИЛИ с двумя входами ервые входы нечетных ЛЭ обозначены буквами А, четных -н; вторые входы нечетных ЛЭ обозначены буквг1ми В, четных - С) и трэмя выходс1ми, на первом из которых (с в случае нечетных ЛЭ и К в случае нечетныхЛЭ) реализуется переключательная функция (ПФ) Неравнозначность, а на втором и Третьем (соответственно дл нечетных ЛЭ-Д и Е, для четных - М и Р и ПФ И , Р-1 ДЛ 5, и Р-1 ЛЭ И-ИЛИ 6 с тремя входами (первый вхо выделен буквами Д, второй вход - Н и третий вход - С) и двумя выходами , на первом из которых Т реализуется ПФ -ИЛИ (), а на втором Ф-ПФ И-ИЛИ (ДНУСН). Буквами ПС . . , ПСгк . и. . И-ИЛИц, И-ИЛИ ... обозначены соот ветственно ЛЭ И-Исключающее ИЛИ и ЛЭ И-ИЛИ, а буквами А,В,С,Д,Е,Н,К,М Р,Т и Ф - входы и выходы, цифрам 1-9, 1-9, l-9обозначены позиции, занимаемые каналами ЦМД. . КДС работает следующим образом. В сумматор поступают ЦМД разрядов операндов Х ... , Хц..., Хр и У, ,. . . , У , . . . , Ур . и y-j младшие разряды операндов,. Чере. четверть такта,- прошедших с момента поступления операндов в позиции 1 и 1 входы КДС (далее по тексту момент поступления операндов в позиции 1 и 1 используется в качестве начала отсчета времени для описания функционирования сумматора) , оба слага мых сближаются на расстояние, доста точное для возникновения сил отталкивания между ЦМД, находящимися в одноименных разрядах КДС (позиция 2и 2),. В результате взаимодействия доменов через О,5 такта в позициях 3 (выходы С нечетных ЛЭ И-Исключающее ИЛИ) образуются результа поразрядного суммирования по модулю ,2, а в позициях 3 и 3 (соответс венно,выходы Д и Е нечетных ЛЭ И-Ис ключающее ИЛИ) - переносы в старшие разряды. Причем, если ЦМД переносов с выходов Е поступают в аннигилятор доменов 3, то переносы с выходов Д, продвигаясь по каналс1М 3-4 пост тупают на входы Д ЛЭ И-ИЛИ, взаимо действуют с.ЦМД в ДЛ и через 0,75 такта приводят к появлению ЦМД пер носов на функциональных выходах И-ИЛИ ЛЭ И-ИЛИ (входах Н более старших четных ЛЭ И-Исключающее ИЛ Одновременно ЦМД переносов, поступа в позиции 8, взаимодействуют с ЦМД поразрядных сумм (позиция 3) и при.водят к возникновению сквозных пере-, .носов через более старшие разряды КДС, поразрядные суммы по модулю 2 которых равны единице, до соответствующих первых старших разрядов КДС, поразрядные суммы по модулю 2 которых равны нулю. В результате взаимодействия ЦМД сквозных перенбсов с поразрядными суммами: по модулю 2 через 1,25 такта на функциональных выходах Неравнозначность в позициях б четных ЛЭ И-Исключающее ИЛИ формируется результат суммирования. Более детально работу- КДС можно рассмотреть на примере образования суьдалы и распространения ЦМД сквозного переноса через К-й разряд сумматора. ЦМД К-х разрядов операндов Х и У, через четверть такта поступают на. входы А (позиция 2) и В (позиция 2) ;(2К+1)-го ЛЭ И-Исключающее ИЛИ. Если в К-х разрядах операндов присутствуют ЦМД (, ), то испытывая взаимное отталкивание,первый из них через половину такта появится на выходе Д (позиция 3)(2К+1)-го ЛЭ И-Исключающее ИЛИ (на входе Д К+1-го ЛЭ И-ИЛИ) и вызывает ра спространение сквозного переноса в более старших разрядах КДС, а второй - на выходе Е (2К+1)-го ЛЭ И-Исключающее ИЛИ и поступает в аннигилятор 3 доменов. На выходе С (2К+1)-го ЛЭ И-Исключающее ИЛИ (на входе С 2К-го ЛЭ И-Исключающее ИЛИ ) в этом случае ЦМД отсутствует, вследствие чего ЦМД. переноса из JC-1-го разряда КГС, поступающий в позицию 8, не испытывая отталкивающего взаимодействия, по каналу У через 1,25 такта поступает на к-ый выход сумматора (SK I-). Если в К-ых разрядах КДС присутствует один из ЦМД ( УК.О или Х 0, ), то, не испытывая влияния второго домена, первый ЦМД через 0,5 такта появляется на выходе С (2К+1)-г6 ЛЭ И-Исключающее ИЛИ в позиции 3 и одновременно на входе С2к-го ЛЭ И-Исключающее ИЛИ, реализуя единицу суммы по модулю 2 в К-ом разряде КДС (на выходах Д и Е (2К+1)-го ЛЭ И-Исключающее ИЛИ ЦМД переносов в старшие разряды отсутствуют). Поступающий в позицию 8 домен переноса из младшего (K-l) разряда, взаимодействуя с ЦМД поразрядной суммы по модулю 2 К-го разряда КДС, выталкивает последний домен на вход С К+1-го ЛЭ;И-ИЛИ, вызывая распространение сквозного переноса в старших разрядах сумматора. В данном случае ЦМД на выходе К-го разряда КДС не появляется (), так как ЦМД переноса из (K-l)-ro разряда, взаимодействуя с ЦМД поразрядной суммы по модулю 2 К-гО разряда КДС из щэзиции 8 поступает в позицию 9 5 7 .(функциональный выход И 2К-го ЛЭ И-Исключающее ИЛИ и продвигается к аннигилятору 3 доменов. Если же в позиции 8 домен переноса из младшего к-го разряда КДС не поступает, то, нё испытывая отталкивающего воздействия,,ЦМД поразрядной суммы по модулю 2 К-го,разряда КДС по каналу 4-5-б через такт с четвертью поступает на выход К-го разряда суммы (Sk 1). Случай с нулями разрядах операнд дов тривиален. Процесс распространения сквозного переноса через ТК-й разряд КДС еле- . дующий. Допускается, что поразрядная сумма по модулю 2 в К-м разряде КДС равна единице (ЦМД находится в позиции 3 - на входе С 2К-го ЛЭ И-Исключающее ИЛи). В этом случае ЦМД переноса младшего {К-1)-го разрйда КДС по одному из каналов или Т-4 поступает соответственно либо на вход Д, либо на вход С К-го ЛЭ Й-ИЛИ, вызывая одновременно появление ЦМД К-й ДЛ в позиции 8 2К-ГО ЛЭ И-Исключающего ИЛИ, который, в свою очередь взаимодействует с доменом поразрядной суммы по модулю 2 К-го разряда КДС, отталкивает его на вход С К+1-ro ЛЭ И-ИЛИ, который, в свою очередь, вы.; талкивает ЦМД К+1-й ДЛ в позицию В (2К+2)-го ЛЭ И-Исключающее ИЙИ, и так далее до первого более старшего разряда КДС, поразрядная сумма по модулю 2 которого равна нулю. Допускается, что поразрядная сумма по модулю 2 в К-м разряде КДС равна нулю (в позиции 3 2К-го ЛЭ И-Исключающее ИЛИ ЦМД отсутствует).. В этом случае ЦМД переноса младшего (к-1)-го разряда КДС-, появляющаяся в позиции 8 2К-ГО ЛЭ И-Исключающее ИЛИ, не испытывает отталкивающего воздействия ЦМД К-ой поразрядной суй мы по модулю .2 и по каналу В-5 -б поступает на выход К-го разряда сумматора ). Цепь сквозного перено са обрывается, так как на вход С . K+tro ЛЭ И-ИЛИ ЦМД не поступает. Как следует из приведенного опи сания работы быстродействие КДС соетавляет 1,25 такта при. сложении .Р-разрядных операндов, что в 0,4 . (Р+3) раза повышает аналогичный пока ватель известного сумматора -;(0,5 76 (Р+3) такта) и не зависит от разрядкости операндов, Формула изобретения Комбинационный двоичный сумматор, содержащий слой одноосного материала с цилиндрическими магнитными доменами, на поверхности которого расположены аннигиляторы доменов и 2Р-1 (Р-разрядность операндов). взаимосвязаннйх логических элементов И-Исклют чающее ИЛИ с двумя входами и тремя вы ходами, отличающийся тем, ито, с целью пов{ шения быстродействия он содержит р-1 динамическую ловушку и Р-1 логический элемент И-ИЛИ,. причем каждый К-й из логических злементов И-ИЛИ () и каждая К-я-из динамических ловушек расположены между (2К-1)-м и 2К-м логическими: элементами И-Исключающее ИЛИ первый, второй входы и первый выход первого логического элемента И-Исг-. ключающее ИЛИ соединены соответственно со входами младших разрядов сумматора и выходом младшего разряда сумматора,.первый и второй входы, первый и второй выходы каждого К-го из логических элементов И-ИЛИ соедипены соответственно со вторым выходом (2к-1)-го логического элемента И-Йсключающее ИЛИ, выходом и входом К-й динамической ловушки и первым входом 2К-го логического элемента И-Исключающее ИЛИ, второй-вход,, в.торой и первый выходы каждого из которых соединены соответственно с первым выходом (2К+1)-го логического элемента И-Исключающее ИЛИ,. третьим входом (К+1)-го логического элемента И-ИЛИ и выходом К-г-о разряда сумматора, первый и второй входы каждого из (2К-ь1)-х логических элементов И-Исключающее ИЛИ соединены соответственно со входами К-х разрядов сумматора, а вторые выходы (2Р-2)-го и (2Р-1)-го логических элементов И-Иск ючающее ИЛИ и третий выход каждого из логических элементов И-Исключающее ИЛИ подключены к аннигиляторам доменов. Источники информации, принятые .во внимание при экспертизе 1.Авторское свидетельство СССР № 520623,. кл. G 11 С 19/00, 1975.. 2.Авторскре свидетельство СССР по заявке № 2644538/18-24, кл. G 11 С 11/14 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Комбинационный двоичный сумматор | 1979 |

|

SU959281A2 |

| Комбинационный двоичный сумматор | 1978 |

|

SU744993A1 |

| Накапливающий двоичный сумматор | 1979 |

|

SU907811A2 |

| Накапливающий двоичный сумматор | 1979 |

|

SU911738A2 |

| Накапливающий двоичный сумматор | 1978 |

|

SU766017A1 |

| Многоразрядный двоичный комбинационный сумматор | 1978 |

|

SU764136A1 |

| Комбинационный двоичный сумматор | 1980 |

|

SU1040605A2 |

| Комбинационный двоичный сумматор | 1980 |

|

SU1040604A2 |

| Комбинационный двоичный сумматор | 1978 |

|

SU907810A2 |

| Комбинационный двоичный сумматор | 1978 |

|

SU951710A2 |

Авторы

Даты

1981-01-15—Публикация

1978-09-26—Подача