Изобретение относится к вычислительной технике и может быть использовано в процессорах ЭВМ и вычислительной системе с виртуальной памятью для динамического преобразования .виртуальных (математических). адресов в физические. , Известно устройство для динамического преобразования адресов в системах с виртуальной организацией памяти Щ . Наиболее близким техническим ре шением к изобретению является устройство, содержащее регистр математического адреса,разряды которого, отражающие номер сегмента и страницы, соединены через первую вентильную группу с первыми входами схем сравнения, вторые входы которых соединены адресными полями регистров ассоциативной памяти, разряды номера слова регистра математического адреса соединены через вторую вентильную группу с соответствующими разрядами регистра физического адреса, старшие разряды которого через схему ИЛИ сое динены с выходами рабочих полей регистров ассоциативной памяти через третью вентильную группу и с выходом информационного регистра оперативной памяти через четвертую вентильную . группу, входы рабочих полей регистров ассоциативной памяти соединены через пятую вентильную группу с выходом информационного регистра оперативной памяти, управляющие поля регистров ассоциативной памяти (разряды занятости и использования регистров) соединены с матрицей быстрой переадресации, выходы которой соединены с управляющими входами вентильных групп запис в регистры ассоциативной памяти и входами установки регистров в нулевое состояние, управляющие входы первой - пятой вентильных групп математического и физического адресов схем сравнения и матрицы переадресации соединены с группой выходов блока местного управления, входы которого соединены с центральным устройством управления ЭВМ, выходами схем сравнения, а выход с входом центрального устройства управления 2 . Погрешностью эфих устройств является увеличение цикла выборки необходимого слова информации из оперативной памяти (ОП) за счет допол:нительных затрат времени на преобраэование математического адреса в физический.

Целью изовретения является повышение быстродействия устройства.

Достигается это тем, что .в устройство для динамического, преобразования адресов, содержащее регистр математического адреса, вход которого является первым входом устройства выходы номера сегмента и страницы регистра математического адреса соединены с входом первого блока элементо И, вход которого соединен с первым информационным входом блока сравнения, второй информационный вход которого соединен с адресным выходом блока ассоциативной памяти, выход номера слова регистра математическо-го адреса соединен с входом второго блока элементов И, выход которого соединен с входом младших разрядов регистра физического адреса, вход старших разрядов которого соединен с выходом элемента ИЛИ, выход регистра физического адреса является первым выходом устройства,первый вхо элемента ИЛИ соединен с выходом третьего блока элементов И, а второй вход - с выходом четвертого блока элементов И, вход третьего блока элементов И соединен с информационным выходом блока ассоциативной памяти, информационный вход которого соедине с выходом пятого блока элементов И, вход которого соединен с вторым входом устройства и с входом четвертого блока элементов И, управляющий вход и выход блока ассоциативной паIvIЯти соединены соответственно с выходом и входом блока переадресации первый выход блока местного управления соединен с управляющими входами с первого по пятый блоков элементов и, блока сравнения и блока переадресации, второй вход блока местного управления соединен с выходом блока сравнения, третий вход блока местно1Х управления является третьим входо устройства, а второй выход - вторым выходомустройства, введены регистр адреса предыдущей математической страницы, регистр адреса- предыдущей физической страницы, дополнительная схема сравнения, шестой и седьмой блоки элементов И, причем первый информационный вход дополнительной схемы сравнения соединен с выходом первого блока элементов И и с вхо.дом щестого блока элементов И, второй информационный вход - с информационным выходом регистра адреса предыдущей математической страницы, а выход -. с четвертым входом блока местного управления, третий- выход которого соединен с управляющими входами дополнительной схемы сравнения, шестого и седьмого блоков элементов И, регистра адреса предыдущей математической страницы и регистра адреса предыдущей физической страницы, информационный вход регистра адреса предыдущей математической страницы соединен с выходом шестого блока элементов И, информационный вход регистра адреса преды физической страницы соединен с выходом третьего блока элементов И, а информационный выход - с входом седьмого блока элементов И, выход которого соединен с третьим входом элемента ИЛИ.

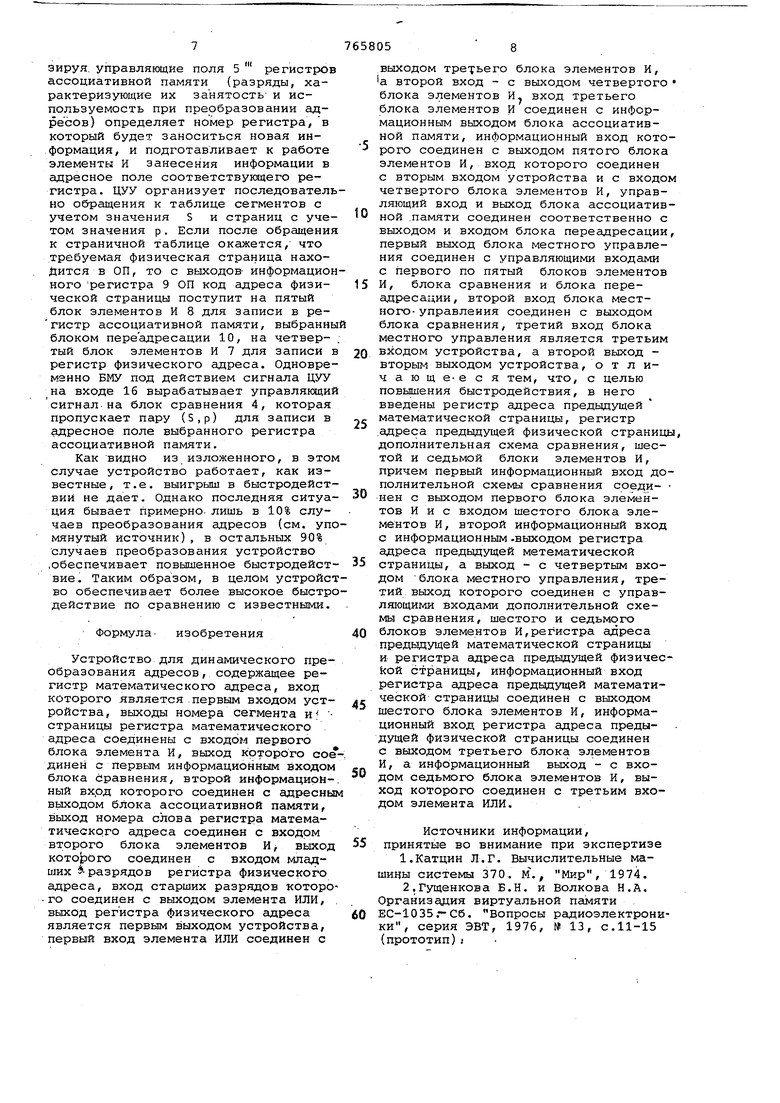

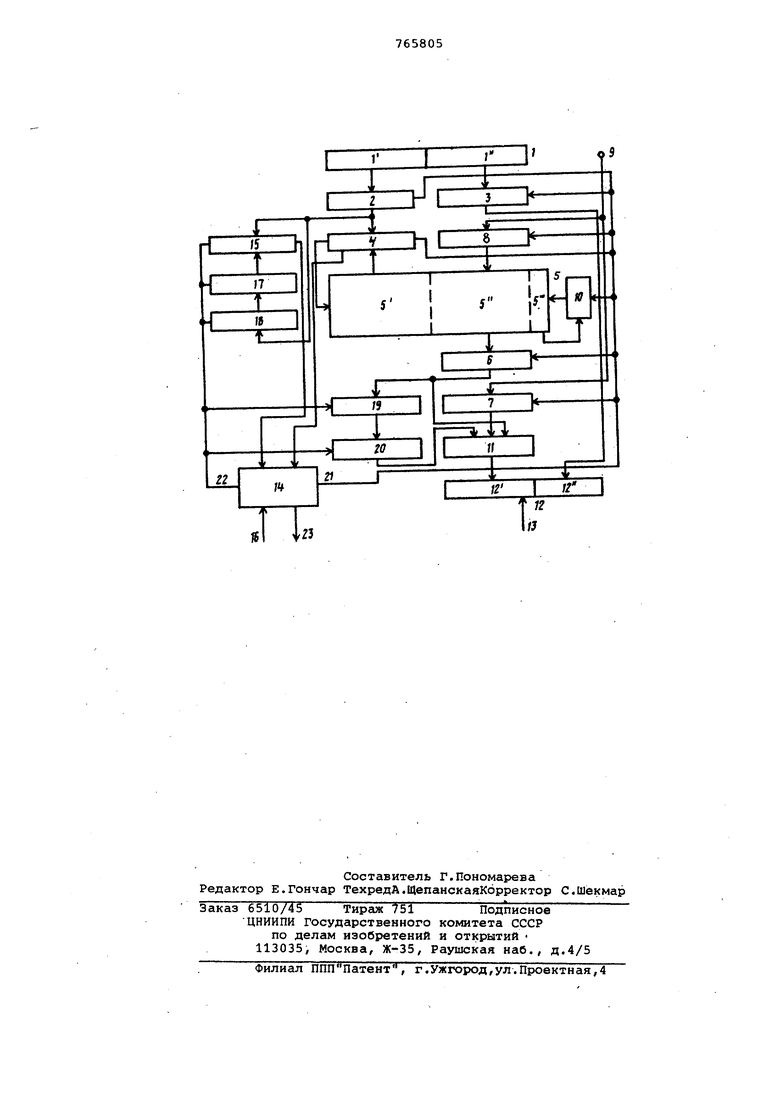

На чертеже схема предлагаемого устройства.

Устройство содержит регистр 1 математического адреса ( -разряды

5 номера сегмента и страницы, 1 -разряды номера слова в странице).первый блок элементов И 2, соединенный выходом с частью 1 регистра 1; блок элементов И 3, соединенный вхс1дом

0 с частью l регистра 1; блок сравнения 4, соединенный первым информационным входом с выходом первого блока элементов И 2; блок ассоциативной памяти 5, адресные поля 5 регистров которого соединены с вторым информационным входом блока сравнения 4; третий блок элементов И 6, информационный вход которого соединен с выходом информационных полей 5 регистров блока ассоциативной памяти

0 5; четвертый и пятый блок элементов И 7 и 8, информационные входы которых соединены с вторым входом 9 устройства; блок переадресации 10, соединенный входом с управляющими

5 полями s регистров блока ассоциативной памяти, элемент ИЛИ 11, соединенный со старшими разрядами 12(номер страницы) регистра физического адреса 12, младшие разряды которого

0 (номер слова) 12 соединены с выходом второго блока элементов И 3, а выход 13 является первым выходом устройства блок местного управления 14 (БЩ) , входы которого соединены с выходом блока сравнения 4, выходом

дополнительной схемы сравнения 15 и третьим входом 16 устройстваJ регистр17 адреса предыдущей математической страницы, информационный вход которого соединен с выходом шестого блока

0 элементов И 18J регистр 19 адреса предыдущей физической страницы, соединенный выходом седьмого блока элементов И 20.

Кроме того, на чертеже показаны первый выход 21 БМУ 14, который соединен с управляющими входами первого-пятого блоков элементов И (2,3,6, 7,8), а также с управляющими входс1ми блока сравнения 4 и блока переадреса0 ции 10; четвертый вход 22 БМУ 14,

который соединен с управляющими входами дополнительной схемы сравнения 15, регистров 17,19, элементов И 18 и 20, второй 23 выход устройства, соединенный с входом центрального УУ

ЭВМ, второй вход устройства соединен с вьоходом информационного регистра ОП; первый выход устройства соединен с входом адресного регистра ОП; третий вход устройства соединен с выходом центрального УУ ЭВМ.

Работает устройство следующим образом.

.Пусть в некоторый момент времени происходит обращение к математической странице, информация о которой имеется в блоке ассоциативной памяти 5, и требуемая физическая страница Нс1ходится в ОП. С приходом кода математического адреса в регистр 1 от ЦУУ ЭВМ запускается 14. Сигнал от БМУ поступает на управляющие входы первого блока элементов И 2 и блока сравнения 15, в.результате чего пара чисел (S,p) t, характеризующая адреса математического сегмента и страницы, поступает для сравнения с адресным полем 5 регистров ассоциативной памяти на блок сравнения 4. Одновременно пара (S-, p)t поступает на дополнительную схему сравнения 15, где сравнивается с содержимьм регистра 17, хранящего пару (S,p) t-( ,т.е математический адрес сегмента и страницы по предыдущему обращению (момент времени t -1 ) . Пусть (S,p)t (S,p)t j тогда с выхода дополнительной схемы сравнения 15 в БМУ поступит сигнал свидетельствующий о том, что предыдущее обращение было к той же самой странице,что и текущее. Так как в . этом случае в предыдущем цикле в регистре 19 был запомнен адрес требуемой физической страницы, то ЕМУ 14 вырабатывает управляющий сигнал, поступающий на управляющий вход седьмого блока элементов И 20, в резуль-. тате чего код адреса физической страницы поступает с регистра 19 через седьмой блок элементов И 20 и элемент ИЛИ 11 на регистр физического адреса 12. Одновременно БМУ посылает управлякяций сигнал на второй блок элемен- тов И 3, чем переписывается адрес слова в странице в регистр физического адреса 12. На этом процесс пре образования заканчивается и БМУ сигналом на выход 23 уведомляет об этом ЦУУ ЭВМ.

Поскольку в рассматриваемом случае обращение происходило к той же самой странице, что и прежде обновления информации в регистрах 17 и 19 не происходит (БМУ не посылает сигналы на третий и шестой блоки элементов И 18 и 6).

Предположим, теперь, что (S , р ) э (S.p)-/ В этом случае с выхода : дополнительной схемы сравнения 15 в БМУ 14 :поступит сигнал, свидетельствующий о том, что обращение происходит к новой странице. БМУ вырабатывает упра-вляилднй сигнал, поступающий на сброс регистра 17, а затем на запись в него новой пары (S,p)tДля этого вьадается управляющий сиг- нал на шестой блок элементов И 18. После этого вырабатывается сигнал на сброс содержимого регистра 19, так 5 как теперь происходит обращение к другой физической странице. Поскольку ее адрес надо теперь выбрать из блока ассоциативной памяти, управляющий сигнал на седьмой блок элементов О И 20 не выдается. После срабатывания блока сравнения 4 по новой паре (S,p)i происходит считывание кода адреса физической страницы из рабочего поля выбранного регистра ассоциативной памяти..Для этого БМУ выра;батывает управляющий сигнал на треIтий блок элементов И 6, в результате I чего код адреса физической страницы :записывается в регистр физического 0 адреса 12 (одновременно туда записывается адрес слова в странице ) а также в регистр 19. Теперь, если следующее обращение будет производиться к той же странице,что и прежде, не потребуется производить вы5

борку из блока ассоциативной памяти, так как ситуация (5,р){.ц(5,р) будет выявлена дополнительной схемой сравнения 15 и БМУ 14 занесет в регистр физического адреса 12 информацию, записанную в .регистре 19.

Таким образом, если происходит подряд несколькообращений к одной .и той же странице (что и бывает прак- тически), то время преобразования математического адреса в физический сокращается на время выборки ин- |формации из б.пока ассоциативной памяти. Это позволяет, во-первых, повыт ;сить производительность ЭВМ за счет 0 сокращения средней длительности цикла обращения к ОП, а во-вторых, делает gee устройство некритичным к параметраг блока ассоциативной памяти.

Более того, в принципе можно ис- 5 пользовать вместо ассоциативнойпамяти быстродействующую память (например, на тонких магнитных пленках) с адресной выборкой. При этом среднее быстродейсжвие устройства будет вы0 Шб/ чем в устройствах с ассоциативной памятью, но построенных по известным схемам.

Рассмотрим теперь работу устройг ства в том, случае, если (S.p). i i(S,p)i,., и пара (S,p).t найдена в блоке ассоциативной . В этом случае с выхода блока сравне.ния 4 на вход БМУ 14 поступает сиг- нал, свидетельствуюрдий о необходи0 |ь«эсти занесения в блок ассоциативной памяти информации по тpeбye юjй странице. БМУ вырабатывает на выходе 23 сигнгш, который поступает в ЦУУ и управлякадий сигнал на запуск блока 5 переадресации 10. Последний, аналиэируя. управляющие поля 5 регистров ассоциативной памяти (разряды, характеризующие их занятость- и используемость при преобразовании адресов) определяет номер регистра, в который будет заноситься новая информация, и подготавливает к работе элементы И занесения информации в адресное поле соответствующего регистра. ЦУУ организует последователь но обращения к таблице сегментов с учетом значения S и страниц с учатом значения р. Если после обращения к страничной таблице окажется, что требуемая физическая страница нахоЙится в ОП, то с ВЫХОДОВ информацио ногорегистра 9 ОП код адреса физической страницы поступит на пятый блок элементов И 8 для записи в регистр ассоциативной памяти, выбранны блоком переадресации 10, на четвертый блок элементов И 7 для записи регистр физического адреса. Одновре менно БМУ под действием сигнала ЦУУ на входе 16 вырабатывает управляющи сигнал.на блок сравнения 4, которая пропускает пару (S,p) для записи в адресное поле выбранного регистра ассоциативной памяти. Как видно из изложенного, в это случае устройство работает, как известные, т.е. выигрыш в быстродейст вий не дает. Однако последняя ситуа ция бывает примерно, лишь в 10% случаев преобразования адресов (см. уп мянутый источник) , в остальных 90% случаев преобразования устройство .обеспечивает повышенное быстродейст вие. Таким образом, в целом устройс во обеспечивает более высокое быстр действие по сравнению с известными. Формула. изобретения Устройство для динамического преобразования адресов, содержащее регистр математического адреса, вход которого является первым входом устройства, выходы номера сегмента и страницы регистра математического адреса соединены с входом первого блока элемента И, выход которого сое динен с первым информационным входом блока Сравнения, второй информацирнный вход которого соединен с адресны выходом блока ассоциативной памяти, выход номера слова регистра математического адреса соединен с входом второго блока элементов И, выход KOTOjporo соединен с входом младших -разрядов регистра физического адреса, вход старших разрядов которо -го соединен с выходом элемента ИЛИ, выход регистра физического адреса является первым выходом устройства, первый вход элемента ИЛИ соединен с выходом третьего блока элементов И, а второй вход - с выходом четвертого блока элементов И. вход третьего блока элементов И соединен с информационным выходом блока ассоциативной памяти, информационный вход которого соединен с выходом пятого блока элементов И, вход которого соединен с вторым входом устройства и с входом четвертого блока элементов И, управляющий вход и выход блока ассоциативной .памяти соединен соответственно с выходом и входом блока переадресации, первый выход блока местного управления соединен с управляющими входами с первого по пятый блоков элементов И, блока сравнения и блока переадресации, второй вход блока местного- управления соединен с выходом блока сравнения, третий вход блока местного управления является третьим входом устройства, а второй выход вторым выходом устройства, о т л ичающе-еся тем, что, с целью повышения быстродействия, в него введены регистр адреса предыдущей математической страницы, регистр .адреса предыдущей физической страницы, дополнительная схема сравнения, шестой и седьмой блоки элементов И, причем первый информационный вход дополнительной схемы сравнения соеди- нен с выходом первого блока элементов И и с входом шестого блока элементов И, второй информационный вход с информационным .выходом регистра адреса предыдущей метематической страницы, а выход - с четвертым входом блока местного управления, третий выход которого соединен с управляпощими входами дополнительной схемы сравнения, шестого и седьмого блоков элементов И,регистра адреса предыдущей математической страницы и регистра адреса предыдущей физической страницы, информационный вход регистра адреса предьвдущей математической страницы соединен с выходом шестого блока элементов И, информационный вход регистра адреса предыдущей физической страницы соединен с выходом третьего блока элементов И, а информационный выход - с входом седьмого блока элементов И, выход которого соединен с третьим входом элемента ИЛИ. Источники информации, принятые во внимание при экспертизе 1.Катцин Л.Г. Вычислительные машины системы 370. М., Мир, 1974. 2.Гущенкова Б.Н. и Волкова Н.А. Организадия виртуальной памяти ЕС-1035.--С6. Вопросы радиоэлектроники, серия ЭВТ, 1976, № 13, с.11-15 (прототип)I

П

I

Е

Е

±

±

г-гп

К

ТТг

13

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления виртуальной памятью | 1980 |

|

SU955076A1 |

| Устройство для динамического преобразования адресов | 1980 |

|

SU903878A1 |

| Устройство управления виртуальной памятью | 1980 |

|

SU1023336A1 |

| Устройство для динамического преобразования адреса | 1985 |

|

SU1265771A1 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ ОБРАЗОВ | 2014 |

|

RU2535182C1 |

| Устройство для управления оперативной памятью | 1985 |

|

SU1291992A1 |

| УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ ОБРАЗОВ | 2010 |

|

RU2430415C1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

Авторы

Даты

1980-09-23—Публикация

1978-08-17—Подача