сл

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1288704A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1988 |

|

SU1529236A1 |

| Устройство для управления и обмена данными | 1986 |

|

SU1319042A1 |

| Процессор | 1984 |

|

SU1200294A1 |

| 8-Битный микропроцессор | 1982 |

|

SU1161950A1 |

| Микропрограммное устройство сопряжения | 1989 |

|

SU1700560A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439617A1 |

| Микропрограммный процессор | 1981 |

|

SU1037262A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении высокопроизводительных вычислительных систем в качестве средства для сопряжения центрального процессора с группой арифметических процессоров. Целью изобретения является повышение быстродействия и надежности вычислительной системы. Устройство содержит блок микропрограммного управления, блок управления композициями, регистр возврата в программу, блок памяти, регистр кода операции, регистр диагностического перехода, узел сравнения, регистр адреса, регистр номера, дешифратор, два триггера, три группы элементов ИЛИ, семь элементов ИЛИ, два элемента И. 2 з.п, ф-лы, 15 ил.

Изобретение относится к вычислительной технике и может быть использовано при построении высокопроизводительных вычислительных систем (В С) в качестве средства для сопряжения центрального процессора (ЦП) с группой арифметических процессоров (АП).

Цель изобретения - повышение быстродействия и надежности вычислительной системы путем замены отказавшей функции АП операционно-эквивалентной композицией не отказавших функций АП, что позволило бы минимизировать потерю быстродействия ВС при отказах функций АП и повысить отказоустойчивость ВС.

Операционно-эквивалентная композиция (ОЭК) - это последовательность функций, выполнение которой приводит к тому

же результату, что и выполнение функции, которой данная последовательность эквивалентна. ОЭК функций, реализуемых АП, могут быть получены из основных известных математических зависимостей, связывающих эти функции. Например, для функции синуса ОЭК.могут быть построены на основе формул (x) cos (х- л/2), sin (х) 1 /cos (х) и ряда других.

Повышение быстродействия В С при отказах функций АП обусловливается значительным различием времени выполнения функции в АП и в форме подпрограммы в ЦП (в среднем 50 - 100 раз). Следовательно, время выполнения ОЭК функций существенно меньше времени выполнения соответствующей программы. Повышение отказоустойчивости ВС объясняется тем,

VJ о ю со XI VI

что при отказе функции АП выполняется работоспособная ОЭК для данной функции и гшшь при отказе всех ОЭК функции производится обращение к ее программной реализации (подпрограмме).

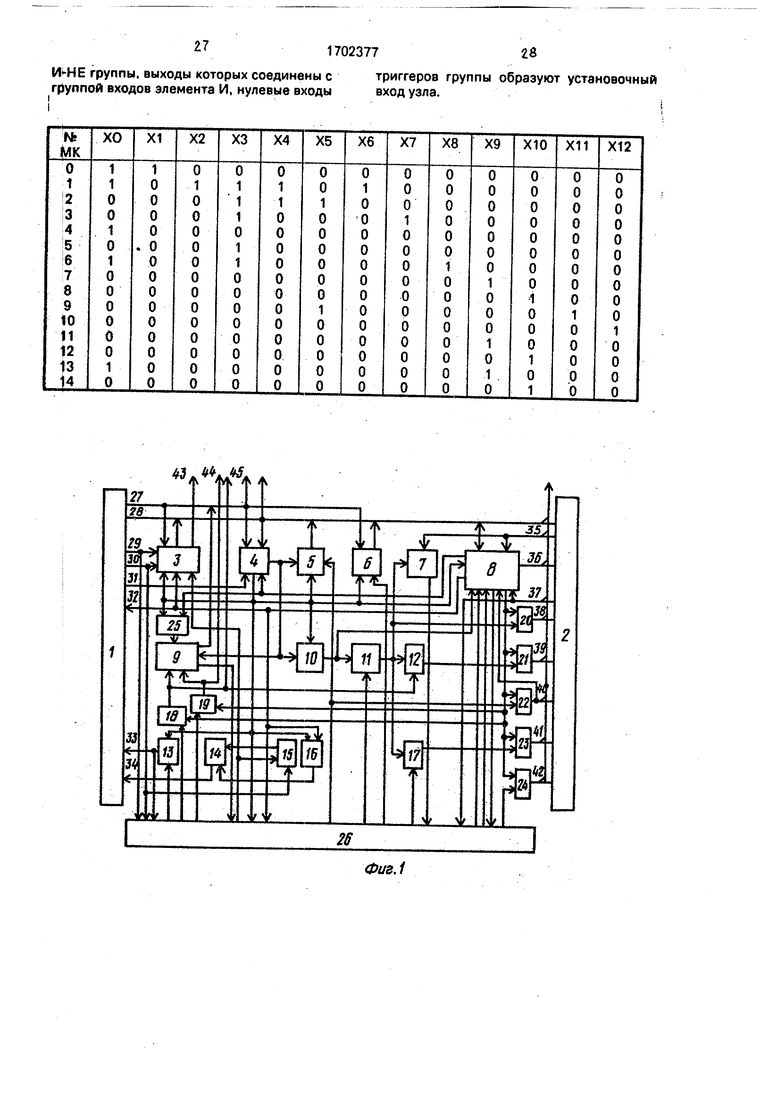

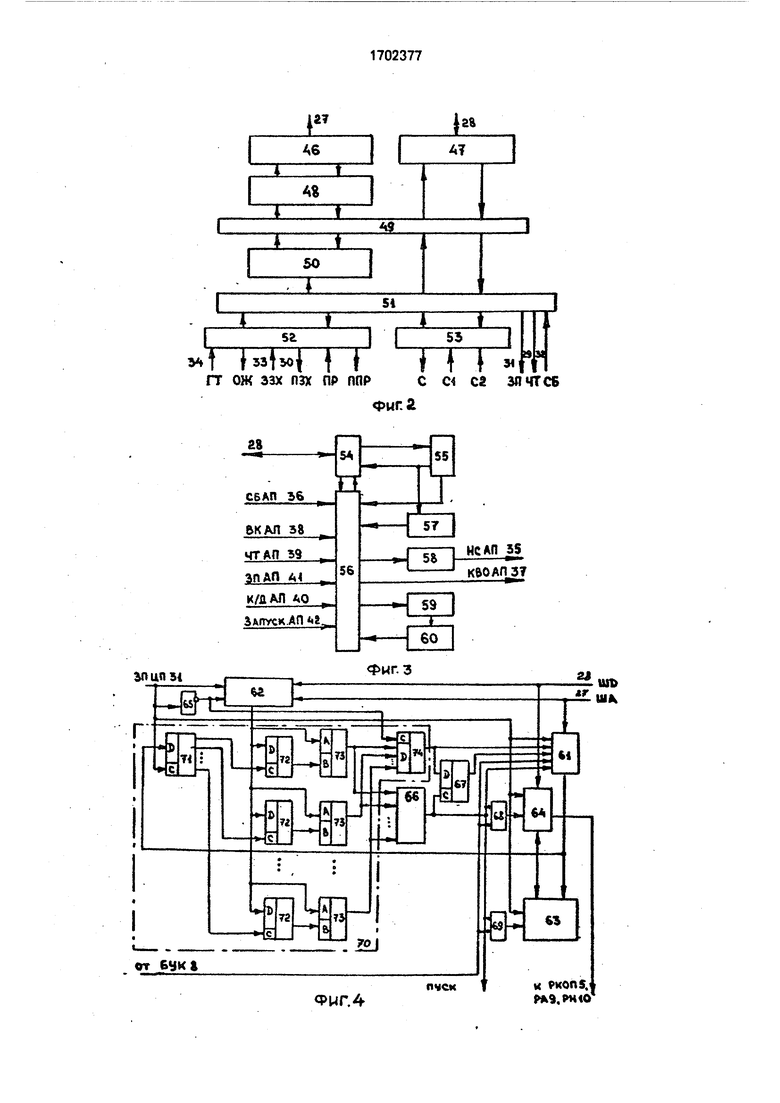

На фигЛ представлена блок-cxeiva устройства; на фиг.2 - блок-схема ЦП; на фиг.З - блок-схема АП; на фмг.4 - блок-схема блока памяти (БП); на фмг.5 - блок-схема реги- Стра возврата в программу (РВП); на фиг.6 - блок-схема регистра кода операции (F КОП); на фыг.7 - блок-схема регистра номера (РН); На фиг.8 - блок-схема регистра адреса (РА); на фиг.З - блок-схема регистра диагностического перехода (РДП); на фиг. 10 - блок- Схема узла сравнения (УС); на фиг. 11 - блок-схема блока управления компос-иция- f- и (БУК); на фиг, 12- блок-схема микропрог- раммного управления; на фиг, 13 - блок-схема узла состояний БУК; ::з фуг.14 - Временная диаграмма перехода в ословнук Программу; на фиг,15 -формат поля памяти, управляющей выполнением ОЭК.

Устройство содержит ЦП 1, АП 2, РВП 3s РП 4, РКОП 5, РДП б, УС 7, БУК 8, РА 9, РН 10, дешифратор 11, элемент И 12, триггеры 13 и 14, элементы ИЛИ 15 и 18, элемент W 17, элементы ИЛИ 18 и 19, группы элементов ИЛИ 20 и 21, элемент ИЛИ 22, группу Элементов ИЛИ 23, элементы ИЛИ 2 и 25, БМУ 26, общую магистраль 27, общую магистраль 28 данных, выход 2S Чтение ЦП ЧТ ЦП), выход 30 Подтверждение захвата ЦП (ПЗх ЦП), выход 31 Запись ЦП (ЗП ЦП), аход 32 Сброс ЦП (СВ ЦП), Вход 33 Запрос захвата ЦП (Зх ЦП), вход 34 Готов- ЦП (ГТ ЦП), выход 35 Неисправность NT (НС АП), вход 36 Сброс АП (СБ АП), Јыход 37 Конец выполнения операции АП (КВО АП), аход 38 Выборка кристалла АП {ВК АП), вход 39 Чтение АП (ЧТ АП), Вход 40 команда/данные АП (К/Д АП), вход 41 Запись АП (ЗП АП), вход 42 Запуск АП (ЗП АП), аход 43 Разрешение вы Зорки ВПП (РВ ВПП), вход 44 Чтение ВПП (ЧТ ВПП) вход 45 Запись ВПП (ЗП ВПП).

ЦП 1 содержит буфер 46 адреса, буфер 47 данных, блок регистров 48, внутреннюю магистраль 49, арифметическое устройство 50, блок 51 управления, блок 52 управления обменом и блок 53 синхронизации.

В устройстве применен ЦП К580ИК80 (6К0.348.393 ТУ).

АП 2 образуют операционный блок 54, сумматор 55, блох 56 управления, первая комбинационная схема 57, триггер 58 неисправности, счетчик 59 ошибок и вторая комбинационная схема 60,

БП 4 содержит коммутатор 61, коммутатор 62, оперативный запоминающий узел

(ОЗУ) 63, шинный формирователь 64, элемент НЕ 65, элемент ИЛИ 66, регистр 67, элементы ИЛИ 68 и 69 и ассоциативный запоминающий узел (АЗУ) 70, состоящий из дешифратора 71, регистров 72, элементов 73 сравнений и шифратора 74.

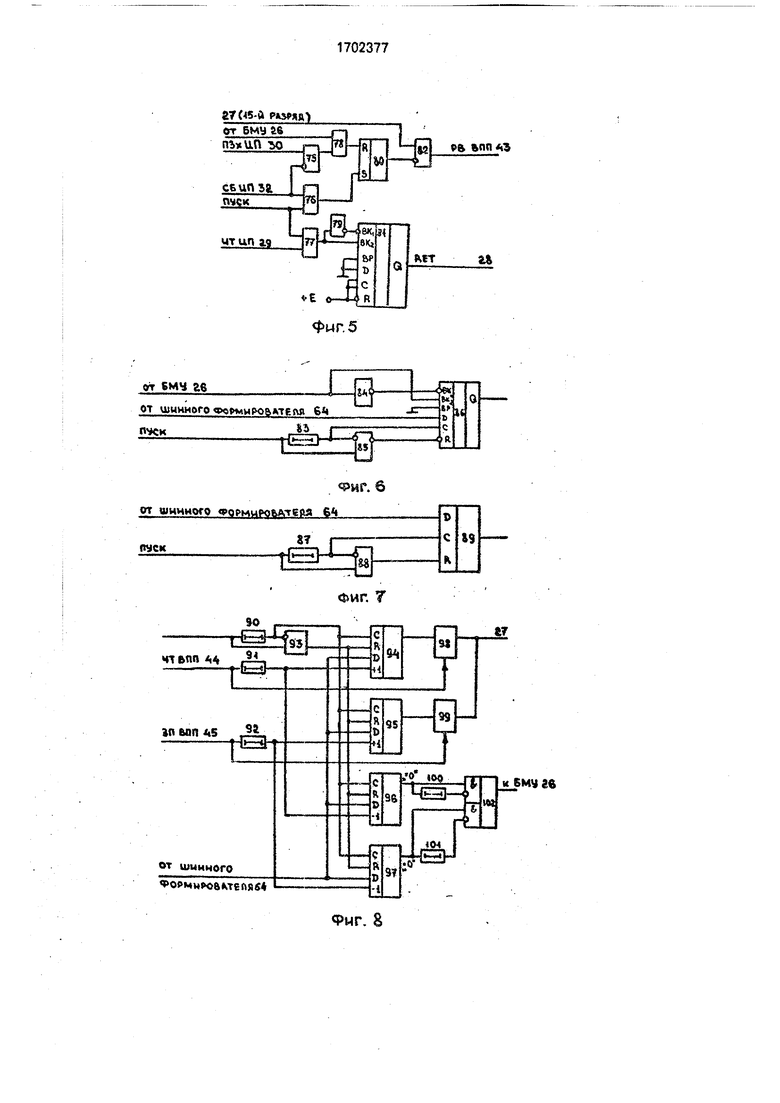

РВП 3 выполнен на элементе И 75, элементе ИЛИ 76, элементе И 77, элементе ИЛИ 78, элементе НЕ 79, триггере 80, многофункциональном буферном регистре (МБР) 81, например, типа К589ИР12 м элементе И 82.

РКОП 5 состоит из элемента 83 задержки, элемента Н Е 84, элемента И 85 и МБР 86.

РН 1C образован элементом 87 задержки, элементом И 88 и регистром 89.

РА 9 содержит элементы 90-92 задержки, элемент И 93, счетчики 94-97, буферный узел 98, буферный узел 99, элементы 100 и i01 м элемент И-ИЛИ 102,

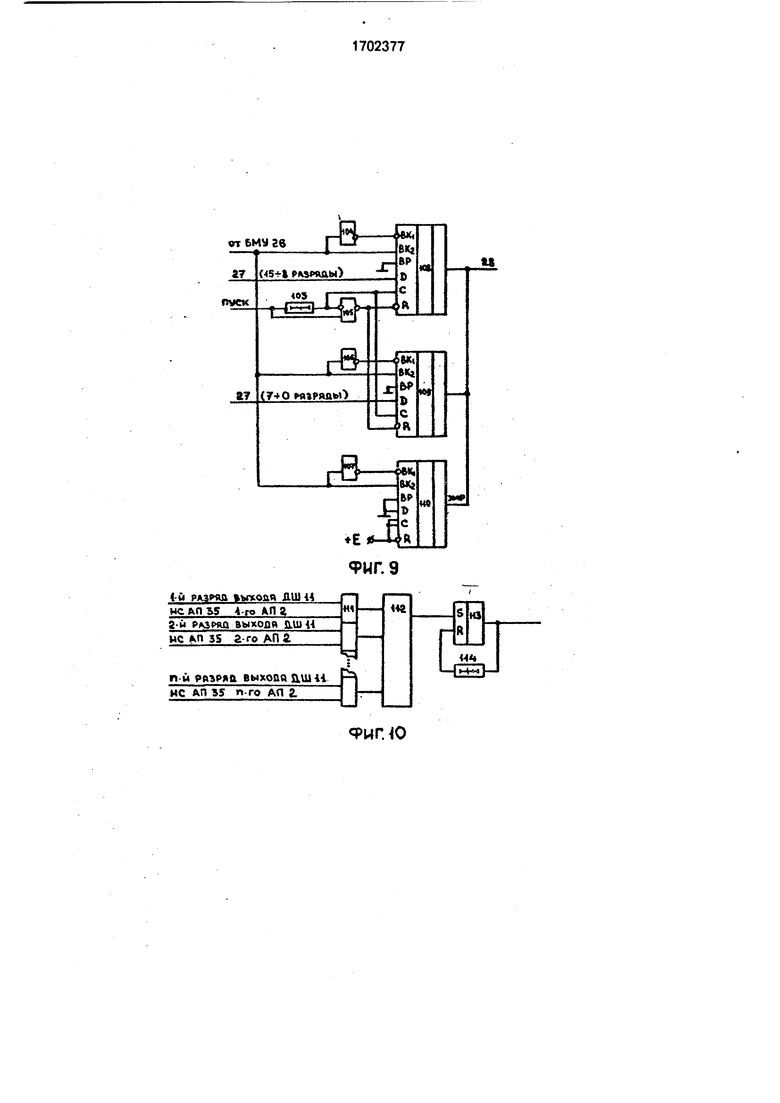

РДП 6 состоит из элемента 103 задержки, элемента НЕ 104, элемента И 105, эле- ментовНЕ 106м 107. а также МБР 108-110.

УС 7 образуют группа элементов И 111, элемент ИЛУ 112, триггер 113 и элемент 114 задержки.

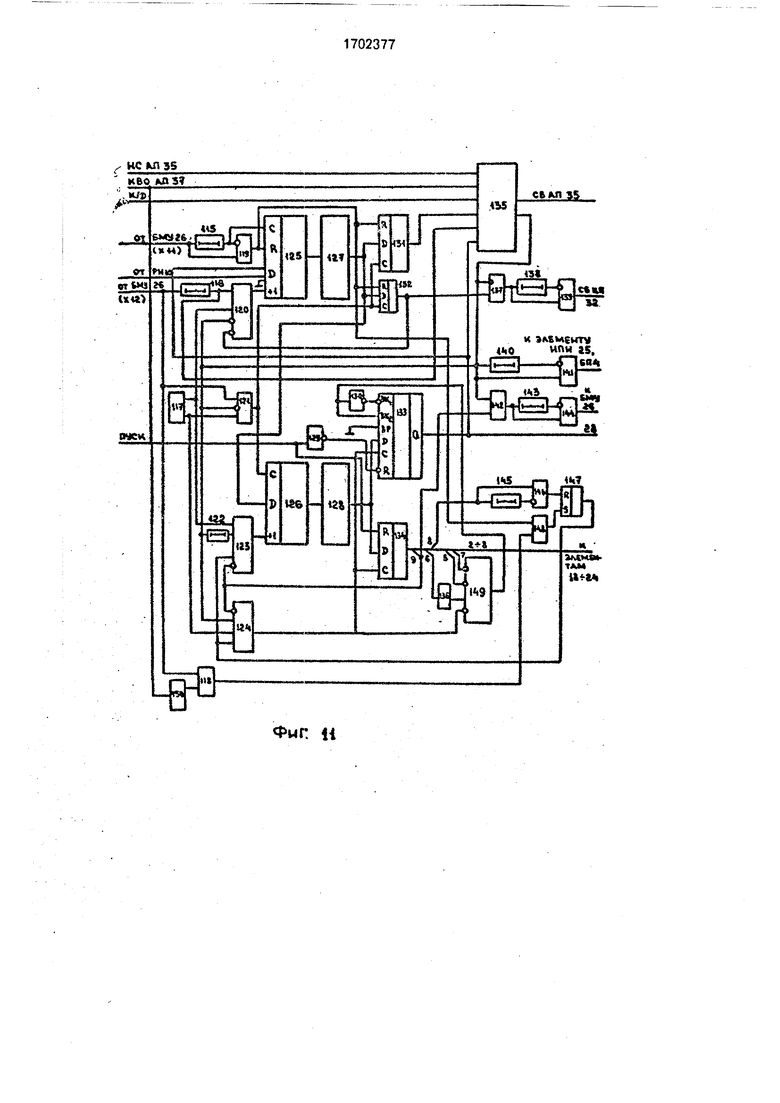

БУК 8 содержит элементы 115 и 116 задержки, генератор 117 импульсов, элементы И 118-121, элемент задержки 122, элементы И 123 и 124, счетчик 125 состояний, счетчик 126 управляющих сигналов, узлы 127 ц 128 памяти, элементы НЕ 129 и 130, регистр 131, триггер 132, МБР 133, регистр 134, узел 135 состояний, элемент ИЛИ 136, элемент И I37, элемент 138 задержки, элемент И 139, элемент 140 задержки, элементы И 141 и 142, элемент 143 задержки, элемент И 144, элемент 145 задержки, элемент И 146, триггер 147, элемент ИЛИ 148, элемент И 149 и элемент ИЛИ 150.

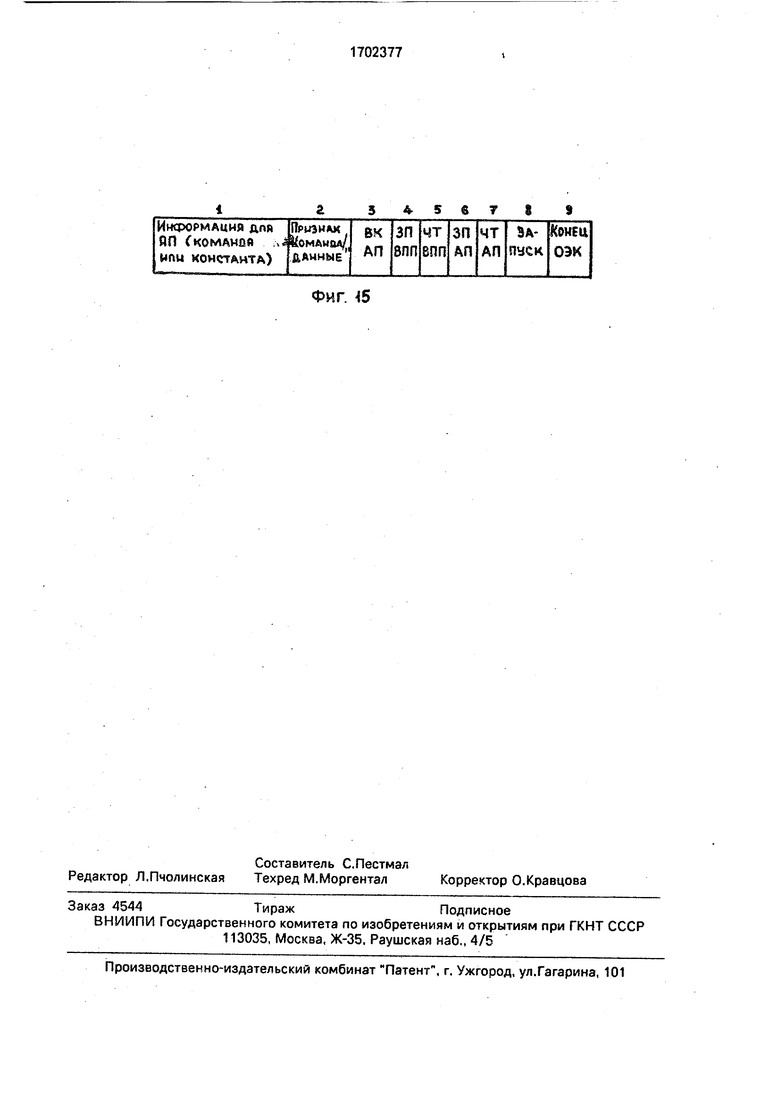

Номера связей, идущих с выхода регистра 134 на входы других блоков соответствуют порядковым номерам полей формата узла 128 памяти (фиг. 15).

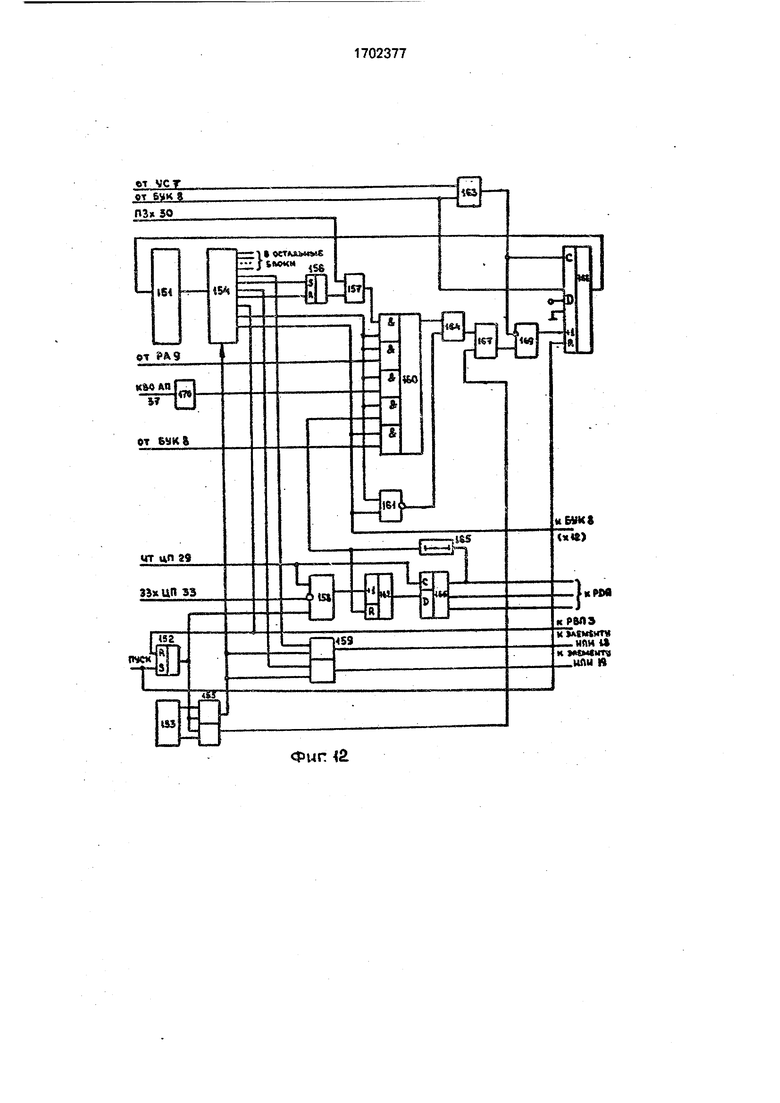

БМУ 26 содержит память 151 микрокоманд, триггер 152, генератор 153 импульсов, регистр микрокоманд 154, элементы И 155, триггер 156, элементы И 157 - 159, элемент И-ИЛИ 160, элемент ИЛИ-НЕ 161, счетчик 162, элементы ИЛИ 163 и 164, элемент 165 задержки, дешифратор 166, элемент И 167, гчетчик микрокоманд 168, элемент S4 169 и элемент ИЛИ 170,

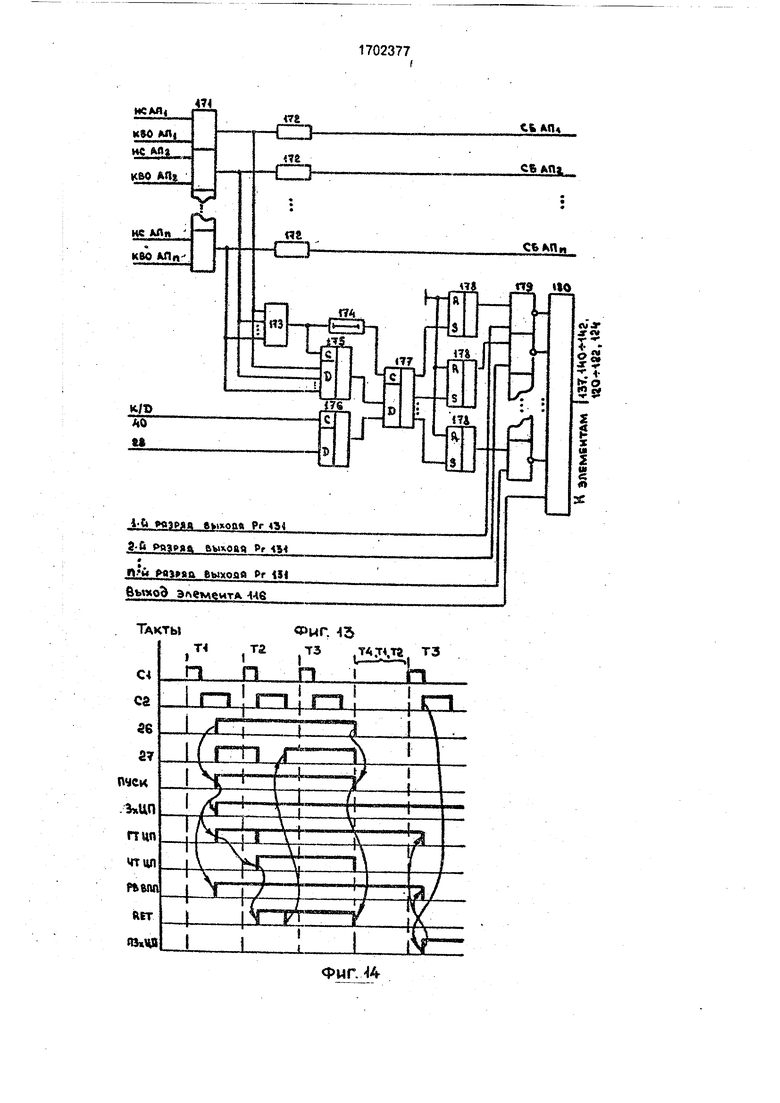

Узел состояний 135 состоит из группы элементов И 171, группы элементов 172 за- дерхкя, элемента ИЛИ 173, элемента 174 задержки, шифратора 175, регистра 176, дешифратора 177, группы триггеров 178, груп- РЫ элементов И - НЕ 179 и элемента И 180,

Формат поля узла 128 памя ги содержит информацию для АП (команда или константа), признак Команда/данные, сигналы выборки АП группы, сигнал записи внешней памяти программы (ВПП), сигнал чтения ВПП, сигнал записи АП группы, сигналы чтения АП группы, сигналы запуска АП группы, признак окончания ОЭК. Порядковые номера полей формата на фиг. 15 соответствуют номерам связей, идущих с выхода регистра 134 на входы других блоков БУК.

В основе построения предлагаемого устройства лежат три принципа: принцип модульного представления программного и аппаратного обеспечения ВС, принцип взаимозаменяемости программных и аппаратных модулей и принцип функционального резервирования на основе ОЭК функций.

Принцип модульного представления заключается в формировании структуры ВС из объектов, называемых модулями и обладающих функциональной завершенностью, реализующих конечное число функций (ап- паратно или программно).

В устройстве в качестве аппаратного модуля используется АП. который в случае реализации нескольких вычислительных операций выступает как многофункциональный аппаратный модуль. При этом для обработки информации АП должен получить входные данные той или иной операции и код операции (команду) в соответствии с требованиями алгоритма решаемой задачи. По окончании процесса вычисления АП выдает обработанные данные как результаты.

Модульное программирование, помимо сокращения времени на разработку программного обеспечения, делает его более наглядным и понятным, позволяет независимо от других программных модулей кодировать и тестировать их. При этом все программные модули оформляются в виде подпрограмм, представляющих единый механизм, которому передается управление программы и от которого возвращается управление программе. Кроме того, использование подпрограмм значительно сокращает объем программной памяти за счет обеспечения возможности многократного обращения к однажды написанной и отлаженной подпрограмме, нет необходимости производить ее многократные дублирования в основной программе. Как и АП, подпрограмма должна получить некоторые входные данные и выдать результаты.

Принцип взаимозаменяемости программных и аппаратных модулей заключается в том, что вычисление любой функции АП с точки зрения результата инвариантно

к средствам вычисления, т.е. может быть выполнено как аппаратным, так и программным модулем, и отличается лишь време- 5 немвычисления.Принцип

взаимозаменяемости основывается на эквивалентности функций соответствующих модулей и способов передачи параметров (исходных данных и результатов) между ос0 новной программной и соответствующими модулями.

Все способы передачи данных, разработанные для микропроцессорной системы (МПС), между основной программой и под5 программой можно разделить на две группы в зависимости от их расположения по отношению к ЦП; внутри ЦП и вне его. К первой группе относятся способы передачи данных с использованием внутренних регистров ЦП

0 или специального стека, встроенного внутрь ЦП. Вторую группу составляют способы обмена данными через внешнюю память программы. Загрузка данных во внутренние регистры или специальный стек

5 ЦП предшествует их хранению в ВПП. Вторая группа способов передачи данных чаще используется для организации подпрограмм. Поэтому можно считать, что наиболее общими способами передачи данных явля0 ются способы передачи через ВПП. В данном устройстве используются только способы передачи данных, при которых возможен доступ к данным всех обрабатываемых модулей системы (данное устройст5 во используется в МПС, в которых имеет место только вторая группа способов передачи данных в подпрограммы).

Принцип функционального резервирования на основе ОЭК функций основывается

0 на том, что функции АП связаны некоторыми зависимостями и могут быть выражены друг через друга. Таким образом, при отказе какой-либо функции АП может быть выполнена одна из ее ОЭК, состоящая из

5 работоспособных функций как этого, так и других АП. Для реализации принципа функционального резервирования на основе ОЭК требуется для множества функций АП построить множество их ОЭК и ввести в устройство сопряжения СП с группой АП

0 блок, осуществляющий при отказе какой-либо функции АП поиск ее работоспособной ОЭК и управление выполнением найденной ОЭК.

5 Данное устройство в составе МПС осуществляет перехват и передачу в АП 2 тех арифметических операций, на эффективное выполнение которых ориентирован АП 2 и которые в однопроцессорной системе реализуются программными средствами, с последующей передачей входных данных в АП 2 и выдачей результатов в нужную область программной памяти.

В случае неверного выполнения функции в АП устройство производит поиск ра - ботоспособной ОЭК неверно выполненной функции и управляет выполнением найденной ОЭК. В случае отсутствия работоспо- робной ОЭК устройство передает Выполнение функции соответствующей под- Программе.

Устройство работает в двух режимах: режиме настройки и рабочем режиме.

В режиме настройки блок 4 формирует так называемую коммутационную матрицу из дескриптора алпаратно реализуемых функций и информационно-управляющих слов АП 2. При этом в регистры 72 АЗУ 70 -записывают метки подпрограмм, имеющих эквивалентную реализацию в аппаратном исполнении на АП 2, а в ячейки ОЗУ 63 - информацию, необходимую АП 2 длк обработки операций и обмена с ВПП: начальные адреса входных данных, начальные адреса выходных данных, код операции, номер АП, длину обрабатываемого слова (например, а байтах), длину результата, Запись произ водится под управлением АП 1, причем таким образом, что имеет место взаимооднозначное соответствие между дескриптором (меткой) К-й подпрограммы, помещаемой в К-й регистр 72 АЗУ 70, и содержимым К-й ячейки ОЗУ 63. Изменяя определенным образом разрядность полей ОЗУ 63, а также объем АЗУ 70, можно получить как требуемое количество аппаратно реализуемых функций и АП 2, включаемых в МПС, так и необходимую длину обрабатываемого слова.

Запись в К-й регистр 72 и К-ю ячейку ОЗУ 63 производится следующим образом,

На общую магистраль адреса 27 ЦП 1 устанавливаются адреса, соответствующие К-му регистру 72 и К-й ячейке ОЗУ. На общую магистраль данных 28 передаются метки К-й подпрограммы и соответствующее начальный адрес входных данных, печальный адрес выходных данных, код К-й операции, номер АП, длина входного слова и длина выходного слова. Сигналом с выхода 31 ЗП ЦП коммутатор 61, коммутатор 62, шинный формирователь 64 переключаются в режим настройки. При этом магистраль адреса 27 коммутируется с дешифратором 71 и адресными входами ОЗУ 63, общая магистраль 28 данных коммутируется с регистрами 72 и информационными входами-выходами ОЗУ 63. Этим же сигналом с выхода 31 ЗП ЦП производится запись К-й метки подпрограммы в К-й регистр 72 (дешифратор 71 открывает входы К-ro регистра 72) и соответствующей информации в К-ю ячейку ОЗУ 63 (сигнал с выхода 31 ЗП ЦП поступает на входы Запись и Разрешенме выборки ОЗУ 63). Осуществляя перезапись коммутационной матрицы, можно переориентировать устройство на обработку требуемого количества прикладных программ.

0 Процесс настройки значительно упрощается в связи с требованиями к оформлению спецификаций для каждой подпрограммы. В этих спецификациях указывается, где находятся данные (адреса

5 входных данных), обрабатываемые подпрограммой и где размещены результаты (адреса выходных данных), полученные при выполнении подпрограмм, В рабочем режиме коммутатор 62 5П 4 подключает общую

0 магистраль 27 адреса к информационным входам регистров 72 и первым входам (входам А) элементов 73 сравнения. Выходы шинного формирователя 64 в рабочем режиме открыты. Поскольку вторые входы (входы

5 В) элементов 73 сравнения соединены с выходами регистров 72, то при поступлении на первые входы элементов 73 сравнения с общей магистралью 27 адреса кода, равного содержимому К-ro регистра 72, на выходе

0 К-ro элемента 73 сравнения появляется сигнал, который переключает элемент ИЛИ 66 в единичное состояние, вырабатывая сигнал Пуск. Сигнап с К-ro элемента 73 сравнения поступает также на один из входов шифра5 тора 74, на выходе которого появляется код, соответствующий адресу К-й ячейки ОЗУ 63. Код, соответствующий адресу К-й ячейки ОЗУ 63 запоминается по сигналу Пуск в регистре 67. Кроме того, сигналом Пуск

0 переключаются коммутатор 61 и через элемент ИЛИ 68 шинный формирователь 64 ак, чтобы они подключали соответственно выходы шифратора 74 к адресным входам ОЗУ 63 и информационные входы-выходы

5 ОЗУ 63 к входам регистров 5, 9 и 10. Этот же сигнал Пуск подается через элемент ИЛИ 69 на входы Чтение и Разрешение выборки ОЗУ 63, осуществляя выборку К-й ячейки 63, в регистр 5 - кода К-й операции,

0 в регистр 9 - адресов входных и выходных данных и длин слов, в регистр 10 - номера АП. При выполнении ОЗК (а случае неверного выполнения функции АП) требуется восстановление в РА 9 адресов входных и

5 выходных данных и дпин слов, В этом случае сигналом от БУК 8 переключаются коммутатор 61 и через элемент ИЛИ 68 шинный формирователь 64 так, чтобы они подключали соответственно выходы регистра 67 (в котором сохранился код, соответствующий

адресу К-й ячейки ОЗУ 63) к адресным входам ОЗУ и информационные входы-выходы ОЗУ к входам регистров 5, 9 и 10. Этот же сигнал от БУК 8 подается через элемент ИЛИ 69 на входы Чтение и Разрешение выборки ОЗУ 63. осуществляя выборку в РА 9 адресов входных и выходных данных и длин слов. Выборка в регистры 5 и 10 в этом случае не производится, так как сигнал от БУК 8 не поступает на их входы записи.

Расчеты показывают, что времени, в течение которого на шине адреса 27 присутствует адрес ячейки ВПП (для К580 - в течение 1-3 тактов, равных 1,5 мкс при тактовой частоте 2 МГц), достаточно для ёыявления обращения к аппаратно реализуемой функции, подачи сигнала на вход ЗЗх ЦП 33 и выборки содержимого К-й ячейки ОЗУ 63 в регистры 5, 9 и 10.

Таким образом, после настройки блок 4 содержит дескриптор аппаратно реализуемых функций и информационно-управляющие слова АП 2. Остальные узлы устройства несут следующую функциональную нагрузку. Сигнал Пуск с выхода элемента ИЛИ 66 (фиг.4) открывает входы регистра 5 (фиг.6) и регистра 10 (фиг.7) таким образом, что вначале производится обнуление содержимого МБР 86 и регистра 89. Элементы 83 и 87 задержки имеют задержку на время сброса (обнуления) МБР 86 и регистра 89 соответственно. Затем сигнал Пуск поступает на С-входы МБР 86 и регистра 89 соответственно, разрешая запись в МБР 86 и регистр 89 данных по информационным входам. Сигнал БМУ 26, поступая на вход элемента НЕ 84, открывает выходы регистра 5, в результате чего содержимое последнего подается на общую магистраль 28 данных. Содержимое регистра 89 (номер АП) подается на вход дешифратора 11.

Сигнал Пуск переключает в единичные состояния первый 13 и второй 14 триггеры. При этом с выхода триггера 13 сигнал поступает на вход ЗЗх ЦП 33 и в БМУ 26, а с выхода триггера 14 - на вход ГТ ЦП 34.

В процессе обработки информации в МПС данное устройство выявляет обращение к аппзратно реализуемой функции и прежде, чем принять на себя управление системой, подготавливает обратный переход в программу.

Организация аппаратного перехода в основную программу происходит следующим образом.

Сигнал Пуск переключает в единичное состояние триггер 80 регистра 3 (фиг.5). Сигнал с выхода триггера 80 поступает на инверсный вход элемента и 82. Прямой выход последнего соединен с выходом В С, управляющим разрешением выборки ВПП (обычно это 15-й разряд общей магистрали 27 адреса). В результате происходит блокировка ВПП. При появлении сигнала с выхода 5 ЧТ ЦП 29 на общую магистраль 28 данных поступает код команды выхода из подпрограммы RET из МБР 81. Сброс команды RET происходит при исчезновении сигнала Пуск, а сброс блокировки ВПП - при появ0 лении сигнала с выхода 30 ПЗх ЦП. Времен- ная диаграмма на фиг.14 поясняет организацию аппаратного перехода в основную программу, ЦП 1 выставляет единичный сигнал на выходе 30 ПЗх ЦП в

5 начале третьего такта машинного цикла Чтение, если сигнал на вход 33 ЗЗх ЦП поступил в первом такте за 180 не до нарастающего фронта второго синхроимпульса, в противном случае сигнал ПЗх выставляет0 ся в третьем такте следующего машинного цикла.

АЗУ 70, выполненное на современной элементной базе, имеет очень малое время срабатывания (порядка 70 не), что позволяет

5 в 1-3 тактах первого машинного цикла ЦП 1 произвести необходимые действия по подготовке перехода в основную программу.

Блокировка ВПП происходит также при появлении сигнала на первом выходе БУК.

0 Сброс блокировки ВПП при этом производится специальным сигналом с выхода БМУ 26.

Сигнал Пуск, поступающий на вход регистра 9, вначале обнуляет счетчики 94-97,

5 а затем разрешает запись данных в них с выхода шинного формирователя 64 по информационным входам счетчиков 94-97. Элемент 90 задержки имеет задержку на время сброса (обнуления) счетчиков 94-97.

0 При этом в счетчик 94 записывается начальный адрес входных данных, в счетчик 95 - начальный адрес выходных данных, в счетчик 96 - дпина входных данных, в счетчик 97 - длина выходных данных. При появлении

5 сигналов ЧТ ВПП 44 или ЗП ВПП 45 открывается буферный узел 98 или 99 с тремя состояниями. При этом содержимое счетчика 94 или счетчика 95 поступает на общую магистраль 27 адреса. При отсутствии сиг0 налов ЧТ ВПП 44 или ЗП ВПП 45 буферные узлы 98 и 99 находятся в состоянии высокого сопротивления. Элементы 91 и 92 задержки (с задержкой на время выборки содержимого счетчиков 94-97) передают сигналы на

5 счетные входы счетчиков 94-97 после выборки их содержимого. Таким образом, при каждом обращении к счетчикам содержимое увеличивается на единицу (для счетчиков 94 и 95) или уменьшается на единицу (для счетчиков 96 и 97). При равенстве нулю

счетчиков 96 и 97 на их выходах появляется сигнал, поступающий через элемент № ИЛИ 102 на вход элемента И-ИЛИ 160 БМУ 26, прекращая обращение к ВПП. Элементы 100 и 101 задержки имеют задержку на время выборки очередной микрокоманды из памяти 151 микрокоманд.

При появлении сигнала Пуск из входе регистра 6 вначале обнуляется содержимое МБР 108и 109. Элемент задержки 103 имеет задержку на время сбрасывания (обнуления) МБР 108 м МБР 109. После этого сигнал Пуск разрешает запись в МБР 108 м МБР 109 содержимого общей магистрали 27 адреса по информационным входам, При этом в МБР 109 записывается содержимое младших разрядов (7-0) общей магистрали 2 адреса, а в МБР 108 - содержимое старших разрядов (15-8) общей магистрали 27 адреса. Сигналы из БМУ 26 (с выхода дешифратора 116), разнесенные во времени, открывают выходы МБР 108-110. При этом на общую магистраль 28 данных поступает код команды безусловного перехода и ад рее перехода (содержимое МБР 110, затем МБР 109, МБР 108). Код команды безусловного перехода в МБР 110 появляется при включении питания на устройство.

Входы узла 7 (входы элементов И 111) соединены с выходами дешифратора 11 и выходами 35 НС АП всех АП 2 структуры МПС. При наличии сигналов с этих блоков на одном из элементов И 111 на его выходе появляется сигнал, который через элемент ИЛ И 112 перекл ючает три ггер 113 в един ич- ное состояние. С выхода последнего сигнал подается на БМУ 26.

Элемент 114 задержки имеет задержку на время записи информации в счетчик микрокоманд 168 по его информационным входам.

БУК 8 при отказе выполняемой функции АП обеспечивает поиск ОЭК данной функции, которая может быть выполнена в текущем состоянии ВС, и управляет ее выполнением. Сигналом Пуск осуществляется начальная установка БУК 8, заключающаяся в обнулении МБР 133 и регистра 134. Структурно в БУК 8 можно выделить подсистему поиска ОЭК и подсистему управления выполнением ОЭК. Основными элементами подсистемы поиска ОЭК являются узел памяти 127 состояний, счетчик состояний 125, узел 135, В памяти состояний хранится информация об ОЭК для всех функций АП группы в следующем формате; состояние АП группы, необходимое для выполнения данной ОЭК, записывается в регистр 131; признак последней ОЭК данной функции записывается в триггер 132; начальный адрес управляющих сигналов данной ОЭК в узел 128 записывается в счетчик 126. Данная информация в узле памяти состояний располагается последовательно в

порядке возрастания номеров АП, для конкретного АП в порядка возрастания кодов функций, для конкретной функции информация может быть ранжирована по времени выполнения ОЭК. Такое расположение по0 зволяет непосредственное сзязать номер АП и код функций с адресом информации с ее первой ОЭК в узле памяти состояний.

Узел 135 обеспечивает сброс триггеров неисправности АП при отказе выполняемых

5 функций АП, фиксацию текущего состояния АП группы и сравнение текущего состояния АП группы с состоянием, требуемым для выполнения рассматриваемой ОЭК. Сброс триггеров неисправности осуществляется

0 элементами И 171 и элементами 172 задержки. При появлении импульсного сигнала на выходе КВО АП 37 одного из АП и при наличии сигнала с выхода 35 НС АП этого АП (что соответствует отказу выполняемой функции

5 АП) импульсный сигнал с выхода соответствующего элемента И 171 группы поступает через элемент 172 задержки на вход 36 СБ ЛП соответствующего АП, сбрасывая его. Элементы задержки группы имеют задерж0 ку на время фиксации отказа функции АП в регистре состояния АП группы, собранном на группе триггеров 178. Функции в регистре состояния АП идентифицируются по номеру АП, в котором произошел отказ

5 (поступает на дешифратор 177 с шифратором 175) и по коду функции (поступает на дешифратор 177 с регистра 176). Код выполняемой функции АП записывается в регистр 176 с общей магистралью данных 28 по сиг0 налу Команда/данные, поступающему с элемента ИЛИ 22 на синхровход регистра 176, т.е. при выдаче АП кода функции для выполнения, данный код одновременно с записью в АП записывается в регистр 176.

5 При отказе функции сигнал с выхода элемента И 171 поступает на один из информационных входов шифратора 175 и через элемент ИЛИ 173 на его разрешающий вход. На выходе шифратора 175 появляется

0 код, соответствующий номеру АП, в котором произошел отказ. Код номера АП вместе с кодом функции из регистра 176 дешифрируется дешифратором 177, обеспечивая установку в единичное состояние

5 соответствующего отказавшей функции АП триггера 178; элемент 174 задержки имеет задержку на время срабатывания шифратора 175. Начальный сброс триггера 178 осуществляется сигналом сброса и вьфабатызающимся при включении питамогла быть выполнена в текущем состоянии АП группы, осуществляется переход к соответствующей подпрограмме, Для этого с первого выхода БУК 8 сигнал поступает на вход 32 СБ ЦП (длительностью не менее трех тактов машинного цикла ЦП 1), на вход регистра 8 (блокировка ВПП), на выходы БМУ 26 и элемента ИЛИ 16 (снятие захвата шин ЦП 1 и установка сигнала на вход 34 ГТ ЦП). При появлении сигнала с выхода 29 ЧТ ЦП на общую магистраль 2У данных выдается код команды безусловного перехода и адрес перехода к подпрограмме, Затем сбрасывается сигнал на входе 34 ГТ ЦП, ВПП блокируется сигналом из БМУ 26, БМУ 26 останавливается.

Формуле изобретения 1. Устройство для сопряжения центрального процессора с группой арифметических процессоров, содержащее блок микропрограммного управления, блок памяти, регистр возврата в программу, регистр кода операции, регистр диагностического перехода, узел сравнения, регистр адреса, регистр номера, дешифратор, два триггера, два элемента ИЛИ, два элемента И, причем первый информационный выход регистра возврата в программу, информационный вход блока памяти, информационные выходы регистра кода операций, регистра диагностического перехода соединены с общей магистралью данных устройства для подключения к информационному входу-выходу центрального процессора, информационным входам- выходам арифметических процессоров группы и информационному входу-выходу внешней памяти программ, информационные входы регистра возврата в программу, регистра диагностического перехода, первый информационный выход регистра адреса, адресный вход блока памяти соединены с общей адресной магистралью устройства для подключения к адресному выходу центрального процессора и адресному входу внешней памяти программ, вход чтения регистра возврата в программу соединен с первым входом логического условия блока микропрограммного управления и является входом устройства для подключения к зыхо- ду чтения центрального процессора, вход записи регистра возврата в программу соединен с вторым входом логического условия блока микропрограммного управления и первым входом первого элемента ИЛИ и является входом устройства для подключения к выходу подтверждения захвата центрального процессора, вход записи блока памяти является входом устройства для подключения к выходу записи центрального

5

0

5

процессора, выход первого триггера соединен с третьим входом логического условия блока микропрограммного управления и

является выходом устройства для подключения к входу запроса захвата центрального процессора, выход второго триггера является выходом устройства для подключения к входу готовности центрального процессора,

Q первый вход узла сравнения является входом устройства для подключения к выходам неисправности арифметических процессоров группы, четвертый вход логического условия блока микропрограммного управления является входом устройства для подключений к выходам конце выполнения операции арифметических процессоров группы, второй информационнчй выход регистра возврата в программу является выходом устройства для подключения к разрешающему входу внешней памяти программ, при этом первый информационный выход блока памяти соединен с информационными входами регистра кода операции, регистра номера и регистра адреса, второй информационный выход регистра адреса соединен с пятым входом логического условия блока микропрограммного управления, первым еьгход которого соединен с первым установочным входом регистра возврата в

0 программу и вторым входом первого элемента ИЛИ, выход которого соединен с единичным входом второго триггера, нулевой вход которого соединен с выходом второго элемента ИЛИ, первый вход которого сое5 динен с вторым информационным выходом блока памяти, разрешающим входом регистра возврата в программу, установочным входом регистра кода операции, входами записи регистра диагностического перехоQ да и регистра номера, шестым входом логического условия блока микропрограммного управления и нулевым входом первого триггера, единичный вход которого соединен с вторым выходом блока микропрограммного управления, третий выход которого соединен с первым входом первого элемента И, второй вход которого соединен с выходом дешифратора, первым входом второго элемента И и вторым входом узла сравнения, выход которого соединен с седьмым входом

0 логического условия блока микропрограммного управления, четвертый, пятый и шестой выходы которого соединены соответственно с входом записи регистра кода операции, зходом чтения регистра ди5 агностического перехода и разрешающим

входов дешифратора, информационный

вход которого соединен с выходом регистра

- номера, отличающееся тем, что, с

целью повышения быстродействия и надеж5

мости вычислительной системы, в него введены блок управления композициями, пять йлемеитов ИЛИ, три группы элементов ИЛИ, причем первый выход блока управления композициями соединен с восьмым входом логического условия блока микропрограммного управления, вторым входом второго элемента ИЛИ и вторым ус- тановочнььм входом регистра возврата в программу w яеяяется выходом устройства для подключения к входу сбросе центрального процес -;-р-з, аыход третьего элемента ИЛИ являете. выходом устройства для подключения к входам запуска арифметических процессоров группы, выход че-вертого элемента ИЛИ соединен с первым входом логического условия блока управления композициями и является выходом устрой- фтез для подключения к входам коман- ы/данных арифметических процессоров Группы, второй выход блока управления Композициями является выходом устройства для подключения к входам сброса арифметических процессоров группы, выходы Элементов ИЛИ первой группы образуют Группу выходов устройства для подкпюче- шя к разрешающим входам арифметических процессоров группы, выходы элементов ИЛИ второй или третьей групп Образуют группы Е- ходов устройства для подключения соответственно к входам чтения и записи арифметических процессоров группы, выход пятого элемента ИЛИ соединен с вторым входом второго элемента И, йервым входом чтения регистра адреса и Является выходом устройства для подключения к входу записи внешней памяти программ, выход шестого элемента ИЛИ Соединен с вторым входом чтения регистра адреса и является выходом устройства для подключения к входу чтения внешней памяти программ, три первые входы третьего, пятого и шестого элементов ИЛИ соединены соответственно с седьмым, восьмым и девятым выходами блокп микропрограммного упрааления десятый и одиннадцатый выходы и девятый вход логического условия которого соединены соответственно с вторым, третьим входами логического условия и третьим выходом блока управления композициями, группа выходов которого соедипена с первыми входами элементов ИЛИ первой, второй и третьей групп, первым входом четвертого элемента ИЛИ и вторыми входами третьего, пятого и шестого элементов ИЛИ, вход записи регистра адреса соединен с выходом седьмого элемента ИЛИ, первый вход которого соединен с вторым информационным выходом блока памяти и четвертым.входом логического условия бло0

5

0

5

0

5

0

5

0

5

ка управления композициями, четвертый выход которого соединен с входом чтения блока памяти и вторым входом седьмого элемента ИЛИ, выход первого элемента И соединен с вторыми входами элементов ИЛИ третьей группы, четвертый выход блока микропрограммного управления соединен с вторым входом четвертого элемента ИЛИ, выход второго элемента И соединен с вторыми входами элементов ИЛИ второй группы, выход дешифратора соединен с вторыми входами элементов ИЛИ первой группы, информационный вход-выход, пятый, шестой и седьмой входы логического условия блока управления композициями соединены соответственно с общей магистралью данных, первым входом узла сравнения, четвертым входом логического условия блока микропрограмного управления и выходом регистра номера.

ния по положительному перепаду напряжения, который поступает на нулевые входы триггеров 178. После начальной установки на нулевых входах триггеров 178 в течение всего времени работы МПС сохраняется напряжение О, что обеспечивает возможность установки триггеров 178 по единичным входам и сохранение их состояний в случае отсутствия сигналов на единичных входах. Сравнение текущего состояния АП группы с состоянием, требуемым для выполнения рассматриваемой ОЭК, производится элементами И-НЕ 179 и элементом И 180 Единичный сигнал на выходе К-го триггера 178 группы свидетельствует об отказе соответствующей функции. Единичный сигнал на К-м разряде выхода регистра 131 свидетельствует о требовании работоспособности соответствующей функции для выполнения рассматриваемой ОЭК. Несовпадение текущего и требуемого состояния АП группы (нулевой сигнал с выхода элемента И 180) получается при наличии хотя бы одного нулевого сигнала с выходов элемента И-НЕ 179 (при единичном разрешающем сигнале от БМУ 26). Нулевой сигнал с выхода К-го элемента И-НЕ группы 179 получается лишь при наличии единичных сигналов с выхода триггера 179 и К-го разряда выхода регистра 131, что соответствует требованию функции и АП, которая зафиксирована как отказавшая,

Основным элементом подсистемы управлением выполнения ОЭК является узел 128 памяти управляющих сигналов, в котором хранятся сигналы управления выполнением всех ОЭК всех функций АП группы в формате, приведенном на фиг. 15, Слово управляющих сигналов в данном формате определяет элементарные операции МПС, такие как: загрузка константы в К-й АП, загрузка данных в К-й АП из ВПП, загрузка кода функции в К-й АП, запуск К-го АП, чтение промежуточного результата из К-го АП в Р-ый АП, чтение результата из К-го АП в ВПП. Последовательность таких управляющих слов обеспечивает выполнение любой ОЭК функции АП. Последовательность управляющих слов для всех ОЭК функций АП группы могут распологаться в узле 128 в произвольном порядке. Адреса начальных управляющих слов ОЭК хранятся в узле 127 памяти состояний, откуда при активизации конкретной ОЭК ее адрес начального управляющего слова заносится в счетчик 126. Формирование содержимого узла 127 памяти состояний 127 и узла 128 производится при разработке устройства полученным ОЭК функций.

Сигнал с десятого выхода БМУ 26, поступающий на второй вход БУК 8 (при отказе выполняемой функции АП), вначале обнуляет счетчик 125 состояний, регистр 131. тригrep 132 и устанавливает триггер 147 в единичное состояние, а затем разрешает запись в счетчик 125 состояний с выходов РКОП 5 и РН 10 информации, однозначно идентифицирующей отказавшую функцию

0 АП и являющейся адресом информации об ее первой ОЭК в памяти состояний. В качестве синхронизирующего элемента в БУК используется двухфазный генератор 117 импульсов. Синхроимпульсы первой фазы

5 поступают через элементы И 120 и 123 на счетные входы счетчика 125 состояний и счетчика 126 соответственно. Синхроимпульсы второй фазы поступают через элемент И 121 на синхровходы регистра 131,

0 триггера 132, счетчика 126, а через элемент И 124 на синхровходы МБР 133 и регистра 134, а также на элемент И 149. Синхроимпульсы второй фазы обеспечивают чтение информации из узлов 127 и 128. Синхроим5 пульсы первой фазы обеспечивают увеличение содержимого счетчика 125 состояний и счетчика 126. Элементы И обеспечивают прохождение синхроимпульсов лишь при выполнении определенных условий.

0 После записи счетчик состояний адреса информации о первой ОЭК отказавшей функции на третий вход БУК 8 с одиннадцатого выхода БМУ 26 поступает сигнал, разрешающий БУК поиск необходимой ОЭК и управ5 ление ее выполнением. Прохождение синхроимпульсов через элементы И 120 и 121 разрешается нулевыми сигналами с триггера 132 и узла 135. Нулевой сигнал с триггера 132 означает, что рассматривае0 мая ОЭК не является последней в множестве ОЭК для отказавшей функции. Нулевой сигнал с узла 135 означает, что рассматриваемая ОЭК не может быть выполнена в текущем состоянии ВС. За счет элемента

5 задержки 116 элемент И 121 срабатывает раньше элемента И 120, что обеспечивает сначала чтение информации об ОЭК отказавшей -функции из памяти состояний и лишь потом увеличение адреса в счетчике

0 состояний 125. Таким образом, информация о первой ОЭК отказавшей функции записывается в регистр 131 (состояние АП группы, требуемое для выполнения данной ОЭК), триггер 132 (признак того, является ли дан5 ная ОЭК последней для отказавшей функции) и счетчик 126 (адрес первого управляющего слово данной ОЭК). Требуемое состояние АП группы сравнивается в ВС с текущим состоянием. В случае несовпадения состояний значение счетчика 125

состояния увеличивается на единицу и происходит выборка информации последующей ОЭК отказавшей функции и так далее до тех пор, пока не будет рассмотрена информация о последней ОЭК функции или не будет найдена подходящая ОЭК. 8 первом случае единичный сигнал с выхода триггера 132 Поступает через элемент И 137 на вхо- Ды элемента 138 задержки и элемента И 139, обеспечивая выработку импульсного сигнала (длительностью не менее трех тактов машинного цикла ЦП 1, что определяется элементом 138 задержки), поступающего на вход Р8П 3 (блокировка ВПП). вход 32 СБ ЦП, элемент ИЛИ 16(установка сигнала на вхо- Де 34 ГТ ЦП) и БМУ 26 (переход на микропрограмму передачи управления подпрограмме).

Во втором случае единичный сигнал с ыхода узла 135, поступая на элементы И 20 и 121, прекращает подачу синхроимпульсов на элементы подсистемы поиска ОЭК. При этом в счетчике 125 состояний остается адрес информации о рассматрива- Јмой ОЭК, а в счетчике 126 - адрес ее первого управляющего слова. Этот же сигнал, поступая на входы элемента 140 задержки и Элемента И 141, обеспечивает выработку импульсного сигнала, поступающего на вход БП 4 и через зле- ментИЛИ 25 на РА 9, по которому а РА 9 восстанавливаются начальные адреса Входных и выходных данных в ВПП и их длина. Кроме этого, единичный сигнал с выхода узла 135, поступая на элемент И 124 и через элемент 122 задержки на элемент 14 123, разрешает работу подсистемы управления выполнением ОЭК. За счет элемента 122 задержки обеспечивается сначала чтение управляющих сигналов ОЭК из узла 128, 8 затем увеличение адреса в счетчике 126, Формат управляющих сигналов ОЭК приведен на фиг. 15. Первое поле (информация для АП) записывается из узла 128вМБР 133, а сигналы, разрешаемые в полях 2-9. записываются в регистр 134. МБР 133 подключен к шине-28 данных, а регистр 134 через элементы ИЛИ 18-24 - к управляющим входам АП группы, РА 9 и ВПП. Кроме того, сигналы с выхода регистра 134 поступают на внутренние элементы подсистемы управления выполнением ОЭК.

ОЭК выполняется следующим образом.

Первое управляющее слово по адресу, находящемуся в счетчике 126, читается из узла 126 в МБР 133 и регистр 134. Управляющие сигналы из регистра 134, поступая на

0

0

5

0

5

0

5

входы АП группы, РА 9 и ВПП, активизируют одну из перечисленных выше элементарных операций МПС. При этом если выполняются операции загрузки в К-й АП константы или кода функции, т.е. информации из МБР 133, то единичный сигнал с элемента И 149 переводит МБР 133 в режим вывода информации. Все остальное время выход МБР 133 находится в третьем, высокоимпедансном, состоянии. Если был запущен некоторый АП, то для дальнейшего продолжения выполнения ОЭК требуется дождаться окончания выполнения функции АП. Для этого сигнал запуск АП (восьмое поле узла 128), поступая на элемент задержки 145 и элемент 146, вырабатывает импульсный сигнал, сбрасывающий в ноль триггер 147, запрещая прохождение синхроимпульсов на а

счетчик 126, МБР 133 и регистр 134. Триггер 147 устанавливается в единичное состояние t лишь по приходу одного из импульсных сиг- налов КВО АП группы. После выполнения очередной элементарной операции адрес счетчика 126 увеличивается на единицу и производится выборка следующего управляющего слова и так далее до тех пор, пока не будет выполнена последняя операция ОЭК или не произойдет отказ при выполнении некоторой функции АП группы. В первом случае единичный сигнал признака конца ОЭК (девятое информационное поле узла 128) запрещает прохождение синхроимпульсов на счетчик 126, МБР 133 и регистр 134, а также, поступая на элемент И 142, обеспечивает выработку импульсного сигнала, поступающего на БМУ 26 и информирующего последний об успешном выполнении ОЭК. Во втором случае нулевой сигнал с узла 135 запрещает работу подсистемы управления выполнением ОЭК и активизирует работу подсистемы поиска ОЭК. которая продолжает дальнейший поиск ОЭК начиная со следующей ОЭК после последней рассмотренной, так как в счетчике состояний сохранился адрес информации о последней рассмотренной ОЭК.

Управляет работой всех блоков устройства в активном режиме 26 блок микропрог- раммного управления. В качестве. синхронизирующего элемента используется двухтактный генератор 153 импульсов, синхросигналы с которого поступают на узел БМУ после появления сигнала Пуск на единичном входе триггера 152. Этим же сигналом производится начальная установка (обнуление) счетчика 168. С выходов элементов И 155 первый тактовый импульс поступает на вход записи регистра 154 и L элементы И 159, второй - на элемент И167.

По первому синхроимпульсу производится запись и выдача управляющих сигналов из регистра 154 на внутренние узлы ЕМУ и в узлы устройства. По второму синхроимпульсу происходит прибавление единицы к содержимому счетчика 168.

На вход БМУ, помимо сигнала Пуск, поступают сигналы с выходов УС 7, БУК 8, РА 9, а также ПЗх ЦП 30, КВО АП 37, ЧТ ЦП 29, ЗЗх ЦП 33.

В БМУ используется система с жесткой последовательностью микрокоманд в унитарных кодах (каждому разряду микрокоманды сопоставляется управляющий сигнал БМУ 26). Работу БМУ поясняет таблица, представляющая собой последовательность и кодировку микрокоманд (расшивку) находящихся в памяти 151 микрокоманд.

Разряды микрокоманды (МК) поступают: ХО - на элементы И-ИЛИ 160, ИЛИ-НЕ 161; Х1 - на единичный вход триггера 156; Х2 - на нулевой вход триггера 156; ХЗ - на вход дешифратора 11; Х4- на вход элемента И 17; Х5 - на входы регистра 5 и элемента ИЛИ 22; Х6 - на вход элемента ИЛИ 159; Х7 - на вход элемента ИЛИ 23; Х8 - на вход элемента И 159; Х9 - на вход триггера 13; Х10 - на входы регистра 3 и нулевой вход триггера 152; Х11 и Х12-на второй и третий входы БУК 8 соответственно.

При наличии единицы в нулевом или двенадцатом разрядах микрокоманды БМУ находится в режиме ожидания до прихода одного из внешних сигналов на элемент И-ИЛИ 160. При нулевом состоянии этих разрядов в очередном такте производится прибавление единицы в счетчик 168 и выборка очередной микрокоманды из памяти 151 микрокоманд в регистр 154.

БМУ 26 работает следующим образом.

При запуске БМУ {появление сигнала Пуск на единичном входе триггера 152) на выходе регистра 154 появляется нулевая МК, которая переключает триггер 156 в единичное состояние. Устройство посылает в это время сигнал на вход 33 ЗЗхСП. Сигнал ПЗхЦП 30 поступает на вход элемента И 157 и производит выборку первой микрокоманды в регистр 154, которая сбрасывает триггер 156.

С помощью этой МК БМУ 26 управляет передачей входных данных из ВПП в АП 2. Так как сигнал данные на входе ОК/Д АП является альтернативным по отношению к сигналу команда, то в пятом разряде МК при записи/чтении АП 2 находится нуль. Поскольку в структуре МПС может содержаться несколько АП2, то на вход каждого и

0

5

0

5

0

5

0

5

0

5

них должна идти соответствующая линия с выхода дешифратора 11. Инициализация того или иного АП 2 определяется содержимым регистра 10 (все линии, идущие на входы и выходы АП 2, выведены косыми линиями на общую шину). Окончание передачи данных в АП 2 происходит при появлении сигнала из регистра 9. по которому выбирается вторая микрокоманда. Вторая микрокоманда управляется записью кода операции в АП 2, затем на вход .42 ЗП АП поступает сигнал - выполняется третья мик- рокоманда. После этого БМУ переходит в режим ожидания - выполняется четвертая микрокоманда (АП 2 обрабатывает входные данные).

При появлении сигнала на выходе 37 КВО АП (сигнал импульсного характера длительностью, равной времени выборки очередной команды из памяти 151 микрокоманд) производится выборка пятой микрокоманды, с помощью которой проверяется исправность АП 2. Если на выходе триггера 58 неисправности устанавливается единичный сигнал, то с выхода узла 7 сиг- нал поступает через элемент ИЛИ 163 на С-вход счетчика 168, по которому разрешается запись в счетчик 168 содержимого его информационных входов. В данном случае на информационных входах счетчика 163 присутствует код 9, то есть осуществляется принудительная адресация к девятой микрокоманде.

Если АП 2 исправен, то с выхода узла 7. через элемент ИЛИ 163 на вход счетчика 168 сигнал не поступает, происходит выборка шестой микрокоманды, которая управляет чтением результата из АП 2 в ВПП. Окончание передачи результата в ВПП происходит при появлении сигнала из регистра 9, по которому выбирается седьмая микрокоманда. Эта микрокоманда сбрасывает в нуль триггер 13, чем снимается захват шин ЦП 1. Восьмая микрокоманда останавливает БМУ 26.

При помощи девятой микрокоманды осуществляется передача кодов из РКОП 5 и РН 10-в счетчик 125 состояний БУК 8 для поиска и выполнения ОЭК неверно выполненной функции АП. При помощи десятой микрокоманды осуществляется передача управления БУК 8, т.е. запускается БУК 8 для поиска и управления выполнением ОЭК. При этом БМУ находится в режиме ожидания до прихода сигнала на элемент И-ИЛИ 160 от БУК 8, означающего успешное выполнение ОЭКфункции. При появлении сигнала от БУК 8 на элемент И-ИЛИ 160 производится выборка одиннадцатой микрокоманды, с

помощью которой сбрасывается в нуль триггер 13 (снимается захват шин ЦП 1), Двенадцатая микрокоманда останавливает БМУ 26. При поиске и выполнении ОЭК функции (десятая микрокоманда) БУК 8 может не найти ОЭК, которая может быть выполнена в текущем состоянии АП группы МПС. В этом случае БУК 8 вырабатывает импульсный сигнал, поступающий через элемент ИЛИ 163 на Ct-вход счетчика 168, по которому разрешается запись в счетчик 168 содержимого его информационных входов. В данном случае йа входах счетчика 168 присутствуе- код 13. так как этот же сигнал поступает на один из информационных входов счегчика 168. Таким образом, осуществляется принудительная адресация к тринадцатой микро- Команде.

При помощи тринадцатой микрокоманды устройство осуществляет переход к соответствующей подпрограмме. При этом БМУ Находится в режиме ожидания до прихода сигнала с выхода элемента 165 задержки. Сигналы, поступающие с выхода 29 ЧТ ЦП, разрешают выборку кода команды безусловного перехода и адреса перехода на общую магистраль 28 данных. Сигналы эти разнесены во времени по машинным циклам ЦП 1. Первый сигнал через элемент И 158 и счетчик 162 поступает на аход дешифратора 166, на соответствующем выходе ко- фрого появляется сигнал, поступающий на выборку МБР 110. Аналогично следующие рва сигнала с выхода 29 ЧТ ЦП производят сыборку содержимого МБР 109 и МБР 108 (щрес перехода). При этом выход дешифратора 166, соединенный с элементом НЕ 104, соединен также с элементом 165 задержки, сигнал с которого поступает по окончании сигнала с выхода 29 ЧТ ЦП, осуществляя переход к четырнадцатой микрокоманде, которая снимает блокировку ВПП и останавливает БМУ 26.

В процессе обработки информации в МПС данное устройство выявляет обоаще- ние к аппаратно реализуемой функции, выставляет запрос ка захват шин ЦП 1 в случае появления такого обращения, выдает информацию на соответствующие узлы устройства из блока памяти 4 и прежде, чем принять на себя управление системой, подготавливает обратный переход в основную программу (засылает в регистр команд ЦП 1 команду возврата из подпрограммы PET), a также подготавливает возможный переход к соответствующей подпрограмме.

Получив управление, устройство определяет АП 2, который будет производить обработку функции, и засылает в него дан

0

5

0

5

0

5

0

5

ные по общей магистрали 28 данных из ВПП в режиме прямого доступа к памяти. Сигналы с выхода БМУ 26 поступают на входы дешифратора 11 (инициирование соответствующего АП 2), элемента И 17 (режим записи в АП 2), регистра 3 (формирование адресов данных), элемента ИЛИ 19 (режим чтения ВПП). По окончании записи данных в АП 2 производится запись в него кода операции также по общей магистрали 28 данных. При этом сигналы с выхода БМУ 26 поступают на входы регистра 5 (выборка кода операции), дешифратора 11, элемента И 17 (режим записи в АП 2). После этого с выхода БМУ 26 поступает сигнал на входы дешифратора 11 и через элемент ИЛИ 24 на вход 42 ЗП АП, при которых начинается обработка данных (вычисление функции). Затем устройство ожидает окончания вычисления функции в АП 2. При появлении сигнала с выхода 37 КВО АП устройство проверяет исправность АП 2, производящего вычисление функции. Для этого с выхода 26 подается сигнал на вход дешифратора 11, выходы которого поступают на узел 7. АП 2 выставляет сигнал НС АП 35 (в случае неисправности АП 2), который также поступает на узел 7. Затем производится либо выдача результата из АП 2 в ВПП (если АП 2 исправен), либо поиск и заполнение ОЭК функции, которая может быть выполнена в текущем состоянии АП группы МПС (если функции АП 2 выполнены неверно).

В первом случае производятся аналогичные действия со стороны устройства. С выхода БМУ 26 сигналы поступают на вход дешифратора 11, в регистр 9 (формирование адресов результата), на вход элемента ИЛИ 18 (режим чтения АП 2 и записи в ВПП). После этого снимается захват шин ЦП 1 сигналом из БМУ 26 на вход триггера 13 и останавливается БМУ 26. В результате ЦП переходит к обработке дальнейшей программы,

Во втором случае БМУ осуществляет передачу в БУК 8 АП и кода функции и передает управление МПС БУК 8. БУК осуществляет поиск ОЭК, которая может быть выполнена а текущем состоянии АП группы, и при нахождении такой ОЭК управляет ее выполнением. Если в процессе выполнения ОЭК произошел отказ (сигнал НС АП совместно с сигналом КВО АП) БУК продолжает поиск ОЭК. При успешном выполнении ОЭК БУК 8 возвращает управление МПС БМУ 26, который снимает захват шин ЦП 1 и останавливает работу БМУ 26. В результате ЦП 1 переходит обработке дальнейшей программы. Если БУК 8 не нашел ОЭК, которая

вторым входами одиннадцатого элемента И и входом первого элемента ИЛИ и образует группу выходов блока, при этом в блоке управления композициями первый тактовый выход генератора импульсов соединен с первым входом двенадцатого элемента И и вторым входом девятого элемента И, выход которого соединен со счетным входом счетчика управляющих сигналов, выход которого соединен с адресным входом первого узла памяти, информационный выход которого соединен информационными входами первого и второго регистров, синхровходы которых соединены с выходом десятого элемента И и третьим входом одиннадцатого элемента И, четвертый вход и выход которого соединены -соответственно с выходом первого элемента ИЛИ и первым разрешающим входом второго регистра, соединенного с входом второго элемента НЕ, выход которого соединен с вторым разрешающим входом второго регистра, установочный вход которого соединен с выходом первого элемента НЕ, второй вход логического условия узла состояний соединен с входом второго элемента ИЛИ, выход которого соединен с вторым входом третьего элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, выход которого соединен с единичным входом первого триггера, выход которого соединен с вторым входом десятого элемента И и третьим входом девятого элемента И, четвертый вход которого соединен с выходом четвертого элемента задержки, вход которого соединен с вторыми входами второго, восьмого и двенадцатого элементов И, первыми входами шестого и тринадцатого элементов И, вторым выходом узла состояний, входом пятого элемента задержки и третьим входом десятого элемента И. четвертый вход которого соединен с вторым тактовым выходом генератора импульсов и третьим входом второго элемента И, выход которого соединен с синхровходами счетчика управляющих сигналов, второго триггера и третьего регистра, информационные входы которых соединены с информационным выходом, второго узла памяти, адресный вход которого соединен с выходом счетчика состояний, синхровход которого соединен с выходом первого элемента задержки и вторым входом первого элемента И, выход которого соединен с установочным входом счетчика состояний, вторым входом третьего элемента ИЛИ, нулевым входом второго триггера и установочным входом третьего регистра, группа выходов которого соединена с группой информационных входов узла состояний, третий вход логического условия

которого соединен с выходом второго элемента задержки и третьим входом двенадцатого элемента И, выход и четвертый вход i которого соединены соответственно со счетным входом счетчика состояний и выходом второго триггера, соединенного с вторым входом тринадцатого элемента И. выход которого соединен с первым входом

четвертого элемента И и входом шестого элемента задержки, выход которого соединен с вторым входом четвертого элемента И, выход пятого элемента задержки соединен с вторым входом шестого элемента И, выход восьмого элемента И соединен с входом седьмого элемента задержки и первым входом пятого элемента И, второй вход которого соединён с вйходом седьмого элемента задержки, выход третьего элемента задержки соединен с вторым входом седьмого эле0 мента И, выход которого соединен с нулевым входом первого триггера, третий информационный вход счетчика состояний и вход режима работы второго регистра подключены к шине нулевого потенциала уст5

роиства.

при этом в узле состояний выход регистра соединен с первым информационным входом дешифратора, второй информационный вход которого соединен с выходом шифратора, группа информационных входов которого соединена с выходами элементов И группы, входами элементов задержки группы и группой входов элементов ИЛИ. выход которого соединен с разрешающим входом шифратора и входом элемента задержки, выход которого соединен с разрешающим входом дешифратора, группа выходов которого соединена с единичными входами триггеров группы, выходы которых соединены с вторыми входами элементов

группы, выходы которых соединены с группой входов элемента И, нулевые входы

триггеров группы образуют установочный вход узла.

Фиг,1

12

jn цп 5t

Ul

3

UnJ

от вук

ФМГ.4

И

2J

«Г

urn UIK

щ

HJ

w

Z°J

пчсм

и PKonS. pA9.

f- rco

«N Ј

«i

i „I

..

тП оо

I

6 Jttdb

ШШ1

Фиг: ii

t VCT

Of 8

Фиг 2

|кМ«

НПИ U «м««та uftu Л

1«Jt

EJ. elSiw/ CJL SV

I

I

йй

ss -I

jr «w

Ott «U

«U4«

MWT

Ю

JL

n

-CDгы

-MIW w«

«uv эй

CD3A.V

«5v о«я

- ttjv w

MW 0«Х

fiV

avw

iiC20Zt

Фиг. 5

| Электроника, 1980, № 10, с.49, фиг.5 | |||

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-12-30—Публикация

1989-06-27—Подача