. Изобретение относится к вычислительной технике, а именно к множитель но-делительным устройствам гибридных вычислительных машин и является усовершенствованием известного устройстИз основного авт. CB,jp411472 известно цифроаналоговое множительноделительное устройство, используемое в .гибридных вычислительных машинах для деления или умножения аналогового напряжения на опорное напряжение, пропорциональное коду делителя (множителя) . Это устройство содержит аналого-цифровой .преобразователь,.первый вход которого соединен с выходом источника опорного напряжения, а второй вход соединен с выходом источника аналогового напряжения. На входе источника опорного напряжения установ лен езлок управления (опорным напряжением) . Устройство позволяет выполнить де ление или умножение аналогового напряжения на нормализованный цифровой код, пределы изменения которого от 10Q,.0 до 111.,, соответствуют изменению опорного напряжения от 0,5 13 до Uon . Однако при кодах множителя (делителя) , меньших 111,,.1, и максимальном входном аналоговом напряжении возникает переполнение на выходе аналого-цифрового преобразователя. Если код множителя, например, равняется 100.,,О, при этом опорное напряжение на входе аналого-цифрового преобразователя будет равно 0,5 то диапазон входных аналоговых напряжений сужается до 0,5 При увеличении вдвое опорного нашряжения уменьшается точность преооразования, так как при любых величинах входного аналогового напряжения старший разряд аналого-цифрового преобразователя не используется. Кроме того, увеличение опорного напряжения связано с изменением электрической схема аналого-цифрового преобразователя и нередко влечет за собой снижение быстродействия, Целью дополнительного изобретения является повышение точности. Поставленная цель достигается тем, что в цифроанал1оговое множительноделительное устройство введены блок задания пороговых напряжений, двухпороговый дискриминатор, сумматор и коммутатор, причем вход блока задания -пороговых напряжений подключен к выходу источника опорного напряжения, выход подключен к первым входам двухпорогового дискриминатора и коммутатора, первый выход которого подключе к первому входу сумматора, вторые вхды сумматора и двухпррогового дискриминатора подключены к выходу источника аналогового напряжения, выход двухпорогового дискриминатора подключен ко второму входу коммутатора, выход сумматора подключен ко второму входу аналого-цифрового преобразователя, а второй выход коммутатора подключен ко второму входу аналго-цифрового преобразователя.

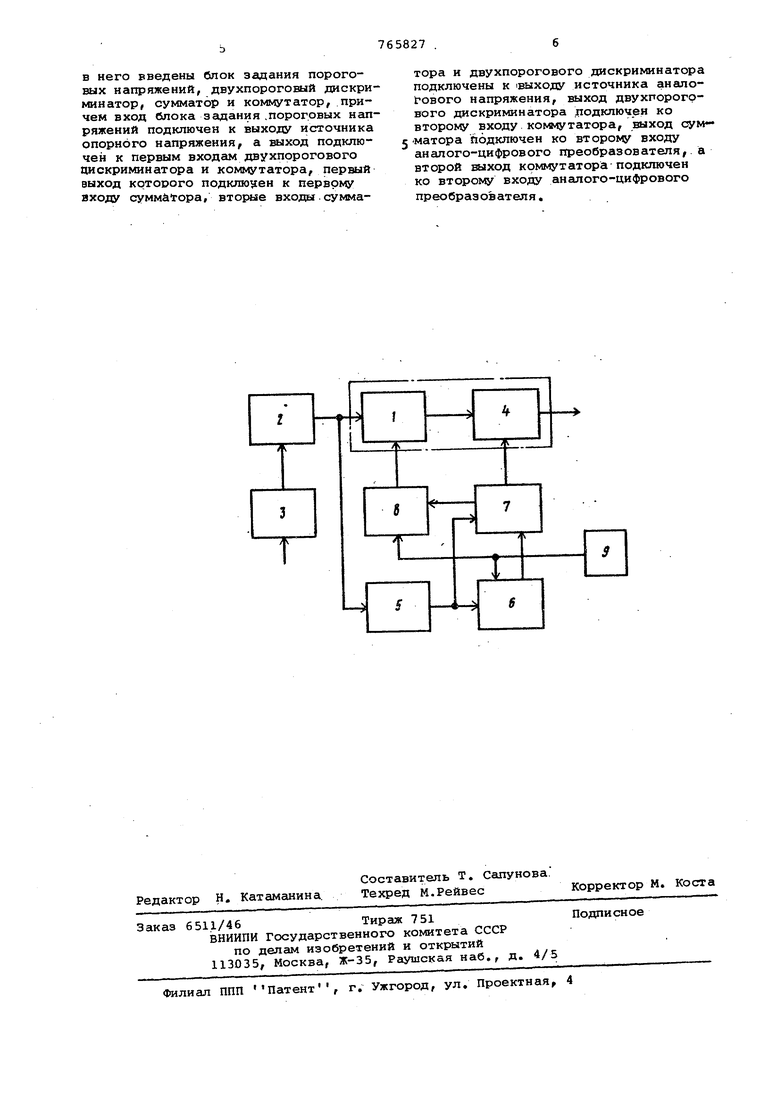

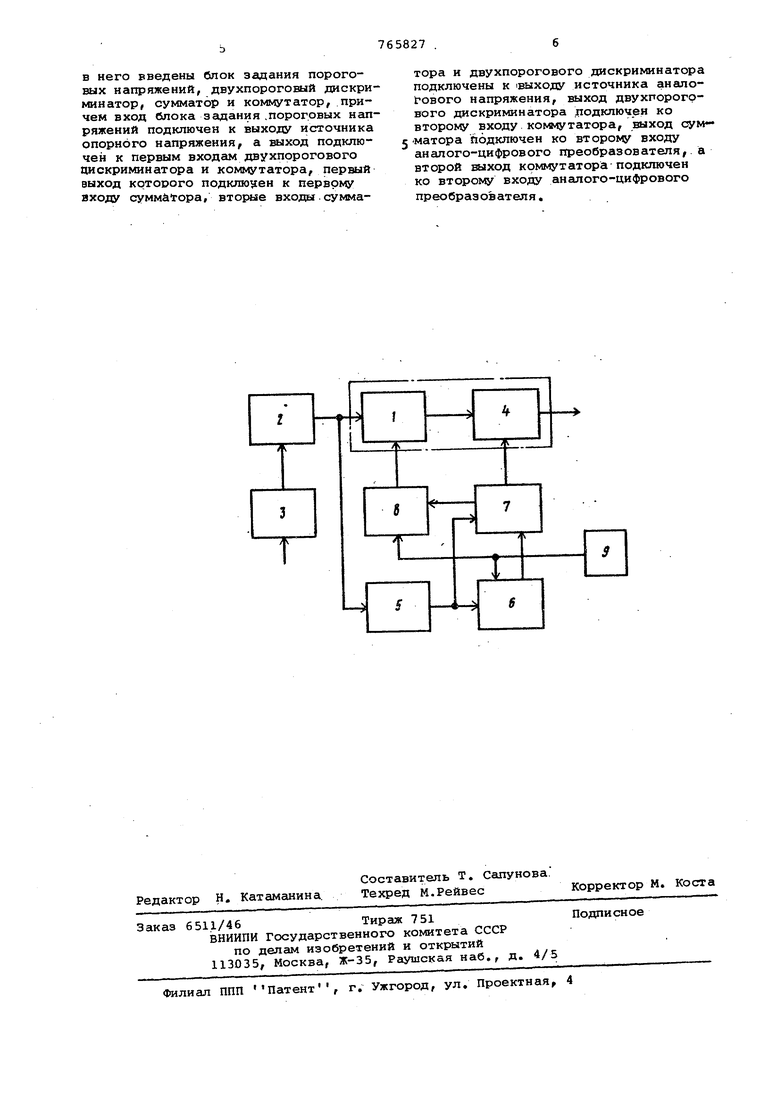

На чертеже представлена блок-схема предлагаемого устройства.

Оно содержит аналого-цифровой преобразователь 1, источник опорного, напряжения 2, блок управления 3, выходной регистр числа 4, блок задания пороговых напряжений 5, двухпорогоБЫй дискриминатор б, коммутатор 7, сумматор 8, источник аналогового напряжения 9.

В цифроаналоговом множительно- делительном устройстве аналого-цифровой преобразователь 1 соединен первым входом с источником опорного нап ряжения 2, на входе которого включен блок управления 3. В выходной регистр числа 4 аналого-цифрового преобразователя 1 введен дополнительный разряд, вес которого в два раза больше старшего разряда прежнего регистра числа аналого-цифрового преобразователя. К выходу источника опорного напряжения 2 подключен блок задания пороговых напряжений 5, выход которого связан, с первыми входами-двухпорогового дискриминатора 6 и коммутатора 7. Второй вход KOvsMyTSiTopa 7 соединен с выходом двухпорогового дискриминатора б, связанного вторым входом с источником аналогового напряжения S и с перним входом сумматора 8, Выход сумматора 8 соединен со вторым входом аналого-цифрового преобразователя 1, Второй вход сумматора 8 подключен к первому выходу коммутатора l,f второй выход которого соединен с дополнительным разрядом регистра числа 4,

Блок задания.пороговых напряжений 5 предназначен для формирования положительного и отрицательного пороговых напряжений, равных по величине текущему значению опорного напряжения ffа -входе аналого-цифрового преобразователя 1.

Устройство работает следующим образом.

На вход блока управления. 3 сывают код шожителя .(делителя) , а на входы двухпорогового дискриминатора 6 и суммсРгора 8 подают аналоговое напряжение, подлежащее преобразованию. Опорное напряжение, пропорциональное коду на входе блока управления 3, с выхода источника опорного напряжения 2 поступает на вход аналоло-цифрового преобразователя 1 и на вход блока задания,пороговых . напряжений 5. С выхода блока задания пороговых напряжений 5 положительное и отрицательное пороговые напряжения, равные по величине текущему значению оп.орного напряжения на входе аналого-цифрового преобразователя 1, поступают на входы двухпо рогового дискриминатора б и коммутатора 7. Входное аналоговое напряжение сравнивают в двухпороговом дискриминаторе б по величине с опорным напряжением. Если аналоговое напряжение по величине окажется меньше опорного напряжения, на выходе двухпорогового дискриминатора б отсутствует сигнал и коммутатор 7 остается в исходном сос.тоянии, .На второй вход сумматора 8 не поступает пороговое.напряжение из коммутатора 7. Аналоговое напряжение через сумматор 8 поступает на вход аналого-цифрового преобразователя 1, Если аналоговое напряжение по величине окгикется больше текущего значения опорного напряжения, на выходе двухпорогового дискриминатора б появится сигнал Этот сигнал поступает на второй вход коммутатора 7, По этому сигналу коммутатор 7 записывает единицу в дополнительный раз.ряд регистра числа 4 и подключает выход блока задания пороговых напряжений 5 ко второму входу сумматора В. С выкода блока задания пороговых напряжений 5 на второй.вход сумматора 8 поступает пороговое напряжение, равное по величине опорному напряжению и обратное по знаку аналоговому напряжению, на первом входе сумматора 8, Разностное.напряжение с выхода сумматора 8 поступает на второй вход аналого-цифрового преобразователя 1 и преобразуется в код обычным способом поразрядного уравновешивания. Выходной код аналого-цифрового преобразователя 1 записывают в основные разряды регистра числа 4, Таким образом устранено переполнение на. выходе аналого-цифрового преобразователя 1,

Предлагаемое -щифрогшал.оговое множительно-делительное устройство позволяет осуществить y ffloжeниe (делени без снижения точности в полом диапазне входного аналогового напряжения н входе аналого-цифрового преобразоваг теля. 1,

Формула изобретения

Цифроаналоговое множительно-делительное устройство по авт, ев, .№ 411472, отличающее ся тем, что, с целью повышения точности

В него введены блок задания пороговых напряжений, двухпороговый дискриминатор, сумматор и коммутатор, причем вход Лпока задания .пороговых напряжений подключен к выходу источника опорного напряжения, а выход подключен к первым входам двухпорогового дискриминатора и коммутатора, первый выход КОТОРОГО подключен к первому входу сумматора, вторые входы.сумматора и двухпорогового дискриминатора подключены к выходу источника анапоЬового напряжения, выход двухпорогового дискриминатора подключен ко второму входу коммутатора, выход сум- -матора Подключен ко второму входу аналого-цифрового преобразователя, а второй выход коммутатора подключен ко BTopONV входу аналого-цифрового преобразователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровое множительное устройство | 1983 |

|

SU1117655A1 |

| ТАНКОВЫЙ БАЛЛИСТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 1979 |

|

SU1840108A1 |

| Устройство для определения статистических характеристик непрерывных случайных величин | 1981 |

|

SU1012270A1 |

| Функциональный генератор | 1980 |

|

SU883931A1 |

| Функциональный генератор | 1979 |

|

SU781839A1 |

| Функциональный преобразователь | 1979 |

|

SU830430A1 |

| Устройство для измерения параметров магнитного поля | 2018 |

|

RU2696058C1 |

| Множительно-делительное устройство | 1978 |

|

SU763915A1 |

| ЧАСТОТОМЕР ДЛЯ ПРОМЫШЛЕННЫХ ЭЛЕКТРИЧЕСКИХ СЕТЕЙ | 2006 |

|

RU2326390C1 |

| Устройство для определения распределения солености воды | 1990 |

|

SU1755157A1 |

Авторы

Даты

1980-09-23—Публикация

1978-10-03—Подача