онного сумматора подключены к нечет ным разрядам третьей группы информа ционных входов коммутатора, четные разряды которой соединены с выходам элементов ИЛИ группы, подключенньйс первыми входами к выходам соответст вумщих четилх разрядов комбинационного сумматора, а входами к соответствующим выходам распределителя импульсов, причем четвертая группа информационных входов коммутатора соединена с шиной потенциала логического нуля. 2. Устройство по п.1, о т ли чающееся тем, что каждый блок сдвига кода последовательного П1«ближения содержит группу элементов НЕ, группу элементов ИЛИ, две группы элементов И, элемент НЕ и регистр, выходы которого являются выходами блока сдвига кода последов тельного приближения,, а тактирующий вход соединен с выходом элемента НЕ подключенного входом к тактирующему входу блока сдвига кода последовательного приближения, причем каждый л-й элемент И первой группы (, где m - количество элементов в группе) соединен первым входом с инфо)мационным входом блока сдвига кода последовательного приближения, вторым входом - с i-м управляющим входом блока сдвига кода последовательного приближения и с входом-t-го элемента НЕ группы, а выходом - с первым входом i-ro элемента ИЛИ группы, подключенного выходом к установочному входу (2i+1)-ro разряда регистра, а вторым входом к выходу i-ro элемента И второй группы, соединенного первым входом с выходом i-ro элемента НЕ, а вторым входом с выходом 21-го разряда регистра, подключенного выходом ()-ro разряда к установочному входу (2t4-2)-ro разряда регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Инкрементный умножитель аналоговых сигналов | 1983 |

|

SU1113820A1 |

| Устройство широкодиапазонного логарифмического аналого-цифрового преобразования | 1988 |

|

SU1571763A1 |

| Цифровой вольтметр | 1985 |

|

SU1337791A1 |

| Инкроментный умножитель аналоговых сигналов | 1982 |

|

SU1057970A1 |

| Множительно-делительное устройство | 1980 |

|

SU902026A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1985 |

|

SU1302435A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1378061A1 |

| Аналого-цифровой инкрементный умножитель | 1982 |

|

SU1057971A1 |

| Аналого-цифровое устройство для вычисления суммы парных произведений | 1980 |

|

SU959106A1 |

| Цифроаналоговый преобразователь с автокалибровкой | 1989 |

|

SU1683176A1 |

1. АНАЛОГО-ЦИФРОВОЕ МНОЖИТЕЛЬНОЕ УСТРОЙСТВО, содержащее накапливакиций сумматор, соединенный выходами свыходами устройства, а инфор- , ма1щрнными входами - с выходами коммутатора, и два аналого-цифровых преобразователя, каждый из которых содержит цифроаналоговый преобразователь и компаратор, подключенный первым входом к вьгходу цифроаналогового хфеобразователя того же аналого-цифрового преобразователя, а вторым входом - к аналоговому входу соответствукяцего сомножителя устройства, причем выходы компараторов обоих аналого-цифровых преобразователей соединены с соответствующими управляющими входами коммутатора, отличаю- щ е е с я тем. что, с целый повышения быстродействия устройства при сохранении его точности, в него дополнительно введены комбинационный сумматорл группа элементов ИЛИ, распрет- ; делитель импульсов и два блока сдвига SU,,,, 1117655 а«Р G 06 G 7/16; G 06 3 3/00 Г- ----I tCF-, кода последовательного приближения, а каждый аналого-цифровой преобразователь содержит регистр последовательного приближения, подключенный тактирующим входом к шине опорной частоты и к тактирующим входам блоков сдвига кода последовательного приближения, накапливающего сумматора и распределителя импульсов, причем ре-, гистр последовательного приближения первого аналого-цифрового преобразователя соединен выходами с входами цифроаналогового преобразователя первого аналого-цифрового преобразователя, а информационным входом - с Ш)1ходом компаратора того же аналогоцифрового преобразователя и с инфорш мационным входом первого блока сдвига кода последовательного приближес ния, подключенного управляющими входами к выходам распределителя импульсов, а выходами - к первой группе входов комбинационного сумматора и к Первой группе информационных входов коммутатора, соединенного второй группой информационных входов с рой группой входов комбинащюнного Эд сумматора и с выходами второго блока. I :д сдвига кода последовательного прибли:л жения, подключенного упр авлякяцими входами к выходам распределителя импульсов, а информационным входом к выходу компаратора второго аналого-цифрового преобразователя и к информационному входу регистра последовательного приближения второго аналого-ци ового преобразователя, соединенного выходами с входами цифроаналогового преобразователя того же аналого-цифрового преобразователя, а выходы нечетных разрядов комбинаци

Изобретение относится к автомати- ке и вычислительной технике, в частности к устройствам для получения в темпе, поразрядного уравновешивания цифрового кода произведения двух ана логовых сигналов с одновременным получением кодов сомнозштелёй. Известно аналого-цифровое множительное устройство, содержащее генератор тактовых импульсов, делители частоты, генератор развертывающего напряжения, распределитель импульсов компараторы, счетчик, ключи и элемен ты И, ИШ,НЕ-И и НЕ-ИПИ lJ. Недостатками устройства являются пониженное быстродействие и ограниченная область применения из-за от;сутствия преобразования сомножителей в цифровую форму. Известно также аналого-цифровое множительное устройств, содержащее сумматор-вычитатель, коммутаторы, сумматоры по модулю два, блок сдвига триггер управления и два следящих аналого-цифровых .тфеобразователя 2j Недостатком данного устройства является повышенное значение максимального времени формирования кода произведения. Наиболее близким к изобретению является аналого-цифровое множительное устройство, содержащее накапливающий сумматор, соединенный выходами с выходами устройства,, а информационными входами - с выходами коммутатора, и два аналого-цифровых преобразователя, каждый иэ которых содержит реверсивный счетчик, цифроаналоговый преобразователь и компаратор, подключенный первым входом к выходу цифроаналогового преобразователя того же аналого-цифрового преобразователя, а вторым входом - к аналоговому входу соответствукяцего сомножителя устройства, причем выходы компараторов обЬих аналого-цифровых преобразователей соединены с соответствующими управляющими входами коммутатора, подключенного первой и второй группами информационных входов соответственно к прямю и инверсным выходам реверсивного счетчика первого аналого-цифрового преобразователя, соединенного входами с выходами компаратора первого аналого-цифрового преоб-

разователя, а выходами - с входами цифроаналогового преобразователя то-г го же аналого-цифрового преобразователя, причем третья и четвёртая группы информационных входов подключены соответственно к прямым и инверсным выходам реверсивного счетчика второго аналого-цифрового преобразователя, соединенного входами и выходами соответственно с выходами компаратора и входами цифроаналогового преобразователя того же аналого-цифрового преобразователя, а управляющие входы компараторов подключены к выходам блока управления, соединенных тактирукмцим входом с шиной бпорной частоты ТЗ.

Недостатком известного устройства является большое время получения результата умножения, обусловленное возможностью работы только в режимах развертьшающего или следящего аналого-цифрового преобразователя. Время вычисления произведения в следящем режиме на каждом шаге равно двум тактам работы устройства, а в режиме развертывающего преобразования тактов (где h- разрядность представления сомножителей), что ограничивает динамический диапазон скорости из менения входных сомножителей и сужае

область применения устройства. I .

Цель изобретения - повышение быстродействия устройства при сохранении его точности.

Поставленная цель достигается тем что в аналого-цифровое множительйое устройство, содержащее накапливающий сумматор, соединенный выходами с выходами устройства, а информацион ными входами - с выходами коммутатора, и два аналого-цифровых преобразователя, каждый из которых содержит цифроаналоговый преобразователь и компаратор, подключенный рервым входом к выходу цифроаналогового преобразователя того.же аналого-цифрового преобразователя, а вторым входом - к аналоговому входу соответствующего сомножителя устройства, причем выходы компараторов обоих аналого-цифровых преобразователей соединены с соответствующими управляющими входами коммутатора, дополнительно введены комбинационный сумматор, группа элемеитов ИЛИ, распределитель импульсой и два блока сдвига, кода последовательногоприближения, а каждый аналогоцифровой преобразователь содержит регистр последовательного приближения, подключенный тактирующим входом к шине опорной частоты и к тактирующим входам блоков сдвига кода последовательного приближения, накапливанлцего сумматора и распределителя импульсов, причем регистр последовательного приближения первого аналого-цифрового преобразователя соединен выходами с входами цифроаналогового преобразователя первого аналогоцифрового преобразователя, а информационным входом - с выходом компаратора того же аналого-цифрового преобразователя и с информационным вхо1ДОМ первого блока сдвига кода последовательного приближения, подключенного управляняцими входами к выходам распределителя импульсов, а выходами - к первой группе входов комбинационного сумматора и к первой группе информационных входов коммутатора, соединенного второй группой информационных входов с второй группой входов комбинационного сумматора и с выходами второго блока сдвига кода последовательного приближения, подключенного управляющими входами к выходам распределителя импульсов, а информационным входом - к выходу компаратора второго аналого-цифрового преобразователя . и к информационному входу регистра последовательного приближения второго аналого-цифрового преобразования, соединенного выходами с входами цифроаналопового : преобразователя того же аналого-цифрового преобразователя, а выходы нечетных разрядов комбинационного сумматора подключены к нечетным разрядам третьей группы информационных входов коммутатора, четные разряды которой соединены с выходами элементов ИЛИ группы, подключенных первыми входами к выходам соответствующих ; четных разрядов комбинационного сум- матора, а вторыми входами - к соответствующим выходам распределителя импульсов, причем четвертая группа информационных входов коммутатора соединена с шиной потенциала логического нуля.

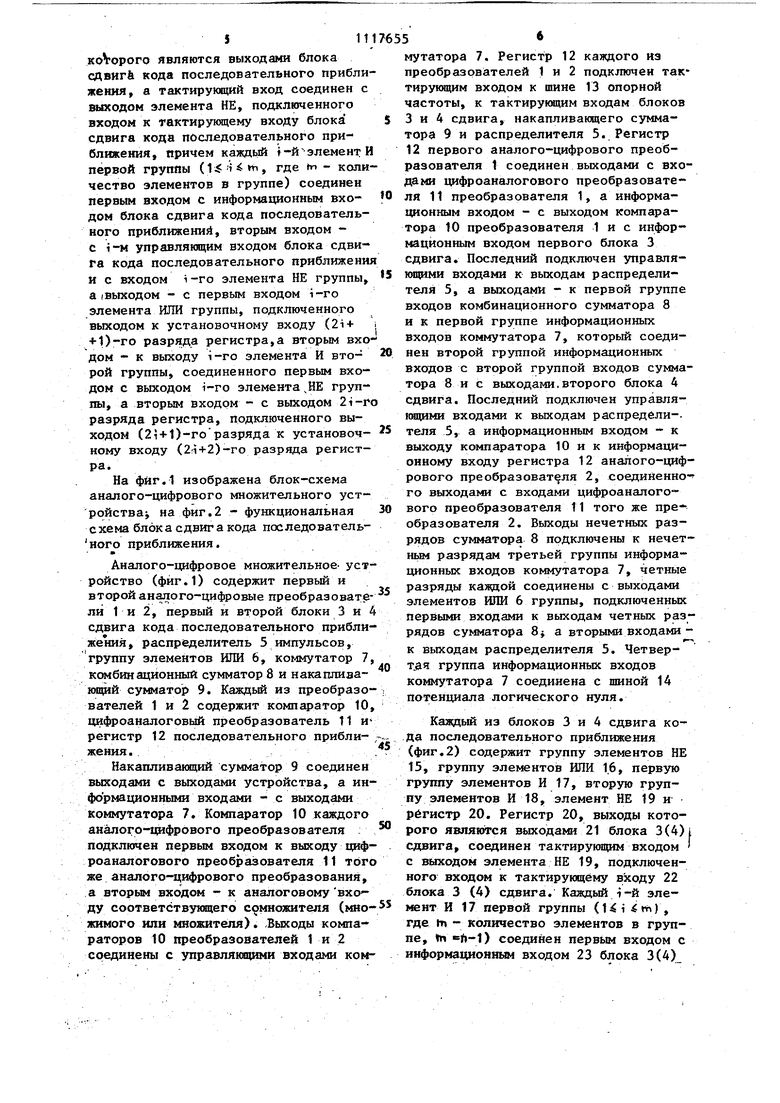

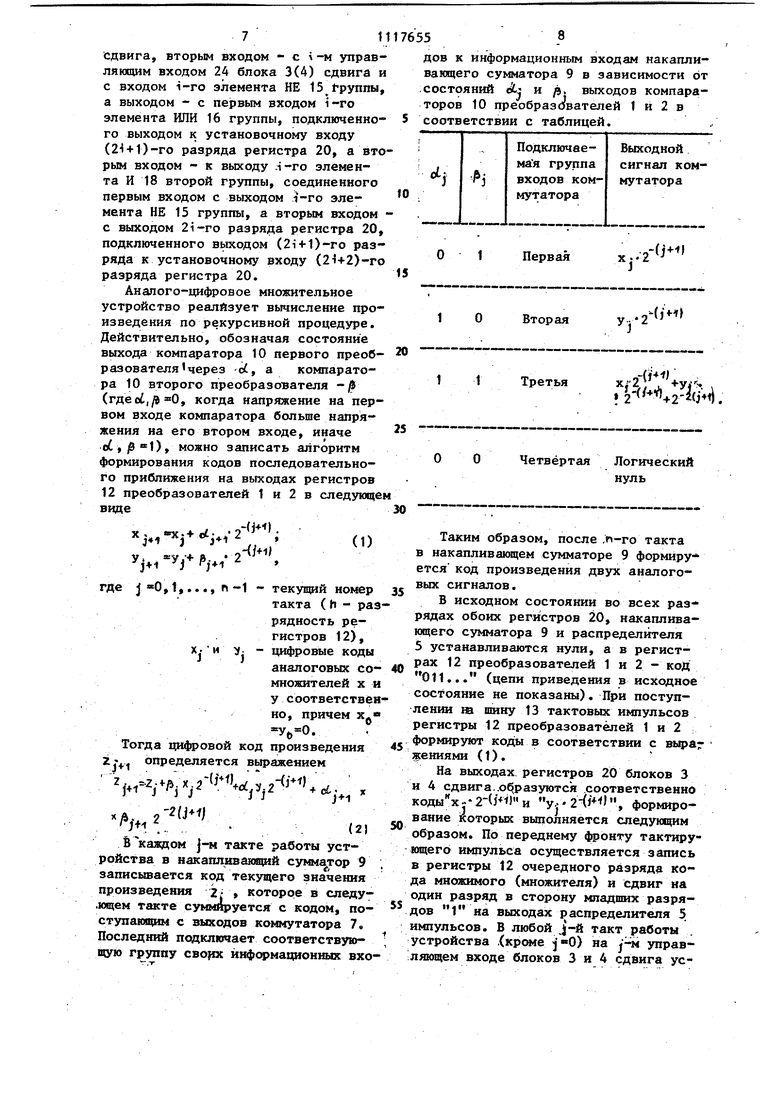

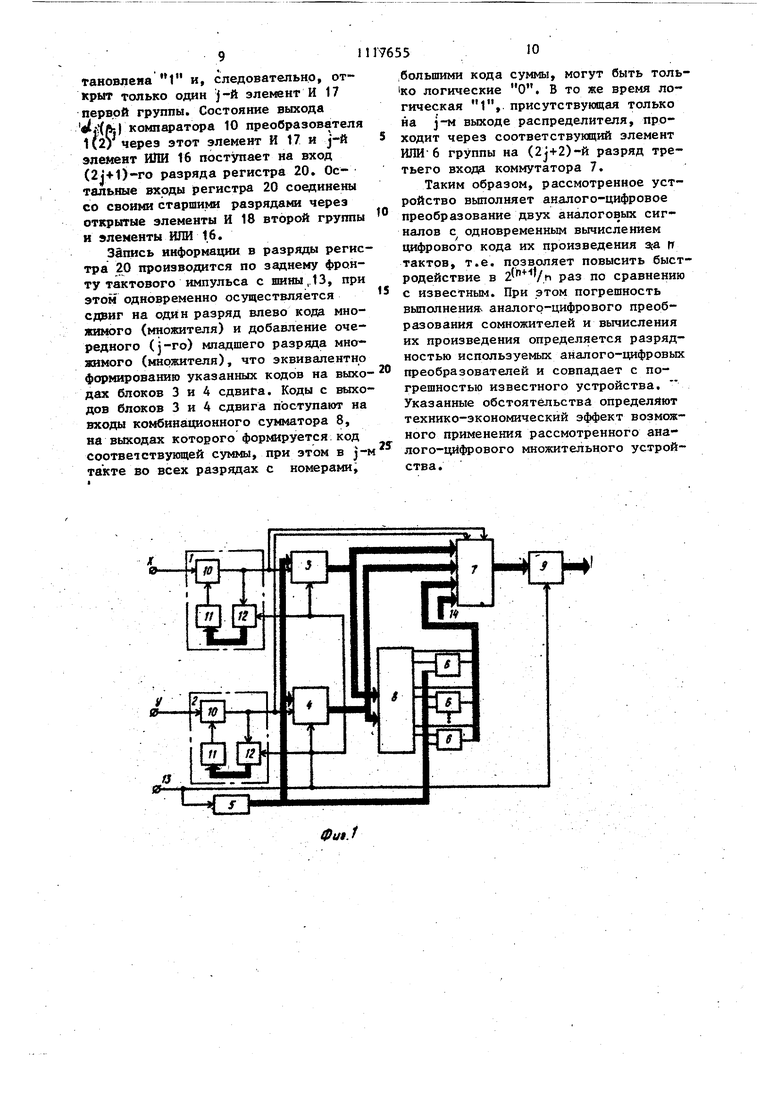

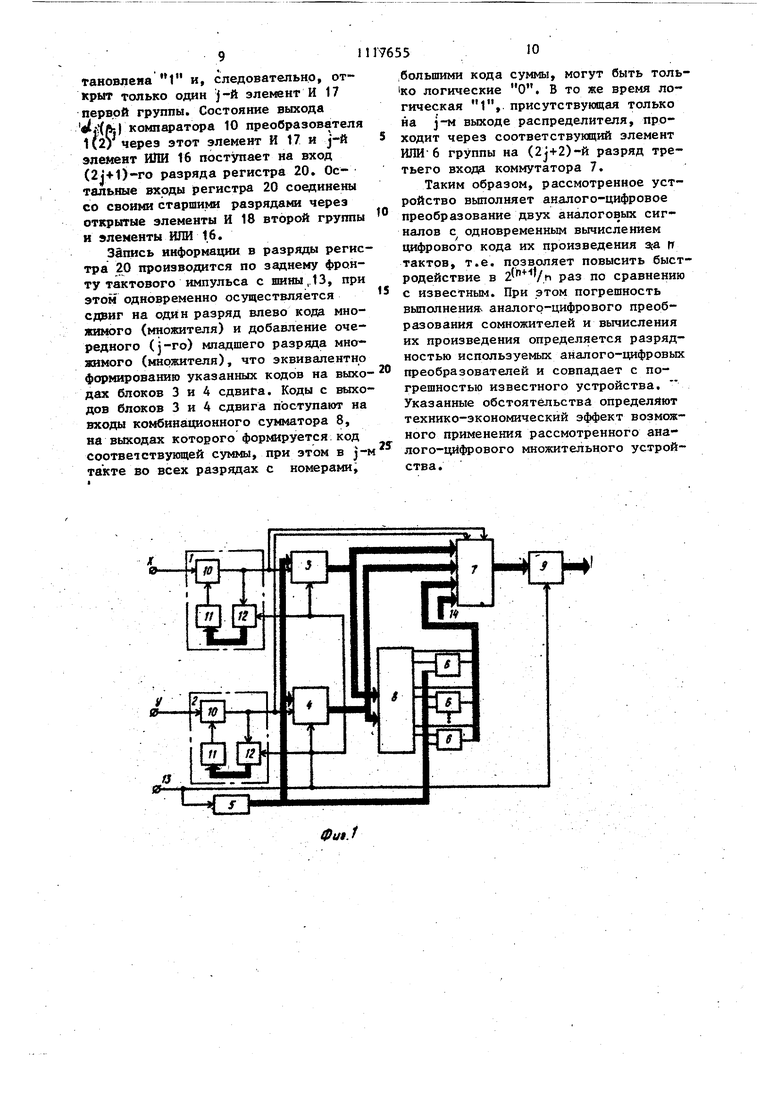

Кроме того, каждьй блок сдвига кода последовательного приближения содержит группу элементов НЕ, группу элементов ИЛИ, две группы элементов И, элемент НЕ и регистр, выходы KoVoporo являются выходами блока сДвигЬ кода последовательного прибли жения, а тактирующий вход соединен с выходом элемента НЕ, подключенного входом к тактирующему входу блока сдвига кода последовательного приближения, причем каждьй t-и элемент И первой группы (1: i ti, где г - коли чество элементов в группе) соединен первым входом с информационньм входом блока сдвига кода последовательного приближений, вторым входом с i-M управлякнцим входом блока сдвига кода последовательного приближения и с входом i-го элемента НЕ группы, а /выходом - с первым входом i-ro элемента ИЛИ группы, подключенного выходом к установочному входу (2i+ +1)-го разряда регистра,а вторым вхо дом - к выходу 1-го элемента И вто- рой группы, соединенного первым входом с выходом i-ro элемента ,НЕ группы, а вторым входом - с выходом 2i-r разряда регистра, подключенного выходом (2i+1)-roразряда к установочному входу (2fi+2)-го разряда регистра. На фйг.1 изображена блок-схема аналого-цифрового множительного устройства; на фиг.2 - функциональная с хема блок а сдвиг а кода пос ледовательного приближения. Аналого-цифровое множительное- устройство (фйг.1) содержит первый и второй аналого-цифровые преобразовате ли 1 и 2, первый и второй блоки 3 и 4 сдвига кода последовательного приближения, распределитель 5 импульсов, группу элементов ШШ 6, коммутатор 7 комбинационный сумматор 8 и накагашвающий сумматор 9. Каждый из преобраэователей 1 и 2 содержит компафатор 10, цифроаналоговый преобразователь 11 ирегистр 12 последовательного приближения. Накапливакшщй сумматор 9 соединен выходами с выходами устройства, а информационными входами - с выходами коммутатора 7. Компаратор 10 каждого аналого-аднфрового преобразователя : подключен первым входом к выходу цифроаналогового преобразователя 11 того же аналого-цифрового преобразования, а вторым входом - к аналоговомувхо- ду соответствуницего сомножителя (множимого или множителя). Выходы компараторов 10 преобразователей 1 и 2 соединены с управляющими входами коммутатора 7. Регистр 12 каждого из преобразователей 1 и 2 подключен так тирукяцим входом к шине 13 опорной частоты, к тактирукщим входам блоков 3 и 4 сдвига, накапливающего сумматора 9 и распределителя 5. Регистр 12 первого аналого-цифрового преобразователя 1 соединен выходами с входами дафроаналогового преобразователя 11 преобразователя 1, а информационным входом - с выходом компаратора 10 преобразователя 1 и с информационным входом первого блока 3 сдвига. Последний подключен управляЮ1цими входами к выходам распределителя 5, а выходами - к первой группе входов комбинационного сумматора 8 и к первой группе информационных входов коммутатора 7, который соединен второй группой информационных входов с второй группой входов сумматора 8 и с выходами,второго блока 4 сдвига. Последний подключен управлякщими входами к выходам распредели-. теля 5, а информационным входом - к выходу компаратора 10 и к информационному входу регистра 12 аналого-цифрового преобразователя 2, соединенного выходами с входами цифроанапого- вого преобразователя 11 того же преобразователя 2. Выходы нечетных разрядов сумматора 8 подключены к нечетным разрядам третьей группы информационных входов коммутатора 7, четные разряды каждой соединены с выходами элементов ИЛИ 6 группы, подключенньк первыми входами к выходам четных разрядов сумматора 8 а вторыми входами к выходам распределителя 5. Четвертая группа информационных входов коммутатора 7 соединена с шиной 14 потенциала логического нуля. Казкдый. из блоков 3 и 4 сдвига кода последовательного приближения (фиг.2) содержит группу элементов НЕ 15, группу элементов ИЛИ 1.6, первую группу элементов И 17, вторую группу элементов И 18, элемент НЕ 19 и регистр 20. Регистр 20, выходы которого являются выходами 21 блока 3(4) сдвига, соединен тактирующим входом с выходом элемента НЕ 19, подключенного входом к тактирующему входу 22 блока 3 (4) сдвига. Каждый i-и элемент И 17 первой группы (14i «) , где It - количество элементов в группе, п ) соединен первым входом с информационным входом 23 блока 3(4) сдвига, вторым входом - с л-м управляккцим входом 24 блока 3(4) сдвига и с входом i-ro элемента НЕ 15 1руппы, а выходом - с первым входом i-ro элемента ИЛИ 16 группы, подключениего выходом к установочному входу ()-гo разряда регистра 20, а вторым входом - к выходу :i-ro элемента И 18 второй группы, соединенного первым входом с выходом 1-го элемента НЕ 15 группы, а вторым входом с выходом 2i-ro разряда регистра 20, подключенного вьпсодом (2i-H)-ro разряда к установочному входу {2-1+2)-го раэряда регистра 20. Аналого-цифровое множительное устройство реализует вычисление произведения по рекурсивной процедуре. Действительно, обозначая состояние выхода компаратора 10 первого преобразователя через -оС, а компаратора 10 второго преобразователя -/9 (гдeoi,, когда напряжение на первом входе компаратора больше напряжения на его втором входе, иначе ct, j8 1), можно записать алгоритм формирования кодов последовательного приближения на выходах регистров 12 преобразователей 1 и 2 в следующем виде 2-(J . yj.i уг р где j«0,t,. текущий номер такта (Ь - раз рядность регистров 12), цифровые коды аналоговых сомножителей х и у соответствен но, причем х Уе,0. . Тогда цифровой код произведения определяется выражением |..c6 -2(JMj Вказвдом j-M такте работы устройства в накапливающий сумматор 9 записывается код текущего значения произведения 2; , которое в следу.ющем такте суммируется с кодом, поступающим с выходов коммутатора 7. Последний подключает соответствующую группу сво информационных вхо 11 8 ионным входам накаплиора 9 в зависимости от .ж , выходов компараиразователей 1 и 2 в таблицей. 0-fJ ервая торая етвёртая Логический нуль Таким образом, после ,п-го такта в накапливакнцем сумматоре 9 формиру ется код произведения двух аналоговых сигналов. В исходном состоянии во всех разрядах обоих регистров 20, накапливающего сумматора 9 и распределителя 5 устанавливаются нули, а в регистрах 12 преобразователей 1 и 2 - код 011... (цепи приведения в исходное состояние не показаны). При поступлении ш шнну 13 тактовых импульсов регистры 12 преобразователей 1 и 2 формируют коДы в соответствии с выра;ениями (1). На выходах, регистров 20 блоков 3 и 4 сдвига,.о1 разуются .соответственно кодых| 2-( yj-2-(, формирование которых выполняется следующим образом. По переднему фронту тактирующего импульса осуществляется запись в регистры 12 очередного разряда кода множимого (множителя) и сдвиг на один разряд в сторону мпадших разрядов 1 на выходах распределителя 5. импульсов. В любой j-й такт работы устройства .(крсм4е ) на у-м управ:ляющем входе блоков 3 и 4 сдвига установлена t и, следовательно, открьрр только один j-й элемент И 17 первой группы. Состояние выхода ) компедатора 10 преобразователя 1(2) через этот элемент И 17 и j-й элемент ШШ 16 поступает на вход (2j41)ro разряда регистра 20, Остальные входы регистра 20 соединены со своими старшиш разрядами через открытые элементы И 18 второй группы и элементы ИЛИ 1.6.

Запись информации в разряды регистра 20 производатся по заднему фронту тактового импульса с нины ,.13, при этом одновременно осуществляется сдвиг на один разряд влево кода множи югo (множителя) и добавление очередного (j-ro) мпадшего разряда множимого (множителя), что эквивалентно формированию указанных кодов на выходах блоков 3 и 4 сдвига. Коды с выходов блоков 3 и 4 сдвига поступают на входы комбинационного сумматора 8, на выходах которого формируется:код соответствующей суммы при этом в j-м такте во всех разрядах с номерами.

суммы, могут быть толь О. В то же время лоприсутствующая только

на J-M выходе распределителя, проходит через соответствующий элемент ИЛИ6 группы на (2|+2)-й разряд третьего входа коммутатора 7.

Таким образом, рассмотренное устройство выполняет аналого-цифровое преобразование двух аналоговых сигналов с одновременным вычислением 1щфрового кода их произведения 3ta rr тактов, т.е. позволяет повысить быстродействие в .n раз по сравнению с известным. При этом погрешность выпoлнeнияv аналого-цифрового преобразования сомножителей и вычисления их произведения определяется разрядностью используемых аналого-цифровых преобразователей и совпадает с погрешностью известного устройства. Указанные обстоятельства определяют технико-эконо1№ческий эффект возможного применения рассмотренного аналого-цифрового множительного устройства.

гз

$U9.Z

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для сигнализации положения механизма | 1981 |

|

SU995106A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-10-07—Публикация

1983-01-14—Подача