Изобретение относится к технике связи, а именно к задаче повторения узлов коммутации сообщений на сетях передачи дискретной информации в ин тегрированных АСУ промышленных пред приятий. Известны устройства коммутации сообщений, нашедшие широкое применение при решении задач передачи сообщений от источников информации к потребителю в информационно-вычислительных комплексах и системах передачи данных. Известно устройство адресного управления коммутацией сообщений, содержащее источники сообщений, вых ды которых связаны с входами узла предварительной коммутации и через элементы ИЛИ - с первыми входами у ла синтеза входных воздействий, выходы которых соединены с первыми входами блока управления, первый выход которого соединен со вторым входом.узла синтеза входных элементов И, вторые входы которых соедине ны с выходами узла предварительной коммутации, а выходы - с входами накопителей сообщений, первые выходы которых соединены с шинами направлений передач, а вторые - с входами блока селекции управляющих воздействий, выход которого соединен со вторым входом ,блока управления lj.i Наиболее близким по технической сущности к предложенному является многоканальный коммутатор, содержа)ций информационные блоки, выходы которых соединены с первыми входами буферного ком1.1утатора и первого элемента ИЛИ, блок управления, первые входы которого соединены с выходами дешифратора, первые входы которого соединены с выходом первого элемента ИЛИ, а второй вход - с первым выходом блока управления, вторые выходы которого соединены соответственно с первыми первых элементов И, вторые входы которых соединены с первыми выходами буферного коммутатора, а выходы - с первыми входами накопителей информации соответственно, адаптивный коммутатор, выход которого соединен с третьим входом блока управления, а вторые входы - со вторыми выходами накопителей информации, входы с первьами четвертые и пятые элементы И, второй и третий элементы ИЛИ, генератор, передающие блоки.

первые выходы которых соединены с направлениями передач, вторые выходы - со вторы 1и входами блока управления, первыми входами адаптивного KOMfiyxaTopa, входами второго элемента ИЛИ, вторыми входами вторых элементов И, вторыми входами пятых элементов И и первыми инверсивными входами третьих элементов И, выходы которых соединены с входами передающих блоков, а входы с первыми выходами Накопителей информации и первыми входами вторых элементов И, выходы которых соединены с входами третьего элемента ИЛИ, выход которого соединен с другим входом первого элемента ИЛИ и со вторым входом буферного коммутатора, второй выход которого соединен со вторым входом четвертого элемента И, первый вход которого соединен с выходом второго элемента ИЛИ а выход - с входом генератора, выход которого соединен с первыми входами пятых элементов И, выходы которых . соединены со вторыми входами накопителей информации соответственно.

Причем адаптивный коммутаторсодержит дешифраторы, блоки деления, регистры режимов, разделитель сигналов, блоки умножения, элементы И, причем первые входы блока соединены с входами дешифратора, выходы которых соединены с первыми входами соответствующих блоков деления, вторые входы которых соединены с выходами блоков умножения, а выходы с первыми входами разделителя сигналов, выход которого является выходом адаптивного коммутатора, а вы,ходы регистров режимов соединены соответственно с первыми входами элементов, И, вторые входы которых соединены со вторыми входами адаптивного коммутатора и вторыми входами разделителя сигналов, а выходы - с соответствующими входами блоков умно жения 2 .

Однако в известных устройствах если канал связи окажется в нерабочем состоянии вследствие высокого уровня помех либо отказа, то по сигналу аппаратуры передачи данных начинается перераспределение сообщений стоящих в очереди накопителя к данному отказавшему каналу. Причем информация поступает на вход коммутатора. Тоё. перераспределение прок опкт заново и на него тратится время, а также возникают затраты на очередные задержки времени в новых очередях. Это приводит к дополнительным затратам по времени доставки информации, срывам по доставке информации и требуемые .сроки.

Цель изобретения - повышение быстродействия многоканального коммутатора.

Указанная цель достигается тем, что в многоканальный коммутатор.

содержащий п источников информации, выходы которых соединены с соответствуЪщими п входами элемента ИЛИ, и буферного коммутатора, m выходов которого соединены с первыми входами соответствующих элементов И, выход элемента ИЛИ соединен с первым входом дешифратора, выходы, которого соединены с соответствующими первы/ми входами первого блока управления, первый выход которого соединен со вторым входом дешифратора,вторые выходы первого блока управления соединены со вторыми входами соответствующих элементов И, выходы которых соединены с входами соответствующих накопителей информации, первые выходы которых соединены с соответствующими первыми входами адаптивного кoм yтaтopa, выход которого соединен со вторым входом первого блока управления, и m передатчиков информации, первые выходы которых соединены с соответствующими вторыми входами адаптивного коммутатора и третьими входами первого.блока управления, вторые выходы m передатчиков соединены с соответствующими m выходами многоканального коммутатора, введены блок ключей, второй блок управления и дополнительные элементы ИЛИ, вторые и третьи выходы накопителей информации соединены с первыми входами второго блока управления и блока ключей соответственно, выходы блока ключей соединены с входами соответствующих m передатчиков, первые и третьи выходы которых соединены соответственно с первыми и вторыми входами соответствующих дополнительных элементов ИЛИ, выходы которых соединены со вторыми входами второго блока управления, выходы второго блока управления соединены с сйответствующими вторыми входами блока ключей.

Кроме того, второй блок управления содержит элемент контроля состояния канала, дешифратор адреса, элемент выбора приоритета, распределитель, переключатель, элементы И, ИЛИ и элемент задержки, первые входы элементов И соединены с первыми входами второго блока управления; выходы элементов И соединены с соответствующими входами дешифратора адреса и первыми входами переключателя, выход которого соединен с первым входом первого элемента ИЛИ, выход

которого соединен с входом распределителя, выходы распределителя соединены се вторыми входами соответствующих элементов И и вторыми входами переключателя, выходы дешифратора

0 адреса соединены с соответствующими первыми входс1ми элемента контроля состояния канала и входами второго элемента ИЛИ, выход которого через элемент задержки соединен со Ьто

5 рым входом первого Элемента ИЛИ,

вторые входы элемента контроля состояния канала соединены с вторыми входами второго блока управления, выходы элемента контроля состояния канала соединены с соответствующими входами элемента выбораприрритета, выходы которого соединены с выходами второго блока управления/

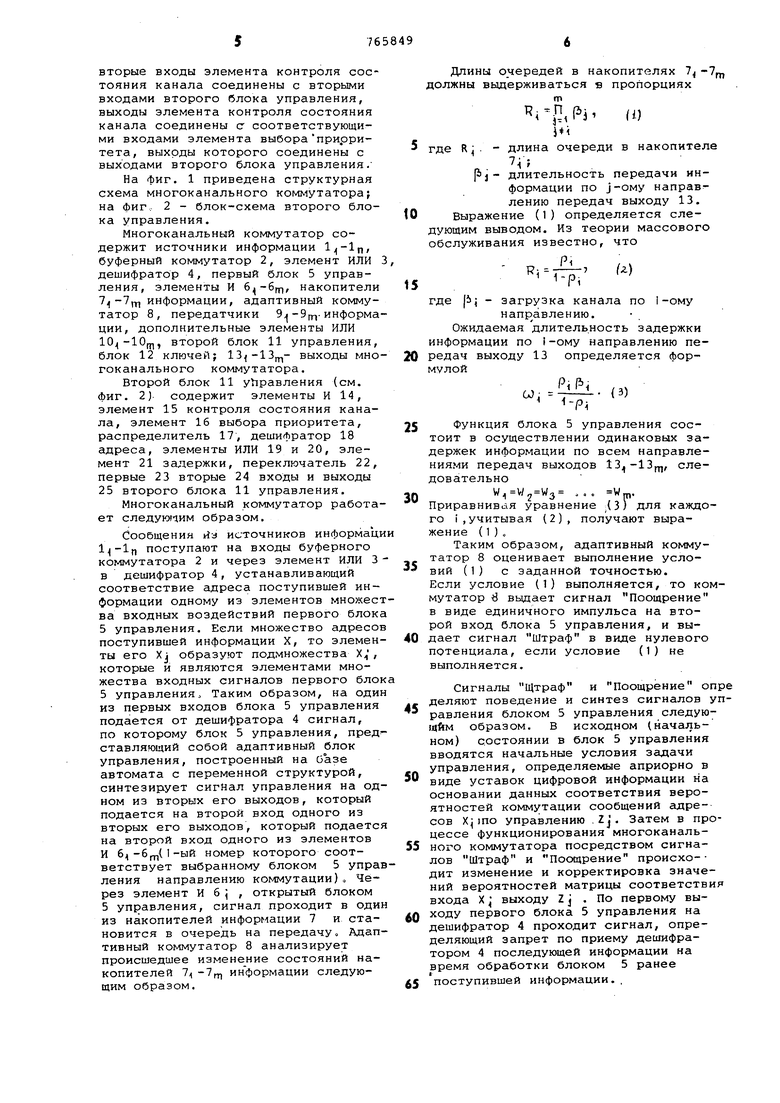

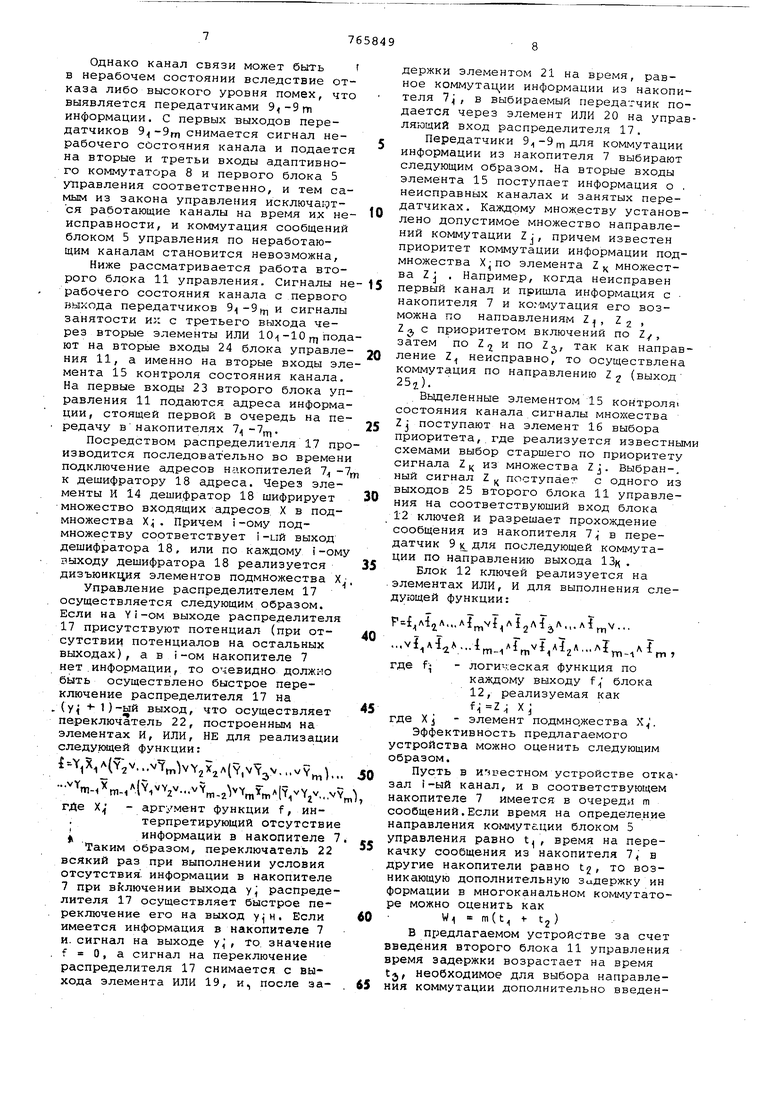

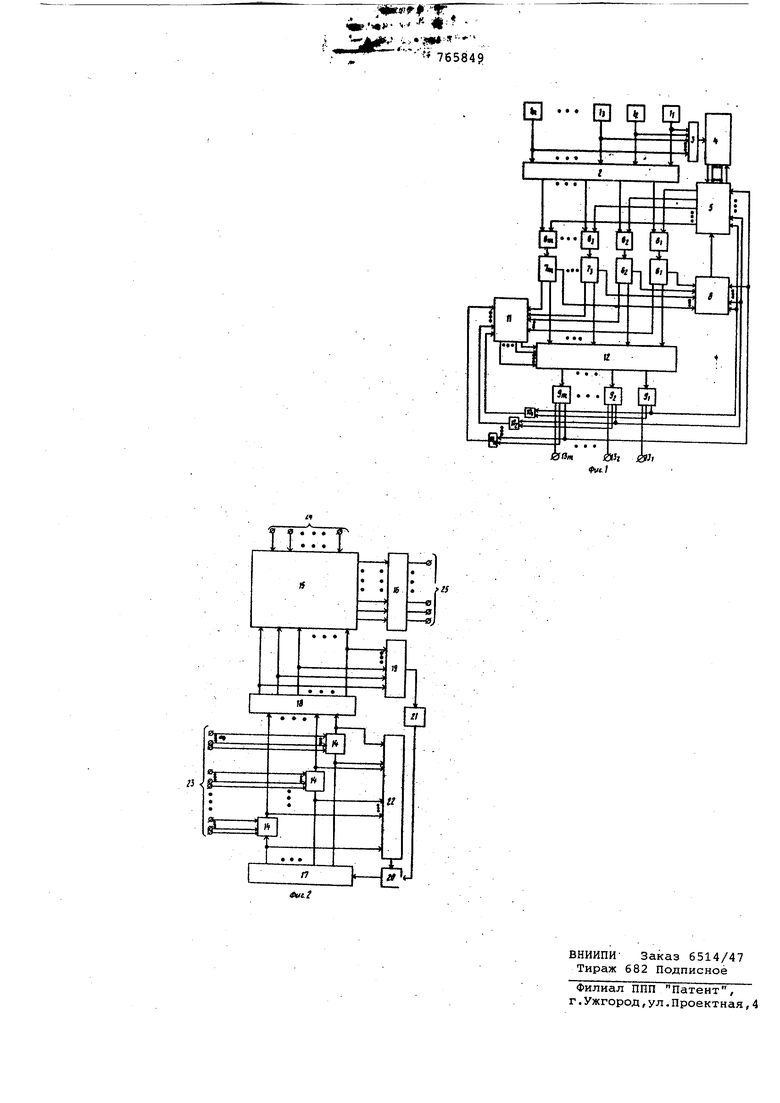

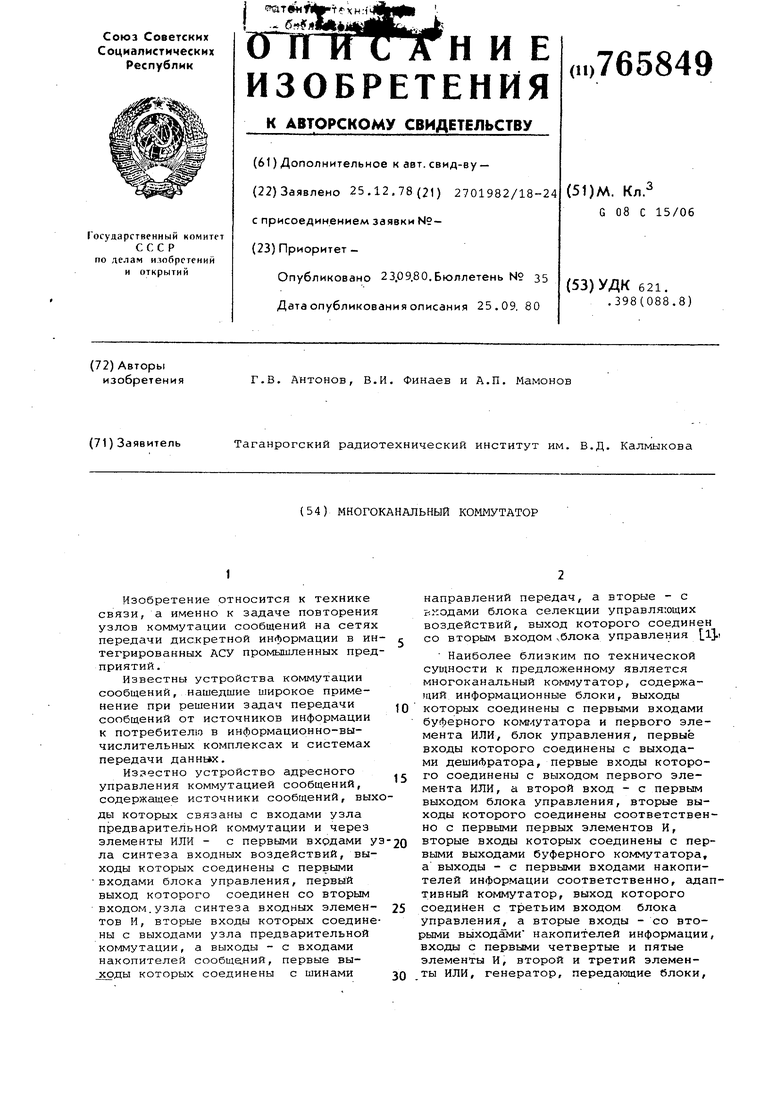

На фиг. 1 приведена структурная схема многоканального коммутатора; на фиг. 2 - блок-схема второго блока управления.

Многоканальный коммутатор содержит источники информации 1,-lp, буферный коммутатор 2, элемент ИЛИ дешифратор 4, первый блок 5 управления, элементы И , накопители информации, адаптивный коммутатор 8, передатчики . информации, дополнительные элементы ИЛИ , второй блок 11 управления, блок 12 ключей; выходы многоканального кок1мутатора.

Второй блок 11 управления (см. фиг. 2) содержит элементы И 14, элемент 15 контроля состояния канала, элемент 16 выбора приоритета, распределитель 17, дешифратор 18 адреса, элементы ИЛИ 19 и 20, элемент 21 задержки, переключатель 22, первые 23 вторые 24 входы и выходы 25 второго блока 11 управления.

Многоканальный коммутатор работает следую11им образом.

Сообщения tia источников информаци поступают на входы буферного коммутатора 2 и череэ элемент ИЛИ 3 в дешифратор 4, устанавливающий соответствие адреса поступившей информации одному иэ элементов множества входных воздействий первого блока 5 управления. Если множество адресов поступившей информации X, то элементы его Xj образуют подмножества , которые и являются элементами множества входных сигналов первого блок 5 управления Таким образом, на один из первых входов блока 5 управления подается от дешифратора 4 сигнал, по которому блок 5 управления, пред ставляющий собой адаптивный блок управления, построенный на базе автомата с переменной структурой, синтезирует сигнал управления на одном из вторых его выходов, который подается на второй вход одного из вторых его выходов, который подается на второй вход одного из элементов И (}-ыК номер которого соответствует выбранному блоком 5 управления направлению коммутации)« Через элемент И 6 j , открытый блоком 5 управления, сигнал проходит в один из накопителей информации 7 и становится в очередь на передачу. Адаптивный коммутатор 8 анализирует происшедшее изменение состояний накопителей 1ц -7ф информации следующим образом.

Длины о чередей в накопителях 7 должны выдерживаться s пропорциях

Г|,Р (i)

где R,. - длина очереди в накопителе „ 7 ;

PJ- длительность передачи информации по j-ому направо лению передач выходу 13. Выражение (1) определяется следующим выводом. Из теории массового обслуживания известно, что

Р1

()

1 1-р,

о. .

где ji, - загрузка канала по 1-ому

лению.

Ожидаемая длительность задержки информации по i-ому направлению пеРедач выходу 13 определяется формулой

(

Функция блока 5 управления состоит в осуществлении одинаковых задержек информации по всем направлениями передач выходов , следовательно

.. Wjn.

Приравнивая уравнение (З) для каждого i.учитывая (2), получают выражение ( 1 ) о

Таким образом, адаптивный коммутатор 8 оценивает выполнение услоВИЙ (1) с заданной точностью.

Если условие (1) выполняется, то коммутатор в выдает сигнал Поощрение в виде единичного импульса на второй вход блока 5 управления, и выдает сигнал Штраф в виде нулевого потенциала, если условие (1) не выполняется.

Сигналы Щтраф и Поощрение опре деляют поведение и синтез сигналов управления блоком 5 управления следующим образом. в исходном (начальном) состоянии в блок 5 управления вводятся начальные условия задачи

управления, определяемые априорно в

виде уставок цифровой информации на основании данных соответствия вероятностей коммутации сообщений адресов Xjino управлению . ZJ. Затем в процессе функционирования многоканального коммутатора посредством сигналов Штраф и Поощрение происхо- дит изменение и корректировка значений вероятностей матрицы соответствия входа X выходу Z j . По первому выходу первого блока 5 управления на дешифратор 4 проходит сигнал, определяющий запрет по приему дешифратором 4 последующей информации на время обработки блоком 5 ранее

поступившей информации.. Однако канал связи может быть в нерабочем состоянии вследствие отказа либо высокого уровня помех, что выявляется передатчиками информации. С первых выходов передатчиков снимается сигнал нерабочего состояния канала и подается на вторые и третьи входы адаптивного коммутатора 8 и первого блока 5 управления соответственно, и тем самым из закона управления исключа1-ртся работающие каналы на время их не исправности, и коммутация сообщений блоком 5 управления по неработающим каналам становится невозможна, Ниже рассматривается работа второго блока 11 управления. Сигналы н рабочего состояния канала с первого выхода передатчиков , и сигналы занятости их с третьего выхода через вторые элементы ИЛИ под ют на вторые входы 24 блока управле ния 11, а именно на вторые входы эл мента 15 контроля состояния канала. На первые входы 23 второго блока уп равления 11 подаются адреса информа ции, стоящей первой в очередь на пе редачу внакопителях . Посредством распределителя 17 пр изводится последовательно во времен подключение адресов накопителей 1 к дешифратору 18 адреса. Через элементы И 14 дешифратор 18 шифрирует множество входящих адресов X в подмножества Х. Причем i-ому подмножеству соответствует i-ий выход дешифратора 18, или по каждому i-ом выходу дешифратора 18 реализуется дизъюнкция элементов подмножества Х Управление распределителем 17 осуществляется следующим образом. Если на Y i-ом выходе распределителя 17 присутствуют потенциал (при отсутствии потенциалов на остальных выходах), а в i-ом накопителе 7 нет ,информации, то очевидно должно быть осуществлено быстрое переключение распределителя 17 на .{yj )-ый выход, что осуществляет переключатель 22, построенным на элементах И, ИЛИ, НЕ для реализации следующей функции: bY,(Y2V...V VY2X2A(Y,VV,jV.,.vY.. --V.m-/(YiVY,v...vY,.(,,v гДе - аргумент функции f, интерпретирующий отсутствие I информации в накопителе 7 Таким образом, переключатель 22 всякий раз при выполнении условия отсутствия информации в накопителе 7 при включении выхода у распределителя 17 осуществляет быстрое пе. реключение его на выход . Если имеется информация в накопителе 7 и. сигнал на выходе , то значение . f О, а сигнал на переключение распределителя 17 снимается с выхода элемента ИЛИ 19, и, после задержки элементом 21 на время, равное коммутации информации из накопителя 7, в выбираемый передатчик подается через элемент ИЛИ 20 на управляющий вход распределителя 17, Передатчики 9 -9рпДля коммутации информации из накопителя 7 выбирают следующим образом. На вторые входы элемента 15 поступает информация о , неисправных каналах и занятых передатчиках. Каждому множеству установлено допустимое множество направлений коммутации Zj, причем известен приоритет коммутации информации подмножества элемента Z множества Z j . Например, когда неисправен первый канал и пришла информация с накопителя 7 и ко.чмутация его возможна по напоавлениям Z|, Z2 Z 2, с приоритетом включений по Z/, затем по Z2 и по Z, так как направление Z неисправно, то осуществлена коммутация по направлению Z,, (выход 25i). Выделенные элементом 15 контроля) состояния канала сигналы множества Zj поступают на элемент 16 выбора приоритета,.где реализуется известными схемами выбор старшего по приоритету сигнала Z из множества Zj. Выбран-, ный сигнал Z 1 поступает с одного из выходов 25 второго блока 11 управления на соответствующий вход блока 12 ключей и разрешает прохождение сообщения из накопителя 7 в передатчик 9 к для последующей коммутации по направлению выхода 13 . Блок 12 ключей реализуется на элементах ИЛИ, И для выполнения следующей функции: ,AijA...Af vI Ai2AT3A.,..,. .--im-i fm v z - mM fm где f - логическая функция по каждому выходу блока 12, реализуемая как i где Xj - элемент подмно.жества . Эффективность предлагаемого устройства можно оценить следующим образом. Пусть в ичвестном устройстве отказал i-ый канал, и в соответствующем накопителе 7 имеется в очереди m сообщений.Если время на определение направления коммутации блоком 5 управления равно t, время на перекачку сообщения из накопителя 7, в другие накопители равно t, то возникающую дополнительную задержку ин формации в многоканальном коммутаторе можно оценить как Wi m(t t t2) В предлагаемом устройстве за счет введения второго блока 11 управления время задержки возрастает на время tj, необходимое для выбора направления коммутации дополнительно введенным блоком 11, но за счет исключен времени, tj/ соизмеримости времени t и tj эффективность и быстродейс вие предлагаемого устройства резко возрастает и в количественном отно шении определится формулой л 7 где - частотность возникновени нерабочего состояния; m - среднее число перераспре деляемой информации при возникновении нерабочего состояния канала. Формула изобретения 1. Многоканальный коммутатор, с держащий п источников информации, выходы которых соединены с соответствующими п-входами элемента ИЛ и буферного коммутатора, m выходов буферного коммутатора соединены с первыми входами соответствующих элементов И, выход элемента ИЛИ сое динен с первым входом дешифратора, которого соединены с соотве ствующими первыми входами первого блока управления, первый выход которого соединен со вторым входом дешифратора, вторые выходы первого блока управления соединены со вторы ми входами соответствующих элементо И, выходы которых соединены с входа ми соответствующих накопителей информации, первые выходы которых сое динены с соответствующими первыми в дами адаптивного коммутатора, выход которого соединен со вторым входом -первого блока управления и m переда чиков информации, первые выходы кот рых соединены с соответствующими вторыми входами адаптивного коммутатора, и третьими входами первого блока управления, вторые выходы m передатчиков соединены с соответств кицими m выходами многоканального коммутатора, отличающийс я тем, что, с целью повышения быстродействиямногоканального коммутатора, в него введены блок ключей, второй блок управления и дополнительные элементы ИЛИ, вторые и третьи выходы накопителей информации соединены с первыми входами второго блока управления и блока ключей соответственно, выходы блока ключей соединены с входами соответствующих m передатчиков, первый и третьи выходы которых соединены соответственно с первыми и вторыми входами соответствующих дополнительных элементов ИЛИ, выходы которых соединены со вторыми входами второго блока управления, выходы второго блока управления соединены с соответствующими вторами входами блока ключей. 2 .Коммутатор по п. 1, отличающийся тем, что второй блок управления содержит элемент контроля состояния канала, дешифратор адреса, элемент выбора приоритета, распределитель, переключатель, элементы И, ИЛИ и элемент задержки, первые входы элементов И соединены с первыми входами второго блока управления, выходы элементов И соединены с соответствующими входами дешифратора адреса и первыми входами переключателя, выход которого соединен с первым входом первого элемента ИЛИ, выход которого соединен с входом распределителя, выходы распределителя соединены со вторыми входами соответствующих элементов И и вторыми входами переключателя, выходы дешифрато-. ра адреса соединены ссоответствующими первыми входами элемента контроля состояния канала и входами второго элемента ИЛИ, выход которого через элемент задержки соединен со вторым входом первого элемента ИЛИ, вторые входы элемента контроля состояния канала соединены со вторыми входами второго блока управления, выходы элемента контроля состояния канала соединены с соответствующими входами элемента выбора приоритета, выходы которого соединены с выходс1ми второго блока управления. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР по заявке 2476766/18-24, кл. 6 08 С 15/06, 1977. 2.Авторское свидетельство СССР по заявке 2636157/18-24, кл. G 08 С 15/06, 1978 (прототип)

i .. .

r. H- 76584

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный матричный коммутатор | 1981 |

|

SU964690A1 |

| СЕТЬ ДЛЯ МАРШРУТИЗАЦИИ СООБЩЕНИЙ | 1996 |

|

RU2115162C1 |

| Многоканальный коммутатор | 1981 |

|

SU963046A1 |

| Адаптивная телеметрическая система | 1979 |

|

SU783825A1 |

| Многоканальное устройство для управления коммутацией сообщений | 1981 |

|

SU1012304A1 |

| Многоканальная система передачи двоичной информации с временным уплотнением | 1982 |

|

SU1075429A1 |

| Многоканальное устройство для сопряжения источников сообщений с цифровой вычислительной машиной | 1980 |

|

SU920693A1 |

| СТАНЦИЯ СВЯЗИ С АДАПТИВНОЙ КОММУТАЦИЕЙ КАНАЛОВ | 2015 |

|

RU2594758C1 |

| Телеизмерительная система | 1979 |

|

SU834735A1 |

| Распределенная система для программного управления технологическими процессами | 1990 |

|

SU1797096A1 |

r i j. I

0Яд 0ai 0}i

/«.

r

Авторы

Даты

1980-09-23—Публикация

1978-12-25—Подача