(54) МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ИСТОЧНИКОВ СООБЩЕНИЙ С ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНОЙ

1

Изобретение относится к вычислительной технике, в частности к устройствам для сопряжения, а также может быть использовано в системах управления и передачи информации.

Известно многоканальное устройство для сопряжения источников случайных потоков сообщений с цифровой вычислительной машиной. Известное устройство сопряжения производит упорядочение сообщений, поступающих последовательно в случайные моменты времени, при этом организуется очередь, в которой сообщения расположены в порядке поступления 1 .

Однако в устройстве сопряжения не предусмотрена возможность нения порядка расположения сробще-, НИИ в очереди в зависимости от важности информации, содержащейся в сообщении.

Наиболее близким к изобретению по технической сущности и достигаемому результату является многокаМАШИНОЙ

нальное устройство для сопряжения источников сообщений с цифровой вычислительной машиной, содержащее блок формирования адреса, блок памяти, блок управления коммутацией, блок формирования кода приоритета, блок управления, блок формирования номера позиции очереди, каналы, каждьпЧ из которых содержит регистр признака канала, регистр приоритета,

to регистр номера позиции очереди канала, группу коммутаторов канала, соединенных между собой определенным образом 2 .

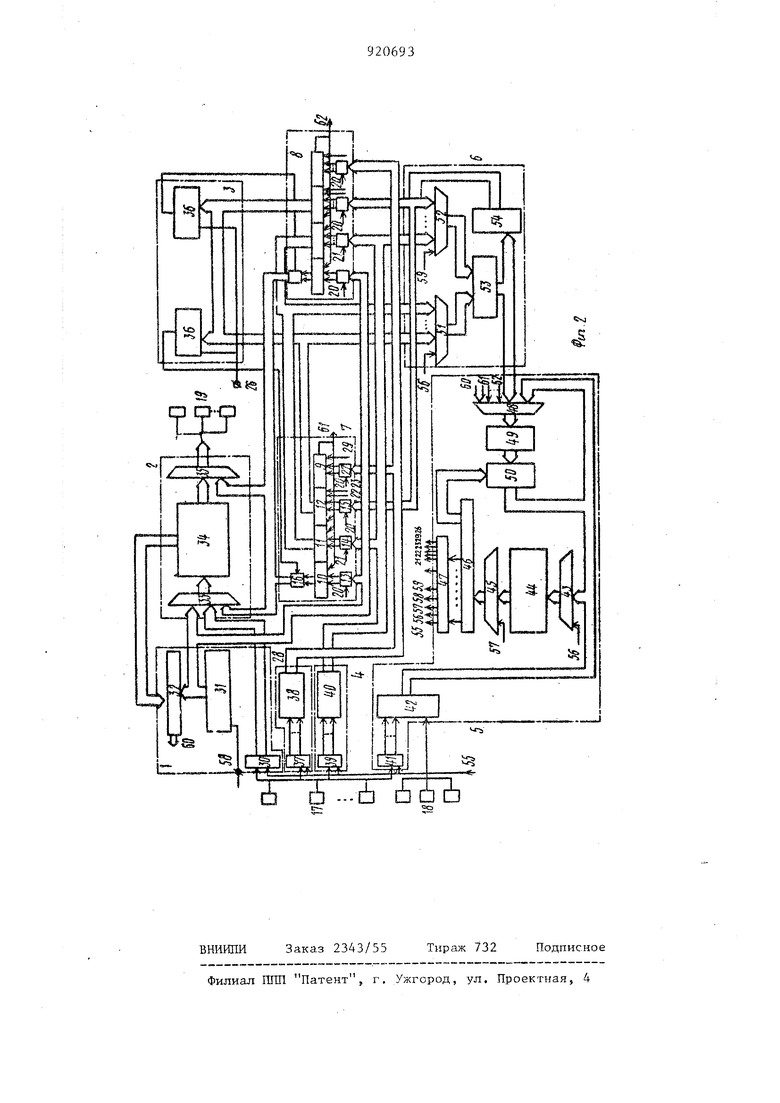

Однако ук-азанное устройство соISпряжения имеет ограниченные функциональные возможности. Время ожидания начала обслуживания единственно зависит от приоритета поступающего сообщения и текущего сос2Qтояния очереди. В этих условиях при ограниченной длине очереди (объеме буферной памяти) отказ в обслуживании получают вновь поступающие заявки низких приоритетов без учета времени пребывания в очереди заявок высших приоритетов. При изменении параметров входного потока, а именно, при наличии преобладающего характера сообщений определенного приоритета, другие сообщения более низкого приоритета, а также вновь поступающие заявки этого же приоритета к обслуживанию не до-пус- каются, так как буферная память заполнена, В условиях резкого возрастания нагрузки (например,- увеличилась интенсивность входного потока) система переходит к обслуживанию заявок с наибольшим приоритетом в порядке их поступления, не принимая во внимание ограничений на допустимое время ожидания с учетом изменившейся интенсивности поступления заявок. Перечисленные недостатки ведут к тому, что ухудшаются качественные показатели функционирования устройства при широком изменении параметров входного потока,.так как среднее время ожидания обслуживания уве ли швается. Целью изобретения является повышение пропускной способности устрой ства при широком диапазоне изменени параметров входного потока сообщений . Поставленная цель достигается те что в многоканальное устройство для сопряжения источников .сообщений с цифровой вычислительноймашиной, со держащее блок формирования адреса, первый вход которого является первым входом устройства и соединен с первыми входами блока памяти, блока управления и с входом блока форми: р.ования кода приоритета, блок форми рования номера позиции очереди, выход которого соединен со вторым вх дом- блока управления, блок управле ния коммутацией, а в каждом кангше регистр признака канала, вход и вы ход которого соединены соответстве но с выходом первого и кодовым вхо дом второго коммутатора канала, ре гистр номера позиции очереди канала, первый вход которого соединен выходом третьего коммутатора канала, регистр приоритета канала, вхо которого соединен с выходом четвер того коммутатора, причем первый и второй выходы блока памяти соедине ны соответственно со вторым входом блока формирования адреса и выходом устройства, второй вход которого соединен с третьим входом блока управления, первьй выход блока управления coeдинe i со входом блока управления коммутацией, группа выходов которого соединена с первыми управляклцими входами вторьпс коммутаторов соответствующих каналов, выходы вторых коммутаторов каналов соединены с соответствующими входами первой группы входов блока памяти, выход блока формирования адреса соединен со вторым входом блока памяти и с кодовыми входами первых коммутаторов каналов, выход регистра номера позиции очере/ди канала соединен с соответствующим входом группы входов блока управления коммутацией и ссоответствующим входом первой группы входов блока формированич номера позиции очереди, выходы первой группы выходов блока управления соединены с управляющими входами первых и четвертых коммутаторов каналов, выходы второй группы выходов блока управлеьшя соединены с управляющими входами третьих коммутатотов каналов, выходы третьей группы выходов блока управлегшя соединены со вторыми входами регистров номера позиции очереди каналов, выходы четвертой группы выходов блока управления соединены с третьими входами регистров номера позиции очереди каналов, кодовые входы третьих кoм Jyтaтopoв каналов соединены с выходом блока фop иpoвaния номера позиции очереди, выход блока формирования кода приоритета соединен с кодовыми входами четвертых коммутаторов каналов, а выходы регистров приоритета каналов соединены со входами второй группы входов блока формирования номера позиции очереди, введен блок формирования кода времени допустимого ожидания начала обслуживаьшя, а в каждом канале - регистр допустимого времени ожидания и пятый коммутатор, причем вход и выход блока формирования кода времени допустимого ожидания начала обслуживания соединены соответственно с входом устройства и с кодовыми входами пятых коммутаторов каналов, управляющие входы пятых коммутаторов каналов соединены с выходами первой группь выходов блока упраш1ерп1Я, а выходы с-первыми входами регистров допусч :Мого времени ожидания, вторые вхо ды которых связаны со вторым выходом блока управления, а выходы регистров допустимого времени ожидания соединены с уста новочными входами регистров при нака, канала, регистров номера позиции канала и регистров приоритета одноименных каналов, с устано вочными входами блока памяти и с вторыми управляющими входами вторы коммутаторов соответствующего кана ла. Кроме того, блок формирования кода допустимого времени ожидания выполнен в виде регистра и шифратора, а вход блока соединен со вхо дом регистра, выход которого через шифратор соединен с выходом блока. На фиг. 1 представлена структур ная схема устройства, на фиг. 2 . один из конкретных вариантов ее выполне шя. Устройство содержит (фиг. 1) бло формирования адреса 1, блок памяти 2, блок управления коммутацией 3, блок формирования кода приоритета 4, блок управления 5, блок формирования номера позиции очереди 6, каналы 7 и 8, регистр допустимого времени ожидания 9, регистр признака канала 10, регистр приоритета 1I,регистр номера позиции очереди 12,первый 13, четвертый 14, третий 15, второй 16 коммутаторы канала, первый вход устройства 17, второй вход устройства 18, выход 19 многоканального устройства для сопряжения источников сообщений с ЦВМ первая группа выходов 20, вторая группа выходов 2, третья группа выходов 22, четвертая группа выходов 23 блока управления 5, первая группа входов 24, вторая группа вхо дов 25 блока формирования номера по зиции очереди 6, первый выход 26 бл ка управления 5, пятый коммутатор 2 канала, блок 28 формирования кода вр мени допустимого ожидания начала обслуживания, второй выход 29 блока управления. Блок формирования адреса 1 содержит (фиг. 2) регистр 30, распределитель импульсов 31, мультиплексоры 32. Блок памяти 2 содержит мультиплексор 33, запоминающее устройство 34, мультиплексор 35, селекторы 36, регистр 37, шифратор 38, регистр 39, шифратор 40,регистр 6936 41, шифратор 42, мультиплексор 43, запоминающее устройство (ПЗУ) 44, мультиплекстор 45, регистр операции 46., дешифратор 47, мультиплексор 48, регистр условий 49, дешифратор условий 50, мультиплексоры 51 52, сумматор 53, регистр 54, выходы 55-59 блока управления входы 60-62 блока управления, являющиеся также соответственно выходом блока формирования адреса и выходами каналов устройства. Блок формирования адреса I содержит входной регис -р 30, распределитель 31, мультиплексор 32. Блок памяти 2 содержит входной мультиплексор 33, запоминающее устройство 34, выходной мультиплексор 35. Блок управления коммутацией 3 состоит из совокупности селекторов36, число которых равно количеству каналов устройства. Блок формирования кода приоритета 4 содержит регистр 39 и шифратор 40. Блок управления 5 представляет собой управляющий автомат с жесткой логикой и содержит-шифратор адреса программы 42, мультиплексор 43, запоминающее устройство 44, мультиплексор 45, регистр операций 46, дешифратор операций 47, мультиплексор 48, регистр условие 49, дешифратор условий 50. Блок формирования номера позиции очереди б содержит мультиплексоры 51 и 52, сумматор 53, регистр-накопитель-54. Блок формирования кода времени допустимого ожидания начала обслуживания 28 содержит регистр 37 и шифратор 38. На управляющее входы регистров 30, 37, 39 и 41 от дешифратора операций 47 подается сигнал 55. Запись в регистры 46, 49 и 54 осуи ествлена парафазным кодом. Мультиплексор 32 имеет группу выходных шин 60, информация по которой поступает на вход мультиплексора 48, Мультиплексоры 43, 45, 51 и 52 управляются сигналами 56-59 с дешифратора операций 47. По группе входов от регистра условий 49 на дешифратор условий 50 поступает внешняя информация, а с регистра операции 46 - внутренняя информация. В ячейках ОЗУ 34 хранятся поступающие сообщения. Ад рее задается состоянием выходов распредепителя 31, связанных с первой группой входов мультиплексора 33. Непосредственно сообщение поступает на вторую группу входов мультиплексора 33 от регистра 30. На третью группу входов гульти1шексора 33 поступает адрес сообщений, время обслу живания которых истекло. В ПЗУ 44 хранятся коды микрокома а формирование кода микрокоманды за дается состоянием выходных информационных шин дешифратора условий 50. Формирование кода начальной микрокоманды микропрограм-ы соответствующего режима работы устройства сопряжения задается состоянием шин (шифратора адреса программы 42. Изменение состояния распределителя 31 осуществляется по приходу внешних сигналов на входные шины 17 (изменение состоя ния происходит всякий раз по приходу очередного сообщения). Каждый из селекторов 36 настраивается на определенное состояние регистра 12 в составе группы регистров 9, 10, П и 2, обеспечивающего перемещение заявки в очереди в соответствии с временем прихода и приоритетом. Связь с выхода дешифратора условий 50 на вход мультиплексора 48 необходима для проверки внешних логических условий с целью ветвления по микропрограмме. Появление сигналов на входах 61 и 62 означает окончани допустимого времени ожидания начала обслуживания конкретной заявки Появление одного из этих сигналов долж но повлечь за с.обой стирание соответствующих ячеек в ОЗУ 34, Вход 18 пр назначен дпя передачи информации от ЦВМ к устройству сопряжения. Выходы 20-23, 26 и 29 соединены с в ходами дешифратора операций 47. Устройство работает в трех режимах. Первый - реализуется при приходе сообщения на вход 17 от источника и имеет целью постановку пришедшего сообщения на место в очереди Е соот вех.ствии с состоянием очереди в момент прихода и важности информации, содержащейся в сообщении. Состояние .очереди определяется числом сообщений, стоящих в очереди, и кодами пр оритетов важностью) этих сообщений Код состояния очереди снимается с в хода блока 6. Второй - реализуется при пс стугшении на вход 18 служебногосигнал вызова сообщения, стоящего на перво месте очереди. Третий - реализуется при истечении времени допустимого ожидания на чала обстгуживания у одного из сообщений, хранящегося в блоке памяти 2 и занимающего один из каналов 7 и В. Это сообщение исключается из очереи, и блок формирования номера позиции очереди 6 определяет новое состояние очереди, зависящее от числа оставшихся сообщени и их важности. В первом режиме устройство функционирует следующим образом. Блок 1 вырабатывает адрес свободной ячейки блока памяти 2. По этому адресу код сообщения записывается в блок памяти 2 и хранится там все время пребывания в очереди. Одновременно с этим блок 4 вырабатывает код приоритета, а блок 28 формирует код времени допустимого ожидания начала обслуживания. Поступившее сообщение воздействует также на блок управления 5, В соответствии с сигналом, приходящим из блока 6, блок управления 5 вырабатывает: на выходах 20 - сигналы управления, которые производят запись кода адреса, кода приоритета и кода времени допустимого ожидания начала обслуживания пришедшего сообщения в свободные регистры 10, 11 и 9 каналов 7 и 8. на выходах 21 - сигналы управления, которые осуществляют запись номера позиции очереди в соответствующий регистр 12 каналов 7 и 8j на выходах 23 - сигналы управления, которые уменьшают на единицу номера позиций очереди сообщений, приоритет которых меньше приоритета пришедшего сообщенияj на выходе 29 - управляющей сигнал, который уменьшает на единицу код времени допустимого ожидания начала обслуживания, храня1цийся в регистрах 9 всех каналов 7 и 8, На этом постановка сообщегдая в очередь заканчивается. Функционирование устройства во втором режиме начинается по приходу на вход 18 сигнала от ЦВМ, который воздействует на блок управления 5, При этом блок управления 5 вырабатывает последовательно: на выходе 26 - сигнал управления, воздействующий на блок 3, на одном из выходов которого, в свою очередь, появляется сигнал управления, если состоя1ше соответствующего регистра 12 в каналах 7 и 8 соответствует первой позиции очереди. Этот сигнал поступает на соответствующие коммутаторы 16 каналов 7 и 8, При этом адр сообщения, стоящего на первой позиции очереди, поступает в блок; памяти 2. По этому адресу из блока памя ти 2 на выход 19 выдается код сообщения J на выходах 22 - управляющие сигналы, которые увеличивают номера позиций очереди в занятых регистрах 12 каналов 7 и 8 на единицу. Такое изменение номеров позиций очереди означает продвижение очереди. Один из этих сигналов переводит соответствующий регистр 12 в одном из каналов 7 и 8 в незанятое состояние. На этом режим вызова сообщения, сто ящего на первом месте очереди, в ЦВ оканчивается. Работа устройства в третьем режиме 2о АИ, начинается в тот момент, когда поя ляется сигнал на выходе регистра 9 каналов 7 и 8, что соответствует окончанию времени допустимого ожида ния начала обслуживания определенным сообщением. В момент прихода каждого сообщения на первый вход ус ройства 17 на выходе 29 блока управ ления 5 появляется сигнал, уменьшающий на единицу состояние регистров 9 всех каналов. В момент равенства нулю состояния регистра 9 одного из каналов 7 и 8, сигнал с выхода этого регистра производит установку в О регистров 10, 11 и 12 одноименного канала. Кроме этого срабатывает второй коммутатор 16. При этом по адресу сообщения, поступающего в блок памяти 2, происходит сброс соответствующей ячейки памяти в ноль. Как видно изменение интенсивност входного потока сообщений приводит и к изменению времени допустимого ожидания начала обслуживания, так ка код регистра 9 списьшается поступающими сообщениями,Таким образом, величина времени допустимого ожидания корректируется с учетом интенсивности входного потока. Причем-, чем вьше интенсивность входного потока, тем меньше среднее время допустимого ожидания начала обслуживания. Отсюда повьшается пропускная способность многоканального устройства для сопряжения сообщений с ЦВМ Таким образом, изобретейие позво ляет повысить пропускную способность устройства при широком диапа93 10 зоне изменения параметров входного потока сообщершй путем варьирования времени допустимого ожидания обслуживания с учетом изменяющихся параметров входного потока. Фломула изобретения 1. Многоканальное устройство для сопряжения и точников сообщений с 1дафровой вычислительной машиной, содержащее блок формирования адреса, первый вход которого является первым входом устройства и соединен с первыми входами блока памяти, блока управлеьшя и со входом блока формирования кода приоритета, блок формирования номера позиции очеревыход которого соединен со вторым входом блока управления, блок управления коммутацией, а в каждом канале - регистр призака канала, вход и выход которого соединены соответственно с выходом первого и кодовым входом второго коммутатора канала, регистр номера позиции очередиканала, первый вход которого соединен с выходом третьего коммутатора канала, регистр приоритета канала, вход которого соединен с выходом четвертого коммутатора, причем первый и второй выходы блока памяти соединены соответственно со вторым входом блока формирования адреса и выходом устройства, второй вход которого соединен с третьим входом блока управления, первый выход блока управления соединен с входом блока управления коммутацией, группа выходов которого соединена с первыми управлякх1щми входами вторых коммутаторов соответствующих каналов, выходы вторых коммутаторов каналов соединены с соответствую цнми входами первой группы входов блока памяти, выход блока формирования адреса соединен со вторым входом блока памяти и с кодовыми входами первых коммутаторов каналов, выход регистра номера позиции очереди канала соединен с соответствующим входом группы входов блока управления коммутацией и с соответствующим входом первой группы входов блока формирования номера позиции очереди, выходы первой группы выходов блока управления соединены с управляющими входами первых и четвертых коммутаторов.

каналов, выходы второй группы -выходов блока управления соединены с управляющими входами третьих коммутаторов каналов, выходы третьей группы выходов блока управления сое динены со вторыми входами регистров номера позиции очереди каналов, выходы четвертой группы выходов блока управления соединены с третьими входами регистров номера позиции очереди каналов, кодовые входы третьих коммутаторов каналов соединены с выходом блока i формирования номера позиции очереди, выход блока форьмрования кода приоритета соединен с кодо выми входами четвертых коммутаторов каналов, а выходы регистров приоритета каналов соединены со входами второй группы входов блока формирования номера позиции очереди, отличающееся тем, что, с целью повышения пропускной способности устройства при широком диапазоне изменения параметров входного потока сообщений, оно содержит блок фор - рования кода времени допустимого ожидания начала обслуживания, а в каждом канапе -.регистр допустимого времени ожидания и пятый коммутатор, причем вход и выход блока формирования кода времени допустимого ожидания начала обслужива1шя соединены соответственно с первым входом устройства и с кодовыми входами пятых коммутаторов каналов, управляющие входы пятых коммутаторов каналов соединены

с выходами первой группы выходов блока управления, а выходы - с первыми входами регистров допустимого времени ожидания, вторые входы которых связаны со вторым выходом блока управления, а выходы регистров допу- . .стимого времени ожидания соединены с установочными входами регистров признака канала, регистров номера позиции канала и регистров, приоритета

одноименных каналов, с установочными входами блока памяти и с вторыми управляющими входами вторых коммутаторов соответствующего канада. 2. Устройство по п. 1, о т л и чающееся тем, что, блок формирования кода допустимого времени ожидания выполнен в виде регистра и шифратора, а вход блока соединен со входом регистра, выход которого через шифратор соединен с выходом блока.

Источники информагдаи, принятые во внимание при экспертизе 1. Авторское свидетельство СССР

№ 489100, кл. G 06 F 3/00, 1975,

2. Авторское свидетельство СССР № 643861, кл, G 06 г 3/00, 1979.

I-

П

С

o

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство для моделирования систем массового обслуживания | 1984 |

|

SU1229771A1 |

| Устройство управления | 1989 |

|

SU1654820A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Многоканальное устройство для сопряжения источников сообщений с цифровой вычислительной машиной | 1976 |

|

SU643862A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1985 |

|

SU1278866A1 |

| Устройство для сопряжения эвм с абонентами | 1984 |

|

SU1215114A1 |

| Устройство для сопряжения каналовВВОдА-ВыВОдА C уСТРОйСТВОМ упРАВлЕНияОпЕРАТиВНОй пАМяТью МНОгОпРОцЕССОР-НОй ВычиСлиТЕльНОй МАшиНы | 1979 |

|

SU822168A1 |

| Устройство для обслуживания запросов | 1977 |

|

SU737953A1 |

Авторы

Даты

1982-04-15—Публикация

1980-04-30—Подача