1

Изобретение относится к измерительной информационной технике и может быть использовано в многоканальных системах передачи информации..5

Известно устройство для передачи информации, содержащее блок отбора Информации, соединенный с выходом адаптивного дискретизатора, блок времени и анализатор частоты отсче- 10 тов информации, входы которого соединены с выходами адаптивного дискретизатора и блока времени, а выходы подключены к входам блока уставок адаптивного дискретизатора и выходно- 5 го блока l .

Недостатком устройства является то, что частота поступления существенных отсчетов в канал связи оста%тся переменной, а для наиболее 20 эффективного использования каналов связи необходим равномерный поток информации.

Наиболее близким по технической сущности к предлагаемому является: 25 устройство для передачи информации, содержащее коммутатор, ключи, блок памяти, блок сравнения, канал связи и буферный накопитель, состоящий из блока управления записью, блока уп- 30

равления считыванием и блока памяти, выход коммутатора соединен, с первым входом блока сравнения и через ключи - с входом блока памяти и с первым входом блока памяти буферного накопителя, выход блока памяти подключен ко второму входу блока сравнения, выход которого соединен с управляющими выходами ключей , первые выходы блока управления .записью и блока управления считыванием подключены соответственно ко второму и к третьему входам блока памяти буферного накопителя, выход которого соединен с каналом связи ,

Недостатком этого устройства является то, что при различной активности входной информации .возможна как потеря информации при переполнении буфера, так и отсутствие информации для передачи в канал связи при оцустошении буфера. Это приводит к неравномерности потока существенной информации в канал связи и, следовательно, снижает надежность устройства.

Цель изобретения - повышение надежности устройства.

Эта цель достигается тем, что в устройство для передачи информации.

содержащее коммутатор, ключи, блок памяти, блок сравнения, канал связи и буферный накопитель, состоящий из блока управления записью, блока управления считыванием и блока памяти, выход коммутатора соединен с первым входом блока сравнения и через ключи - с входом блока памяти и с первым входом блока памяти буферного накопителя, выход блока памяти подключен ко второму входу блока сравнения, выход которого соединен с управляющими выходами ключей, первые выходы блока управления записью и блока управления считыванием подключены соответственно ко второму и к третьему входам блока памяти буферного накопителя, выход которого соединен с каналом связи, введены блок вычитания, формирователь допусков, триггер и формирователь кода, вторые выходы блока управления записью и блока управления считыванием буферного накопителя подключены соответственно к первым и вторым входам «лока вычитания и триггера, выход которого соединен с третьим входом блока вычитания, выходы которого через формирователь допусков и через формирователь кода соответственно подключены к третьему входу блока сравнения и к четвертому входу блока памяти буферного накопителя.

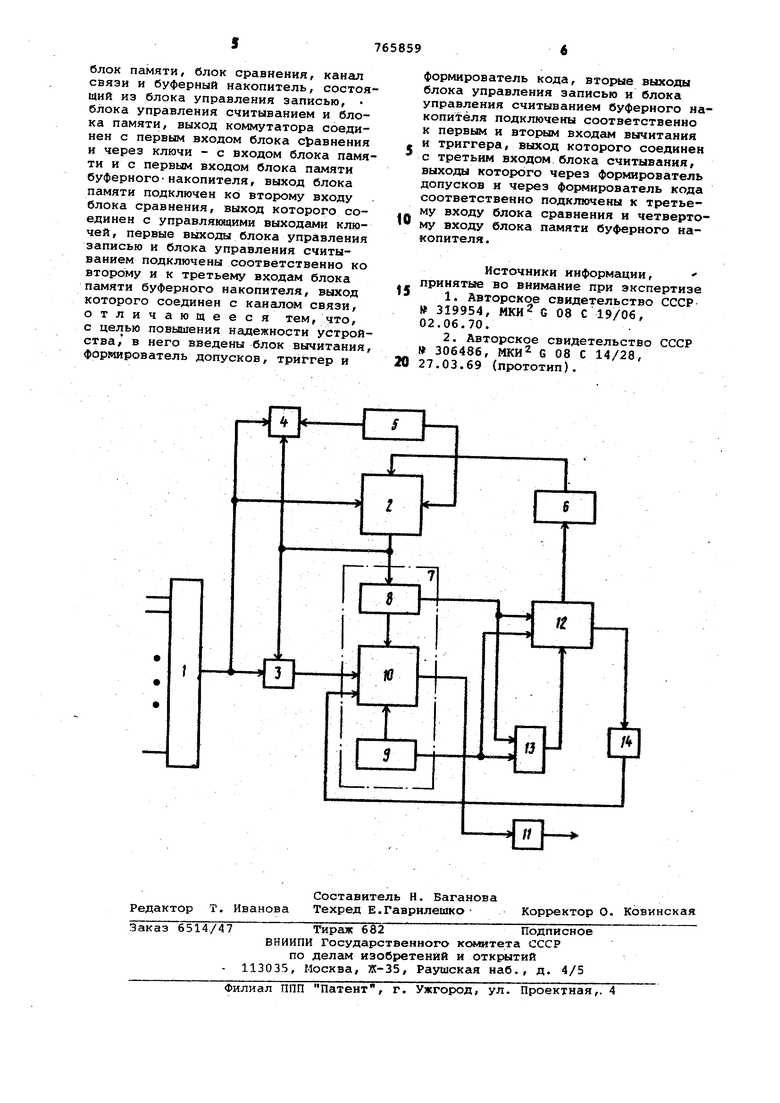

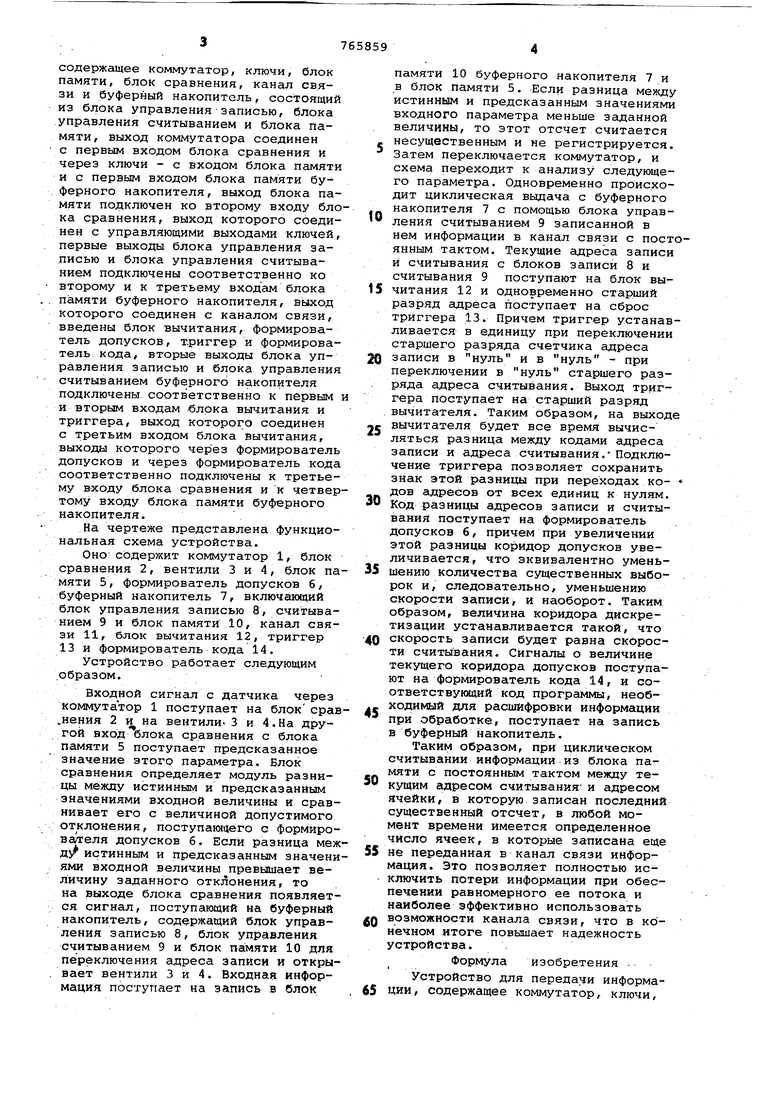

На чертеже представлена функциональная схема устройства.

Оно содержит коммутатор 1, блок сравнения 2, вентили 3 и 4, блок памяти 5, формирователь допусков 6, буферный накопитель 7, включающий блок управления записью 8, считыванием 9 и блок памяти 10, канал связи 11, блок вычитания 12, триггер 13 и формирователь кода 14.

Устройство работает следующим образом.

Входной сигнал с датчика через коммутатор 1 поступает на блок срав нения 2 и на вентили- 3 и 4.На другой вход блока сравнения с блока памяти 5 поступает предсказанное значение этого параметра. Блок сравнения определяет модуль разницы между истинным и предсказанным значениями входной величины и сравнивает его с величиной допустимого отклонения, поступаю аего с формирова/геля допусков 6. Если разница межД5 истинным и предсказанным значениями входной величины превышает величину заданного отклонения, то на выходе блока сравнения появляется сигнал, поступающий на буферный накопитель, содержащий блок управления записью 8, блок управления считыванием 9 и блок 10 для переключения адреса записи и откры. вает вентили 3 и 4. Входная информация поступает на запись в блок

памяти 10 буферного накопителя 7 и в блок памяти 5. Если разница меяоду истиннь1М и предсказанным значениями входного параметра меньше Зсщанной величины, то этот отсчет считается несущественным и не регистрируется. Затем переключается коммутатор, и схема переходит к анализу следующего параметра. Одновременно происходит циклическая выдача с буферного накопителя 7 с помощью блока управления считыванием 9 записанной в нем информации в канал связи с постянным тактом. Текущие адреса записи и считывания с блоков записи 8 и считывания 9 поступают на блок вычитания 12 и одновременно старший разряд адреса поступает на сброс триггера 13. Причем триггер устанавливается в единицу при переключении старшего разряда счетчика адреса записи в нуль и в нуль - при переключении в нуль старшего разряда адреса считывания. Выход триггера поступает на старший разряд вычитателя. Таким образом, на выход вычитателя будет все время вычисляться разница между кодами адреса записи и адреса считывания.- Подключение триггера позволяет сохранить знак этой разницы при переходах кодов адресов от всех единиц к нулям. Код разницы адресов записи и считывания поступает на формирователь допусков 6, причем при увеличении этой разницы коридор допусков увеличивается, что эквивалентно уменьшению количества существенных выборок и, следовательно, уменьшению скорости записиj и наоборот. Таким образом, величина коридора дискретизации устанавливается такой, что скорость записи будет равна скорости считывания. Сигналы о величине текущего коридора допусков поступают на формирователь кода 14, и соответствующий код программы, необходимый для расшифровки информации при обработке, поступает на запись в буферный накопитель.

Таким образом, при циклическом считывании информации из блока памяти с постоянным тактом между текущим адресом считывания и адресом ячейки, в которую записан последний существенный отсчет, в любой моMesHT времени имеется определенное число ячеек, в которые записана еще не переданная в канал связи информация. Это позволяет полностью исключить потери информации при обеспеч:ении равномерного ее потока и наиболее эффективно использовать возможности канала связи, что в конечном итоге повышает надежность устройства.

Формула изобретения .

Устройство для передачи информации, содержащее коммутатор, ключи.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи информации | 1981 |

|

SU1012311A1 |

| Устройство для передачи измерительной информации | 1982 |

|

SU1062753A1 |

| Устройство для сжатия информации | 1976 |

|

SU567174A1 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1990 |

|

SU1732380A1 |

| Передающее устройство адаптивной телеизмерительной системы | 1989 |

|

SU1679517A1 |

| Система управления многопозиционной индукционной нагревательной установкой | 1983 |

|

SU1121789A1 |

| Устройство для передачи телеизмерений с адаптивной коммутацией | 1982 |

|

SU1020849A1 |

| Устройство контроля качества датчиков времени | 1986 |

|

SU1422218A1 |

| Устройство для регистрации цифровой информации | 1986 |

|

SU1386915A2 |

| Буферное запоминающее устройство | 1981 |

|

SU1008793A1 |

Авторы

Даты

1980-09-23—Публикация

1978-12-18—Подача