11 Изобретение относится к преобразо вательной технике и может найти применение в автоматизированных электро термических установках с несколькими зонами управляемого индукционного нагрева при питании от тиристорного преобразователя частоты. Известны системы управления электр термических установок, содержащие источники питания и ряд других нагрузок, подключаемых с помощью силовы ключевых элементов, управляемых от специальной схемы синхронизации СО Недостатками этих систем являются узость функциональных возможностей, высокая сложность реализации и низка надежность регулирования, связанная с необходимостью иметь большое количество единиц силового оборудования и регулирующих устройств. Наличие дополнительной схемы синхронизации ведет к дополнительному усложнению системы управления. Алгоритм работы этих систем задан их схемой, поэтому функциональные возможности их ограни чены. Наиболее близкой по технической сущности является система управления многопозиционной индукционной нагревательной установкой, содержащая снабженный рмирователем импульсов инвертор, к выходу которого подключе ны по меньшей мере две нагрузки в виде колебательных контуров, настроенных на различные резонансные часто ты, блоки задания режимов нагрева и датчиков контроля технологических и электрических параметров нагрузок, выходы которых через коммутатор Связаны с формирователем импульсов инвертора..Работа системы заключается в поочередной подстройке частоты выходного тока инвертора под собственные частоты нагрузок, в этом случае мощность инвертора.поочередно и периодически вьщеляется в каждой наг рузке - в.течение настроенного состояния инвертора и нагрузки.С этой целью пересчетная схема периодически и поочередно подключает соответствующие определенным йагрузкам датчики контроля собственных частот к управляющему задающему генератору, обеспечивая подстройку его частоты под собственные частоты нагрузок 2). Недостатком известной системы являются ограниченные функциональные возможности, так как вариации регулирования осуществляются только изме 92 нением закона переключения пересчетной схемы, осуществление которого сложно и не позволяет использовать другие типы регулирования. Цель изобретения - расширение функциональньрс возможностей системы управления электротермической установкой. Поставленная цель достигается тем, что система управления многопозиционной индукционной нагревательной установкой, содержащая снабженный формирователем импульсов инвертор., к выходу которого подключены по меньшей мере две нагрузки, в виде колебательных контуров, настроенных на различные резонансные частоты, блоки задания режимов нагрева и датчиков контроля технологических и электрических па раметров нагрузок, выходы которых через коммутатор связаны с формирователем импульсов инвертора, снабжена процессором, шина ввода которого через введенные первый ключ и аналого-цифровой преобразователь связана с выходом коммутатора, а шина, адреса связана через введенный дешифратор адреса ввода с управляющим входом коммутатора непосредственно и через введенный первый блок задержки - с управляющим входом первого ключа, а через дешифратор адреса вывода и второй введенньй ключ - с адресным входом введенного буферного запом1шающего устройства, вькодные шины которого подключены к входам предустановки двух введенных двоичных реверсивных счетчиков, вход вычитания первого реверсивного счетчика соединен-с выходом введенного генератора тактовых импульсов, а выход - с управляющим входом формирователя импульсов инвертора, с входом вычитания второго реверсивного счетчика, с управляющим входом второго ключа и входом управления режимами запись-считывание буферного запоминающего устройства через введенный дополнительный формирователь импульсов и инвертор и через введенный второй блок задержки с входом синхронизации предустановки первого реверсивного счетчика и S-входом введенного RS-триггёра, выход которого подклочен к входу синхронизации предустановки втощзго реверсивного счетчика, связанного выходом с R-входом триггера непосред- . ственно, а с адресным входом буферного запоминающего устройства - через

введенный двоичный счетчик и ключ, управляющий вход которог подключен к выходу дополнительного формирователя импульсов.

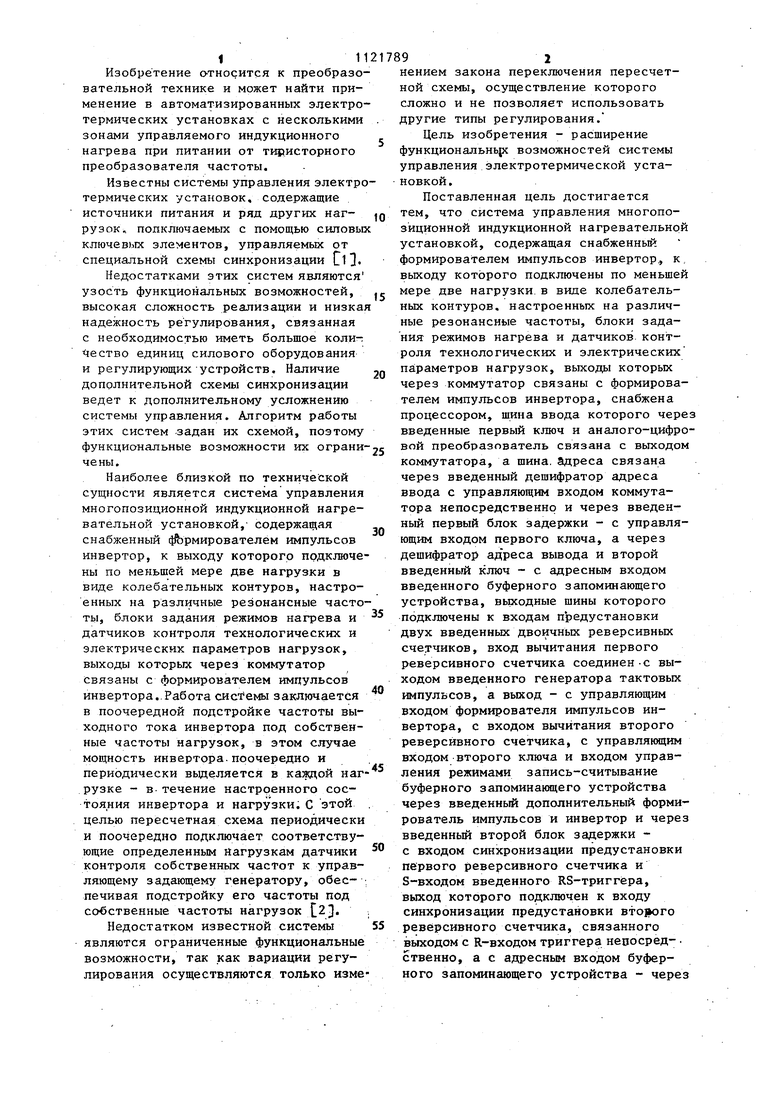

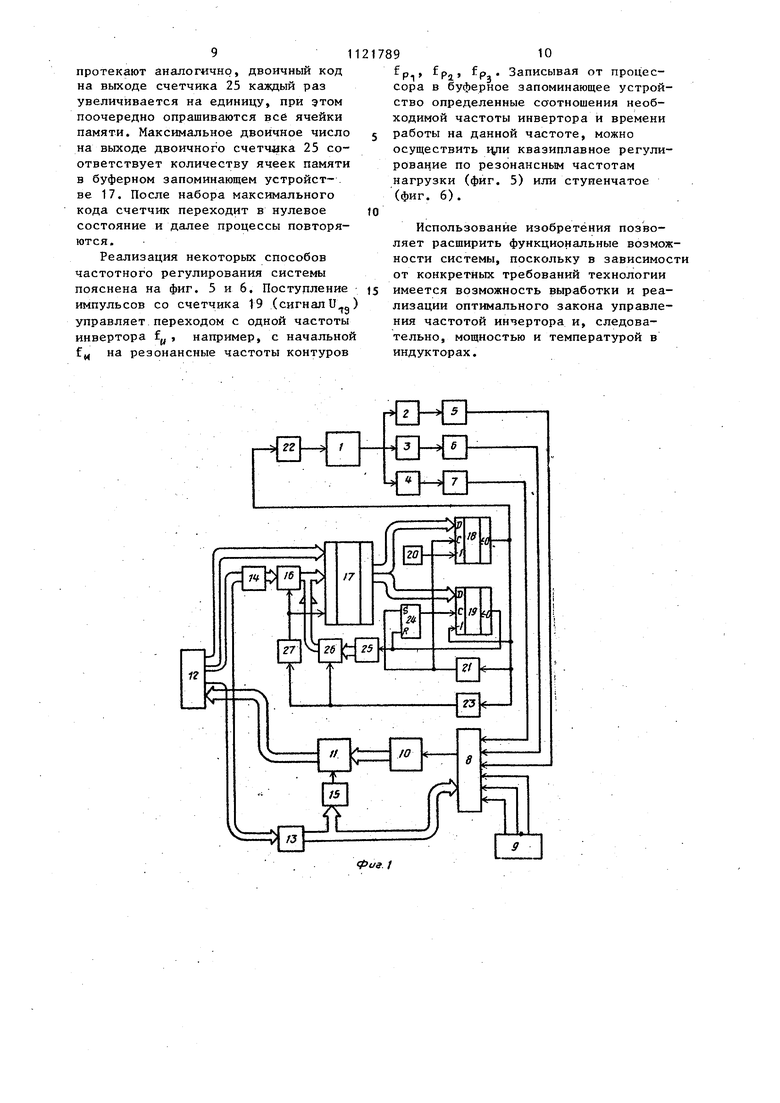

На фиг. 1 приведена ст()ук1, схема системы управления: на фиг. 2 временные пиягряммы циклов обменл информацией в системе; на фиг. 3 временные диаграммы формирования импульсов управления инвертором; на фиг. 4 - временные диаграммы, поясняющие процессы записи и считывания информации буферного запоминающего устройства; на фиг. 5 - временные диаграммы частотного регулирования системы при квазиплавном изменении частоты по резонансным частотам нагрузок; на фиг. 6 - временные диаграммы частотного регулирования системы Tipif ступенчатом изменении частоты.

Обозначения на временных диаграммах (фиг. 2-6) использованы в соответствии с позиционными обозначениями элементов фиг. 1.

Ьистема управления установки содержит инвертор 1, подключенньй к нагрузкам 2-4, выходы которых через датчики 5-7 подключены к коммутатору 8; одновременно к нему же подключен блок 9 задания режимов,выход коммутатора сигналов через аналого-цифровой преобразователь (А1Щ) 10 и первый ключ 11 подключен к шине ввода процессора 12, к шине адреса последнего подключены дешифратор 13 адреса ввода и дешифратор 14 адреса вывода, к выходу дешифратора 13 адреса ввода подсоединены блок 15 задержки и адресный вход коммутатора 8, к выходу дешифратора 14 адреса вывода через второй ключ 16 подключен адресный вход буферного запоминающего устройства 17, к выходным шинам которого, разделенным на две группы, подсоединены входы предустановки двоичных реверсивньк счетчиков 18 и 19. К входу вычитания двоичного реверсивного счетчика 18 подключен генератор 20 тактовых импульсов, а к его выходу подсоединены входы двоичного реверсивного счетчика 1.9, блок 21 задержки, формирователя 22 импульсов инвертора и дополнительного формирователя 23, к выходу двоичного реверсивного счетчика 19 подключены R-вход RS-триггера 24 и через двоичный счетчик 25 и третий ключ 26 - адресный вход буферного запоминающего устройства 17. Выход блока 21 задержки подсоединен к входу синхронизации предустановки двоичного реверсивного счетчика 18 и к S-входу RS-триггера 24, выход которого подключен к входу синхронизации предустановки двоичного реверсивного счетчика 19, выход формирователя 22 импульсов соединен с входо управления ключа 26 и через инвертор 27 с управляющим входом ключа 16 и входом управления режимами записьсчитывание буферного запоминающего устройства 17, выход формирователя 2 подключен к входу инвертора 1.

На основании информации, получе ной от датчиков технологических и электрических параметров 5-7 и зада-, ния от блока 9 задания режимов, система управления вырабатывает импульсы управления с частотой, изменяющейся по необходимому для распределения мощности закону. Распределение мощности основано на настройке резонансных контуров нагрузок на отличающиеся частоты и дифференцированной подаче мощности за счет подстройки частоты инвертора под указанные частоты при использовании различных законов подстройки, которые реализуются в системе

Работа системы управления (фиг. 1) производится в режиме приема и передачи информации.

В режиме приема процессор 12 устанавливает на шине адреса адрес нужного датчика контроля технологического или электрического параметра (элементы 5-7) или сигнала соответствующего канала блока 9 задания режима, при этом адрес преобразуется дешифратором 13 в сигналы, открывшощие определенный канал коммутатора 8 одновременно с этим указанные сигналы поступают на вход схемы 15 задержки - Сигнал лт коммутатора 8,обозначенный UQ (фиг. 2), поступает на АЦП 10, который преобразует аналоговый сигналВ цифровую форму, представляемую в виде двоичного числа с п разрядами, где п - количество разрядов. С выхода А1Щ -сигнал U (фиг. 2) по шине из п линий поступает на вход ключа 11, открывание которого и, соответственно подключение к шине ввода процессора производится сигналом с выхода блока 15 задержки, который необходим для вьщачи информации в процессо только после полного окончания преобразования А1Щ. Длительность задержки выбирается не менее времени преобразования АЦП 10 (и и. , фиг. 2), Передача информации из процессора начинается установкой адресов приемных устройств, дешифруемых дешифратором 14 адреса вывода. Появление на выходе дешифратора 14 адреса вывода сигнала (фиг. 2) означает, что процессор готов к передаче информации в буферное запоминающее устройство 17, при этом запись инфор мации в последнее будет возможна при наличии разрешающего сигнала с HHBep тора 27, открывающего ключ 16 и пере водящего буферное запоминающее устро ство в режим записи информации (временные диаграммы 21 16 фиг. 2). Работа управляемого задающего генератора (фиг. 1), выполненного на генераторе 20 тактовых импульсов, реверсивном двоичном счетчике 18 и формирователе 22 импульсов,происходи следующим образом. Информация с выхода буферного запоминающего устройства в двоичной форме подается на входы предустановк реверсивного двоичного счетчика 18, при появлении импульса на его входе синхронизации предустановки указанна информация переписывается в счетчик 18 - устанавливает триггеры, входящие в состав указанного счетчика. Импульсы тактового генератора, поступающие на вход вычитания реверсивного двоичного счетчика 18, вычитают из двоичного числа, записанного в указанном счетчике ,и обнуление счетчика, т.е. установка всех его тригге ров в ноль,происходит после поступления количества импульсов, численно равного двоичному числу, записанному в счетчик. При обнулении счетчика на его выходе появляется импульс, который после прохождения через формирователь 22 импульсов используется как импульс управления инвертором, т.е. является выходным импульсом управляемого задающего генератора. Одновременно импульс с выхода реверсивного двоичного счетчика 18 подается на вход вычитания реверсивного двоичног счетчика 19. При этом выходной импульс на выходе реверсивного двоич ного счетчика 19 появляется после прохода импульсов управления, количество которых равно двоичному числу предварительно записанному в данный счетчик с выхода буферного запоминаюп;его устройства 17. В моменты обнуления реверсивных двоичных счетчиков 18 и 19 производится повторная их предустановка двоичной информацией с выхода буферного запоминающего устройства 17. Первоначально в реверсивные двоичные счетчики записываются соответственно числа п и К,. После поступления на вход счетчика 18 п импульсов (сигнал 2о ° выходе появляется выходной импульс (сигнал J-.g ) после этого в счетчик 18 записывается следующее число п. и после прохода импульсов.с количеством П2 формируется второй выходной импульс (сигналы U ии). далее процессы протекают аналогично описанному. Аналогично происходит работа счетчика 19, на который поступают выходные импульсы счетчика 18, при этом после прохода К импульсов (сигнал ) формируется выходной импульс (сигнал U ), и далее импульсы формируются после Кл импульсов, К., импульсов и т.д. Каждый выходной импульс счетчика 18 (сигнал ) после формирователя 22импульсов формирует импульс управления (сигнал и ), в соответствии с которым на выходе инвертора 1 появляетсяимпульс выходного тока (напряжения) U (J). Процессы записи информации в буферное запоминающее устройство 17 и перезаписи в реверсивные двоичные счетчики 18 и 19 происходят следующим образом. В исходном состоянии при отсутствии выходных импульсов счетчиков 18 и 19 на выходе формирователя 23 импульсов сигналотсутствует (логический ноль), вследствие чего ключ 26 отключает выход двоичного счетчика 25 от адресного входа буферного запоминакнцего устройства 17, одновременно инвертированный сигнал формирователя 23импульсов после инвертирующего элемента 27 открывает ключ 16, подключая выход дешифратора 14 адреса вывода к адресному входу буферного запоминающего устройства 17, при этом этот же сигнал переводит буферное :запоминающее устройство в запись информации. В этом состоянии процессор, устанавливая адреса ячеек памяти буферного запоминающего устройства 17, производит запись информации в последнее. Записываемое информационное слово условно г тбито на группы старших и младших бит, т. слово, состоящее из Р бит, содержит q бит старшей группы и г i- М1..л.гей: Р q + г Старшая группа из q бит переписывается в счетчик 18 и кодирует количество импульсов тактового генератора 20, после прохода которых формируется выходной импульс счетчика 18, т.е. выходные импульсы управляемого задающего генератора, которы определяют частоту тока инвертора. Младшая группа из г бит переписывается в счетчик 19 и кодирует количес во выходных импульсов счетчика 18, после прихода которых формируется выходной импульс счетчика 19. Перезапись информации в счетчики 18 и 19 происходит после поступления импульса на их входы синхронизации предустановки. Указанные импульсы для счетчика 18 формируются из его выходных импульсов путем временной задержки с помощью блока 21 задержки Для счетчика 19 импульсы формируются RS-триггером 24, при этом после поступления на его R-вход выходного импульса счетчика 19 триггер переходит в нулевое состояние, и после прихода задержанного импульса с блок задержки 21 RS-триггер 24 переходит в единичное состояние, положительный перепад которого синхронизирует пред установку счетчика 19. Задержка №4пульсов предустановки необходима для того, чтобы на выходе буферного запоминающего устройства 17 успела установиться необходимая для перезапи си информация. Выходные импульсы счетчика 19 считываются двоичньм счетчиЛом 25, который устанавливает двоичные адрес ячеек памяти буферного запоминающего устройства 17. Количество состояний и их двоичная кодировка у двоичного счетчика 25 соответствуют количеству и кодировке ячеек памяти буферного запоминающего устройства 17. Каждый раз при появлении выходного импульса счетчика 18 формирователь 23 датульсов выдает импульс, в течение которого информация с выхода двоичного счетчика 25 через открытый ключ 26 подается на адресный вход буферного запоминающего устройства 17, одновременно через инвертор 27 указанный импульс отключает с помощью ключа 16 дешифратор 14 адреса ввода от адресной иины буферного запоминающего устройства 17 и переводит последнее в режим считывания информации из ячейки с адресом, задаваемым двоичным счетчиком 25. Пусть в счетчики 18 и 19 предварительно записаны числа п и К. После поступления от тактового генератора 20 на вход счетчика 18 количества импульсов, величина которого записана в процессе предыдущей предустановки {л),на его выходе появляется выходной импульс - сигнал и , который вызывает- появление на выходе формирователя импульсов 22 импульса с длительностью с, который открывает ключ 26 (сигнал U- ), и через инвертор 27 закрывает ключ 16 (сигнал и), одновременно переводя буферное запоминающее устройство 17 в режим считывания информации. На выходе буферного запоминающего устройства 17 с задержкой по времени, равной t (длительность задержки в общем случае определяется техническими данными примененного элемента памяти), проявляется информация, записанная в ячейке памяти с адресом, определяемым выходным сигналом двоичного счетчика 25. В момент времени t на входе синхронизации предустановки счетчика 18 появляется задержанный блоком 21 задержки выходной импульс счетчика- 18, и в счетчик 18 переписывается информация из буферного запоминающего устройства 17 (старшая группа из q бит). После того, как на вход счетчика 19 поступило К импульсов с,выхода счетчика 18, на его выходе появляется выходной импульс (сигнал ), который переключает RS-триггер 24 в нулевое состояние (сигнал U ) и увеличивает двоичную информацию двоичного сч тчика 25 на единицу. Таким образом, на адресный вход буферного запоминающего устройства поступает новый код и на выходе его появляется информация, записанная в следующей ячейке памяти. При поступлении в момент времени t задержанного импульса с блока 21 RS-триггер переключается в единичное состояние (сигнал и„ ), при этом производится перезапись информации из буферного запоминающего устройства 17 в счетчик 19 (переписывается младшая группа из г бит). Описанные процессы далее

протекают аналогично, двоичный код на выходе счетчика 25 каждый раз увеличивается на единицу, при этом поочередно опрашиваются веб ячейки памяти. Максимальное двоичное число на выходе двоичного счетчика 25 соответствует количеству ячеек памяти в буферном запоминающем устройст- . не 17. После набора максимального кода счетчик переходит в нулевое состояние и далее процессы повторяются.

Реализация некоторых способов частотного регулирования системы пояснена на фиг. 5 и 6. Поступление импульсов со счетчика 19 (сигнал управляет переходом с одной частоты инвертора f, например, с начальной fu на резонансные частоты контуров

fpifpj

PI Ра Pa Записывая от процессора в буферное запоминающее устройство определенные соотношения необходимой частоты инвертора и времени работы на данной частоте, можно осуществить цди квазиплавное регулирование по резонансным частотам нагрузки (фиг. 5) или ступенчатое (фиг. 6).

Использование изобретения позволяет расширить функциональные возможности системы, поскольку в зависимос от конкретных требований технологии имеется возможность выработки и реализации оптимального закона управления частотой инвертора и, следовательно, мощностью и температурой в индукторах.

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемая линия задержки | 1986 |

|

SU1406753A1 |

| Устройство для анализа логических состояний | 1980 |

|

SU1096648A1 |

| Устройство для определения местоположения источника акустической эмиссии | 1987 |

|

SU1499224A1 |

| Многоканальная система измерения и регистрации | 1988 |

|

SU1707546A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Устройство для передачи информации | 1981 |

|

SU1012311A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| Устройство для ввода информации | 1987 |

|

SU1509914A1 |

| Фильтр | 1983 |

|

SU1140229A1 |

| Устройство для передачи цифровой информации | 1983 |

|

SU1141436A1 |

СИСТЕМА УПРАВЛЕНИЯ МНОГОПОЗШЩОННОЙ ИНДУКЦИОННОЙ НАГРЕВАТЕЛЬНОЙ УСТАНОВКОЙ, содержащая снабженный формирователем импульсов инвер.тор, к выходу которого подключены по меньшей мере две нагрузки в виде колебательных контуров, настроенных на различные резонансные частоты, блоки задания режимов нагрева и датчиков контроля технологических и электрических параметров нагрузок, выходы которых через коммутатор связаны с формирователем импульсов инвертора, о т л ич а юща яся тем, что, с целью расширения функциональных, возможностей, система снабжена про- цессором, ина BJBoдa которого через введенные первый ключ и аналого-цифровой преобразователь связана с выходом ко№ утатора, а шина адреса связана через введенный дешифратор адреса ввода с управляющим входом коммутатора непосредственно и через введенный первый блок задержки - с управляющим входом первого ключа, а через дешифратор адреса вывода и второй введенный ключ - с а дресным входом введенного буферного запоминающего устройства, выходные шины которого подключены к входам предустановки двух введенных двоичных реверсивных счетчиков, вход вычитания первого реверсивного счетчика соединен с выходом введенного генератора тактовых импульсов, а выход - с управляющим входом формирователя импульсов инвертора, с входом вычитания второго § реверсивного счетчика, с управляющим входом второго ключа и входом управления режимами запись-считывание буферного запоминающего устройства через введенный дополнительный формирователь импульсов и инвертор и через введенный второй блок задержки - с входом синхронизации предустановки первого реверсивного счетчика 1С и S-входом введенного RS-триггера, выход которого подключен к входу хронизации предустановки второго ре00 версивного счетчика, связанного выхосо дом с R-входом триггера непосредственно, а с адресным входом буферного запоминающег 1уустройства - через введенный двоичный счетчик и третий ключ, управляющий вход которого подключен к выходу дополнительного формирователя импульсов.

Г

е - (у8 приемаrrr - cfi/ff/roB nepea af/u

f

fi Uff/r Lrr . 1 r

ue. t

/7f Пг

20

«ii

ifi

Uia

fl4t/fffl

П2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ управления процессом электрошлакового переплава в установках для выплавки полых слитков | 1970 |

|

SU371807A1 |

| Обогреваемый отработавшими газами карбюратор для двигателей внутреннего горения | 1921 |

|

SU321A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство распределения мощности инвертора | 1977 |

|

SU657571A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1984-10-30—Публикация

1983-07-26—Подача