Изобретение относится к зэпоминающим устройствам и может быть использовано в измерительных системах при сопряжении функциональных устройств, работающих с различными скоростями преобразования и передачи информации, имеющей кадровую структуру.

Известно буферное запоминающее устройство, содержащее накопитель с шинами записи и считывания, счетчики адресов записи и считывания 1J.

Существенным недостатком указанного .устройства является низкая надежность работы при асинхронном поступлении импульсов записи и считывания на соответствующие счетчики от периферийных устройств передачи и приема сигналов.

Наиболее близким к предлагаемому является буферное запоминающее устройство (БЗУ), содержащее накопитель, счетчики адресов записи и считывания, выходы которых через коммутатор подключены к накопителю, при этом первые и соединенные между собой вторые входы накопителя и коммутатора подключены к блоку управления, соединенному с двумя входными, шинами. Кроме того, входы и выходы обоих счетчиков подключены к блоку управления, два выхода которого соединены с выходными шинами, а к двум входным шинам подключен генератор импульсов 2.

Недостатком известного устройства является узкая область применения, так как оно не может быть использовано для работы с информацией, имеющей кадровую структуру. Это объясняется тем, что в этом устройстве запись и считывание сигналов с БЗУ осуществляется произвольно, без согласования входных и выходных информационных структур со схемой управления накопителем, а также тем, что используемый рабочий объем накопителя не связан с числом кадровых структур сигналов, поступающих на БЗУ. В измерительных системах с временным разделением каналов используют, как правило, режим работы, при котором все периферийные коммутаторы синхронизированы одним внешним низкочастотным маркером. Считанная с буферного запоминающего устройства информация, поступающая на один из каналов центрального приемного коммутатора, должна быть синхронизирована с информацией, поступающей

на другие входы э-того коммутатора; j Таким образом, источник информации на входе буферного запоминающего устройства имеет кадровую структу- ру. При этом маркеры кадров входной и выходной информации могут отличаться как по частоте, так и по фазе. Так как в известном устройстве нет привязки маркера информационного кадра к адресу накопителя буферного запоминающего устройства как при записи, так и при считывании, невозможно правильно принять информацию, запомнить принятую,информацию и передать 5 в центральный коммутатор.

Цель изобретения - расширение области применения устройства за счет возможности работы с кадровыми информационными структурами.

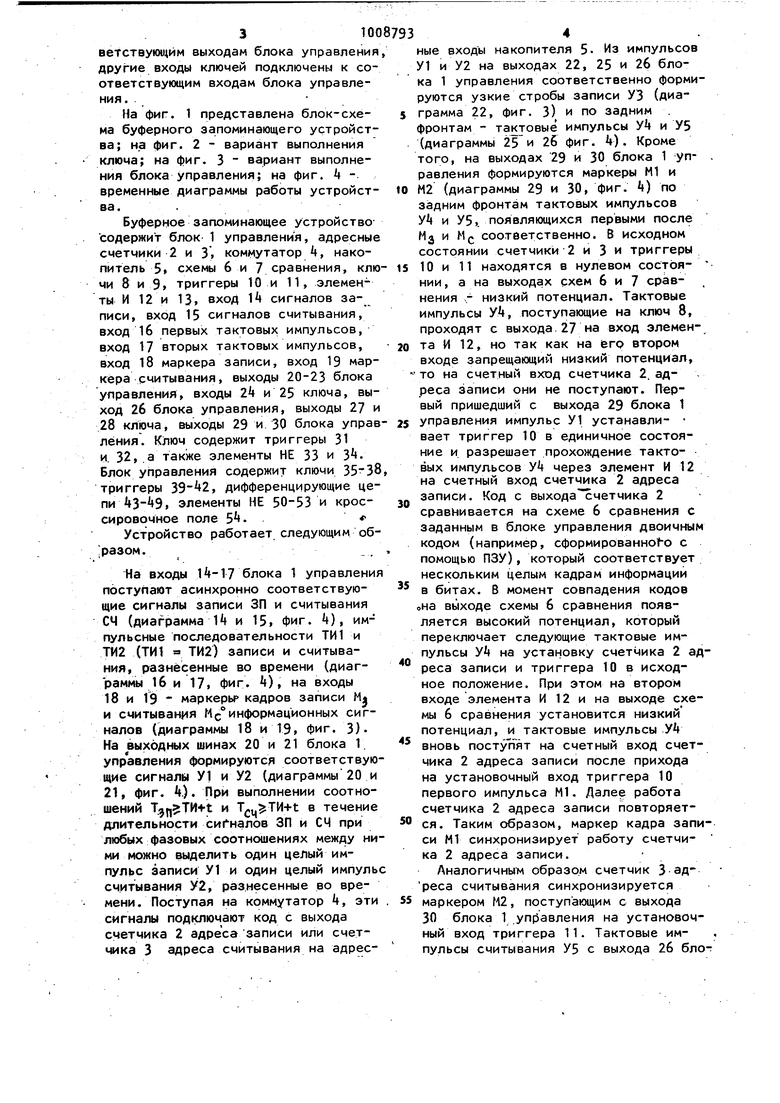

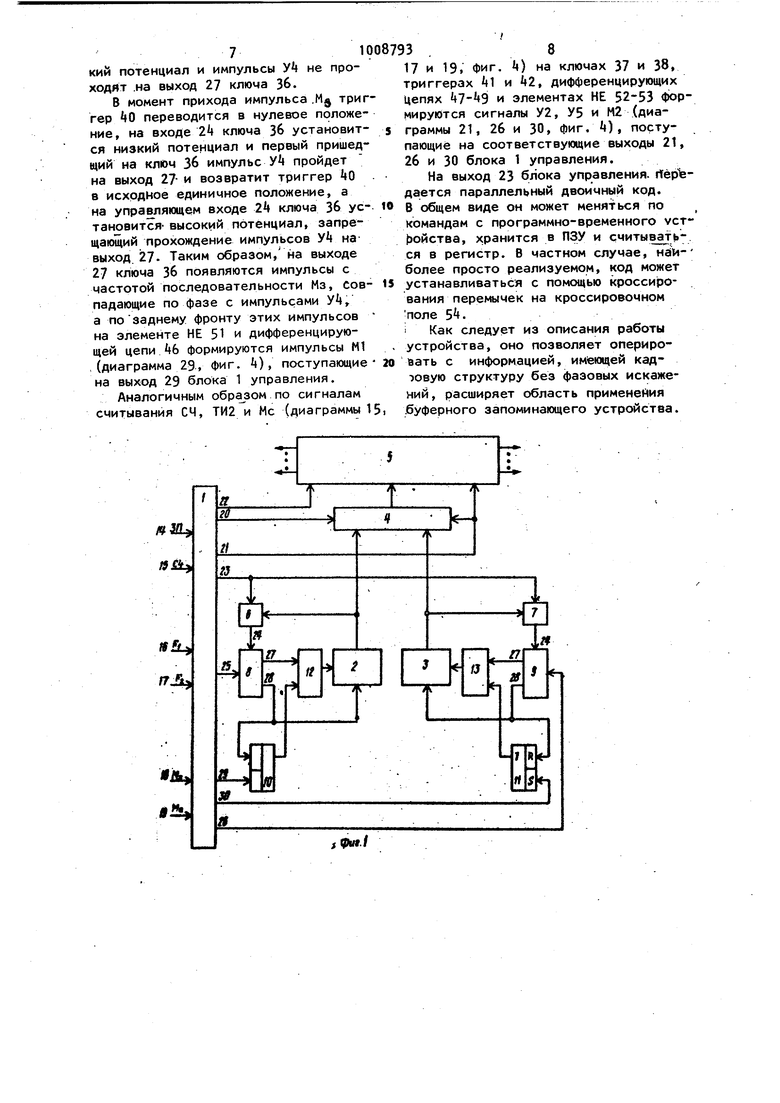

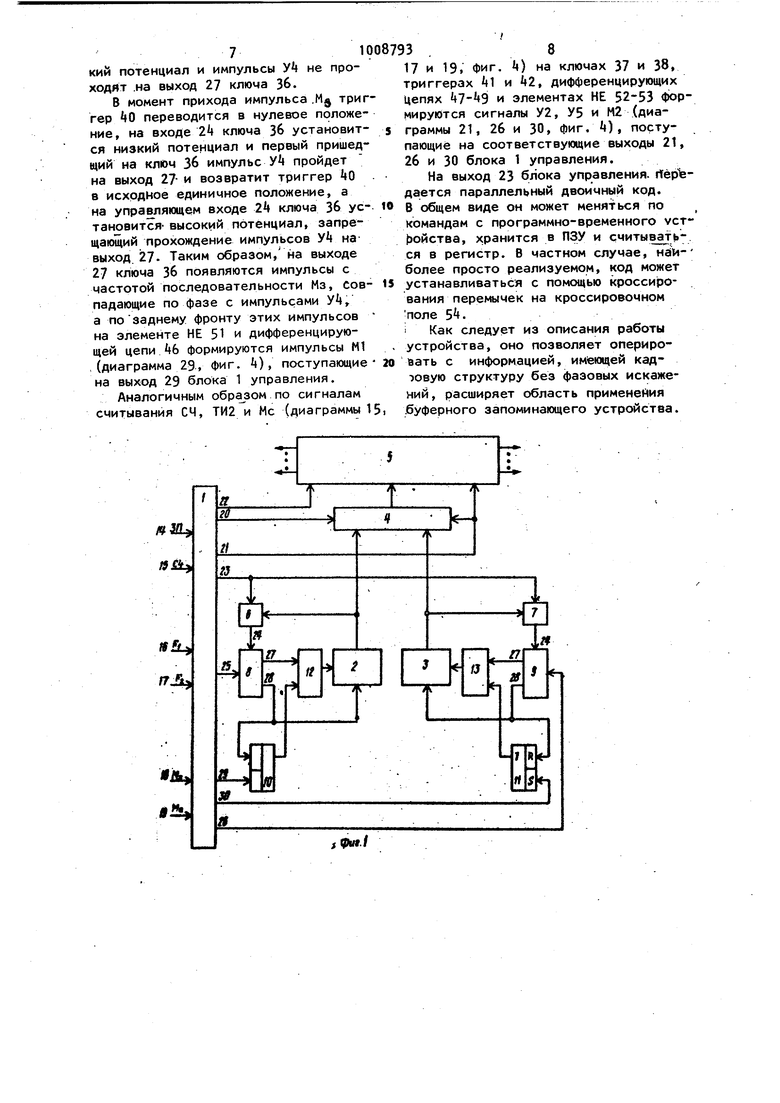

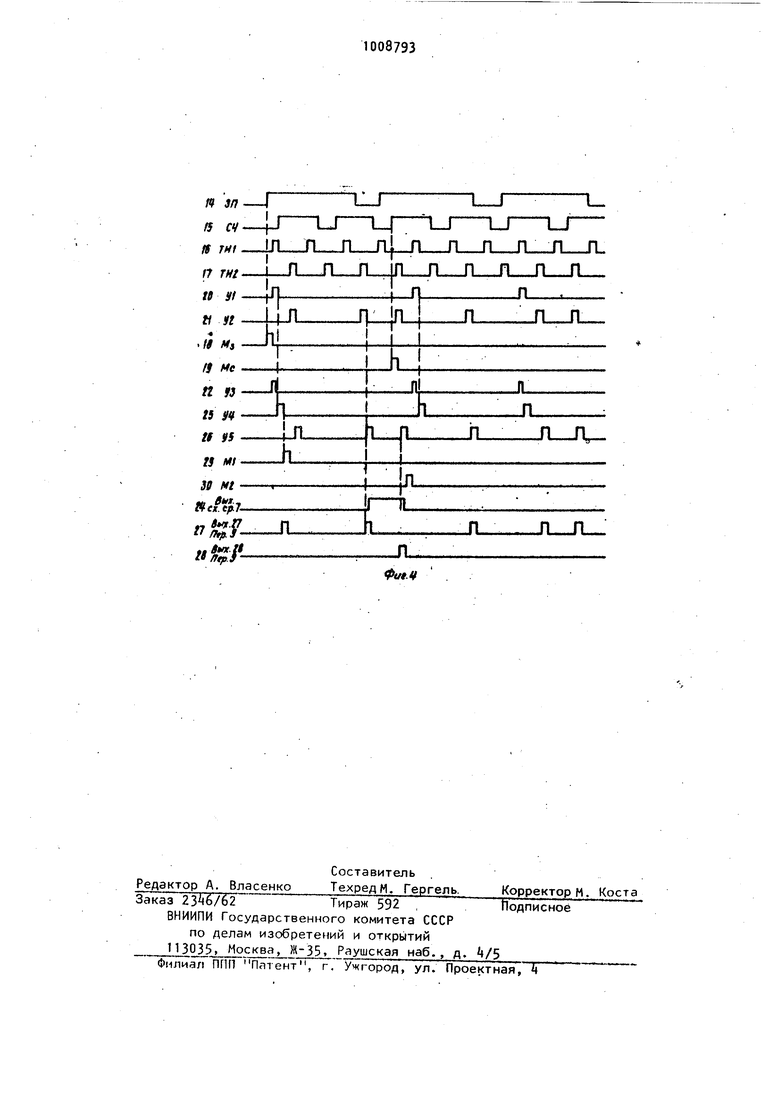

Поставленная цель достигается тем, что в буферное запоминающее устройство, содержащее накопитель, информационные входы и выходы которого являются соответственно информационными входами и выходами устройства, один управляющий вход накопителя подключен к выходу коммутатора, управляющие .входы, которого подключены к соответствующим выходам блока управления, другие управляющие входы накопителя подключены к соответствующим выходам блока управления, информационные входы коммутатора подключе-. ны к выходам первого и второго адресных счетчиков, дополнительно введены ключи, схемы сравнения, элементы И и триггеры, одни входы которых подключены к соответствующим выходам блока управления, выходы первого и второго триггеров подключены к одним входам соответственно п рвого и второго элементов И, другие входы которых подключены к одним выходам соответственно первого и второго ключей, выходы первого и .второго, элементов И подключены к одним входам соответственно первого и второго адресных счетчиков, другие входы которых подключены к одним входам соответственно первого и второго триггеров и к другим выходам соответственно первого и второго ключей, одни входы первого и второго ключёи подключены к выходам соответственно первой и второй схемы сравнения, одни входы которых подключены к выxoдa il соотв.етственно первого и второго адресных счетчиков, другие входы схем сравнения подключены к соответствущйм выходам блока управлени другие входы ключей подключены к со ответствующим входам блока управления. На фиг. 1 представлена блок-схема буферного запоминающего устройства; на фиг. 2 - вариант выполнения ключа; на фиг. 3 вариант выполнения блока управления; на фиг. 4 -. временные диаграммы работы устройст ва. . Буферное запоминающее устройство содержит блок 1 управления, адресные счетчики 2 и 3, коммутатор 4, накопитель 5 cxeNftji 6 и 7 сравнения, клю чи 8 и 9 триггеры 10 и 11, элементы И 12 и 13, вход 14 сигналов записи, вход 15 сигналов считывания, вход 16 первых тактовых импульсов, вход 17 вторых тактовых импульсов, вход 18 маркера записи, вход 19 маркера считывания, выходы 20-23 блока управления, входы 2k и 25 ключа, выход 2б блока управления, выходы 27 и 28 ключа, выходы 29 и 30 блока управ лёния. Ключ содержит триггеры 31 и. 32, .а также элементы НЕ 33 и 34. Блок управления содержит ключи триггеры , дифференцирующие цепи 43-49, элементы НЕ 50-53 и кроссировочное поле 54. Устройство работает следующим об разом. . На входы 14-17 блока 1 управлени поступают асинхронно соответствующие сигналы записи ЗП и считывания СЧ (диаграмма 14 и 15, фиг. 4), импульсные последовательности ТИ1 и ТИ2 (ТИ1 ТИ2) записи и считывания, разнесенные во времени (диаграммы 16 и 17, фиг. 4), на входы 18 и 191 - маркерьр кадров записи М и считывания Мс информационных сигналов (диаграммы 18 и 19, фиг. 3). На выходных шинах 20 и 21 блока 1. управяения формируются соответствую щие сигналы У1 и У2 (диаграммы20 и 21, фиг. 4.). При выполнении соотношений , и в течение длительности сигналов ЗП и СЧ при любых фазовых соотношениях между ни ми можно выделить один целый импульс записи У1 и один целый импуль считывания У2, разнесенные во времени. Поступая на коммутатор 4, эти сигналы подключают код с выхода счетчика 2 адреса записи или счет tftiKa 3 адреса считывания на адресные входы накопителя 5- Из импульсов У1 и У2 на выходах 22, 25 и 26 блока 1 управления соответственно формируются узкие стробы записи УЗ (диаграмма 22, фиг. 3) и по задним . фронтам - тактовые импульсы У4 и У5 (диаграммы 25 и 2б фиг. k). Кроме того, на выходах 29 и 30 блока 1 управления формируются маркеры Ml и М2 (диаграммы 29 и 30, фиг. 4) по задним фронтам тактовых импульсов yk и У 5 ..появляющихся первыми после Мз и MC соответственно. В исходном состоянии счетчики 2 и 3 и триггеры 10 и 11 находятся в нулевом состояНИИ, а на выходах схем 6 и 7 сравнения ,- низкий потенциал. Тактовые импульсы yk, поступающие на ключ 8, проходят с выхода.27 на вход элемента И 12, но так как на его втором входе запрещающий низкий потенциал, то на счетный вход счетчика 2. адреса записи они не поступают. Первый пришедший с выхода 29 блока 1 управления импульс У1 устанавли- ет триггер 10 в единичное состояние и разрешает прохождение тактовых импульсов У4 через элемент И 12 на счетный вход счетчика 2 адреса записи. Код с выхода четчика 2 сравнивается на схеме 6 сравнения с заданным в блоке управления двоичным кодом (например, cфopмиpoвaннo o с помощью ПЗУ), который соответствует нескольким целым кадрам информации в битах. В момент совпадения кодов на выходе схемы 6 сравнения появляется высокий потенциал, который переключает следующие тактовые импульсы У4 на установку счетчика 2 адреса записи и триггера 10 в исходное положение. При этом на втором входе элемента И 12 и на выходе схемы 6 сравнения установится низкий потенциал, и тактовые импульсы У4 вновь поступят на счетный вход счетчика 2 адреса записи после прихода на установочный вход триггера 10 первого импульса Ml. Далее работа счетчика 2 адреса записи повторяется. Таким образом, маркер кадра записи М1 синхронизирует работу счетчика 2 адреса записи. Аналогичным образом счетчик 3 адреса считывания синхронизируется маркером М2, поступающим с выхода 30 блока 1 уп|3авления на установочный вход триггера 11. Тактовые импульсы считывания У5 с выхода 2б блока 1 управления поступают на вход ключа 9, управляемый по входу 2 сигналом с выхода схемы 7 сравнения После прихода на триггер 11 маркере М2 тактовые импульсы с выхода 27 ключа 9 проходят через элемент И 13 на счетный вход счетчика 3 адреса считывания, выходной код которого сравнивается с заданным в блоке 1 управления (выход 23) на схеме 7 сравнения. После совпадения кодов следующий тактовый импульс считывания У5 устанавливает счетчик 3 .адре са считывания и триггер 11 в исходное положение, а пришедший за ним импульс М2 вновь разрешает прохождение тактовых импульсов У5 на счет ный вход счетчика 3 адреса считывания и так далее. Оба счетчика, и адреса записи и адреса считывания, работают в цикли ческом режиме. На любом цикле всегда сохраняется соответствие между адресом накопителя и номером слова кадра информации. Так, всегда по ne вому адресу накопител я записывается и считывается первое слово, по второму - второе и т.д. Это означает, что на выходе буферного запоминающего устройства сохраняются входные фазовые соотношения между информационным кадром и низкочастотным маркером. В качестве ключей 8 и 9 использу ются устройства, функционально пред ставляющие собой переключатель с са моблокировкой. Оба ключа 8 и 9 работают одинаково. В качестве примера рассмотрим работу ключа 9 управляющего счетчика 3 адресов считывания. На вход 26 ключа 9 поступает импульсная последовательность У5. Пока на входе 2 ключа, а следователь но, и на входе сброса триггера 31 держится низкий потенциал, на его инверсном выходе - высокий потенциал До прихода импульса на вход 2б ключа на прямом выходе 31 и инверсном выходе 32 тригге()ов высокие потенци лы, и вентиль первого триггера 31 о крыт для прохождения тактовых импульсов У5, а вентиль второго триггера 32 - закрыт. Пока на входе 2Ц ключа 9 низкий потенциал, все импульсы У5 проходят через вентиль триггера 31 и элемент НЕ 33 на выход 27 ключа 9, а следовательно, и 93 . « hfa вход элемента И 13 (диаграмма 27, фиг. 4). ,При поступлении на счетный -ВХОД адресного счетчика 3 предпоследнего импульса У5 на входах схемы 7 сравнения устанавливаются одинаковые коды, а на выходе появляется высокий потенциал (диаграмма 24, фиг. 4). Поступающий на вход переключателя последний импульс У5 .проходит через открытый вентиль триггера 32 и элемент НЕ З на выход 28 (диаграмма 28, фиг. ) ключа 9 сбрасывает cчeтчиJ 3 адреса считывания, а на выходе схемы 7 сравнения устанавливается низкийТютенциал. Блокуправления работает следую1ЦЙМ образом. В исходном состоянии триггер 39 находится в единичном положении, при этом импульсы последовательности ТИ (диаграмма 16, фиг. 4), поступающие на вход 25 ключа 35, не проходят на выход 27, так как на его управляющем входе 2 высокий потенциал. При поступлении на вход Т блока управления сигнала записи ЗП (диаграмма 1, фиг. Ц) происходит дифференцирование переднего фронта ЗП (положительного) на дифференцирующей цепи 43. Этот импульс переводит триггер 39 в нулевое положение, на входе 2k ключа 35 появляется низкий потенциал, и первый после этого приходящий импульс последовательности ТИ1 проходит на выход 27 ключа 35. устанавливает триггер 39 в исходное единичное состояние и проходит на выход 20 блока управления (диаграмма 20, фиг. h). Таким образом, на выходе 20 блока управления формируются импульсы У1 с частотой сигнала записи ЗП и фазой импульсов ТИ1. На дифференцирующей цепи kk из импульсов У1 формируются узкие импульсы УЗ (диаграмма 22, фиг. 4), поступающие на выход 22 блока 1 управления, а на инверторе 50 и дифференцирующей.цепи kS по заднему фронту импульсов У1 формируются импульсы У (диаграмма 25, фиг. k). Поступая на выход 25 блока 1 управления, импульсы У подаются также на вход 25 ключа Зб, выход 27 которого соединен с входом триггера 0, На вход триггера kO подаются импульсы f1 (диаграмма 18, фиг. 4) . 8 исходном состоянии ,до прихода импульса М,з триггер kO находится в единичнрм положении, а следовательно, на входе 2k ключа Зб высо710087кий потенциал и импульсы У не проходят .на выход 27 ключа 36. В момент прихода импульса .М триггер 0 переводится в нулевое положение, на входе 24 ключа Зб установит- s ся низкий потенциал и первый пришедщий на клич 36 импульс У пройдет на выход 27- и возвратит триггер 0 в исходное единичное положение, а на управляющем входе 2А ключа 36 ус- ю танрвится-высокий потенциал, запрещающий прохождение импульсов У на выход 27. Таким образом, йа выходе 27 ключа 36 появляются импульсы с частотой последовательности Мз, сов- 15 падающие по фазе с импульсами У, а позаднему фронту этих импульсов на элементе НЕ 51 и дифференцирующей цепи 46 формируются импульсы Ml . (диаграмма 29, фиг. 4), поступакмцие м на выход 29 блока 1 управления. Аналогичным образом по сигналам /AMOJIV I ПМП011-1 wx|.. - . .- -- считывания СЧ, ТИ2 и Мс (диаграммы 15i 3 .8 17 и 19, Фиг. 4) на ключах 37 и 38, триггерах tl и , дифференцирующих цепях kJ-kS и элементах НЕ 52-53 формируются сигналы У2, У5 и М2 (диаграммы 21, 26 и 30, фиг,Ч) , поступающие на соответствующие выходы 21, 26 и 30 блока 1 управления, На выход 23 блока управления, rfepleдается параллельный двоичный код. в общем виде он может меняться по командам с программно-временного УСТ|)ойства, хранится в ПЗУ и считываться в регистр. В частном случае, нЗйболее просто реализуемом, код может устанавливаться с покющью кроссирования перемычек на кроссировочном попе 5. Как следует из описания работы устройства, оно позволяет опериройать с информацией, имеющей кадэовую структуру без фазовых искажений, расширяет область применения ,,,,,. у ,... ,, буферного запоминающего устройства.

(риег

/ff

/ У/

У5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи информации | 1981 |

|

SU1012311A1 |

| Устройство для передачи измерительной информации | 1982 |

|

SU1062753A1 |

| Устройство для контроля оперативной памяти | 1986 |

|

SU1401520A2 |

| Запоминающее устройство | 1983 |

|

SU1116458A1 |

| БИБЛИОТЕЧКА _J_Р. Г. Сафаров | 1972 |

|

SU328456A1 |

| Буферное запоминающее устройство | 1983 |

|

SU1096692A1 |

| Устройство для сопряжения между абонентами | 1988 |

|

SU1594550A1 |

| Устройство управления для процессора быстрого преобразования Фурье | 1983 |

|

SU1111173A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1111202A1 |

| Устройство для контроля оперативной памяти | 1984 |

|

SU1226535A1 |

ЗП

j /7

2

/5 f

Л

Me

( / /Гросс

I поле .

L

фиг.д

f W/

/Р

26 45

Ц-И

Jff М2

bZ3

Авторы

Даты

1983-03-30—Публикация

1981-02-13—Подача