(54) УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК В БЛОКАХ ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исправления ошибок в блоке памяти | 1978 |

|

SU868841A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1043743A1 |

| Запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1127012A1 |

| Устройство для контроля блоков памяти | 1978 |

|

SU765883A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1026165A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU864339A1 |

| Запоминающее устройство с исправлением ошибок | 1984 |

|

SU1226536A1 |

| Запоминающее устройство с исправлением дефектов и ошибок | 1987 |

|

SU1536445A1 |

| Устройство для коррекции отказов в полупроводниковой памяти | 1982 |

|

SU1049981A1 |

1

Изобретение относится к запоминающим устройствам и может быть использовано для исправления ошибок в блоках памяти, т.е. как средство обеспечения работоспособности блока памяти, содержащего дефектные запоминающие элементы.

Под дефектами понимаются неисправности элементов памяти, проявляющиеся в том, что по определенным адресам, в определенных (дефектных) разрядах блока памяти, вместо любого из двоичных символов О и 1, может надежно храниться или только О, или только 1.

Известно устройство для исправления ошибок в блоках памяти позволяющее компенсировать дефекты в одном произвольном разряде ячейки памяти 1.

Недостатком этого устройства являются ограниченные функциональные возможности .

Наиболее близким к предлагаемому является устройство, содержащее преобразователь контрольных символов в вектор компенсации дефектов и компенсатор дефектов ГЗ Недостатком этого устройства является то, что при использовании его для компенсации произвольных дефектов в блоках, объединяющих несколько разрядов памяти, при числе дефектных

10 блоков более одного, число добавляемых к памяти контрольных разрядов существенно больше максимального числа дефектных разрядов в слое памяти, так что полное использование емкости

15 исправных элементов памяти недостижимо.

Указанные обстоятельства увеличивают аппаратурные затраты, снижают надежность и быстродействие устрой20ства.

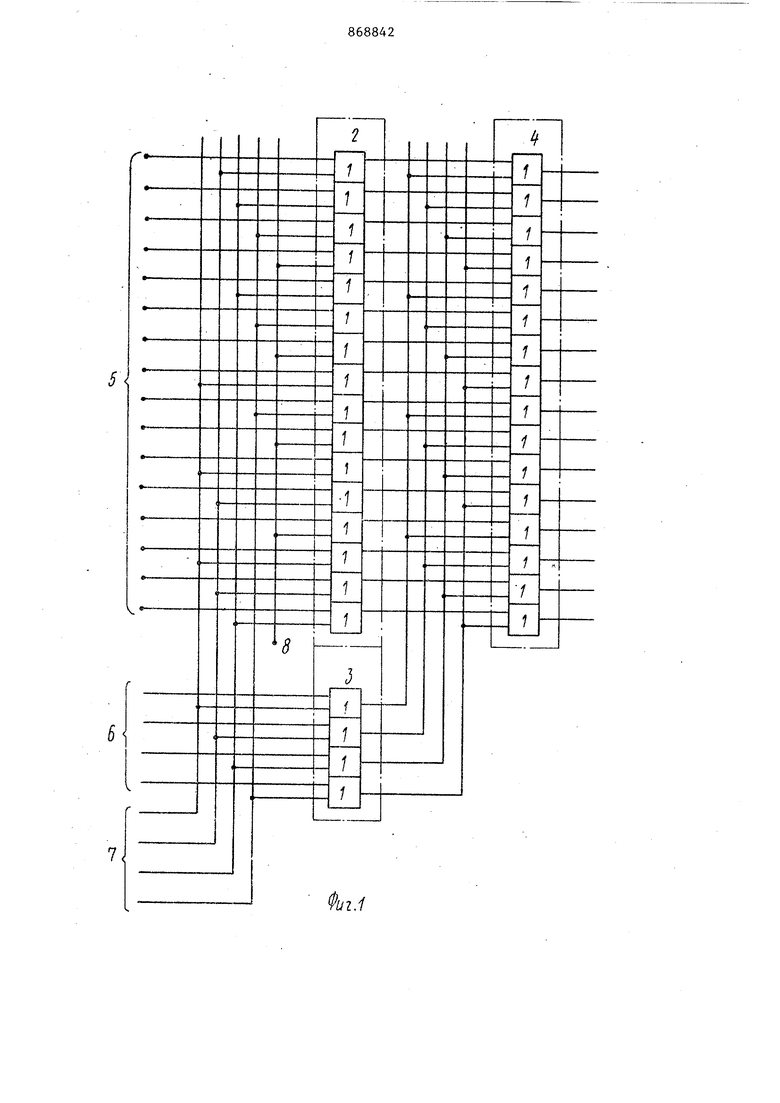

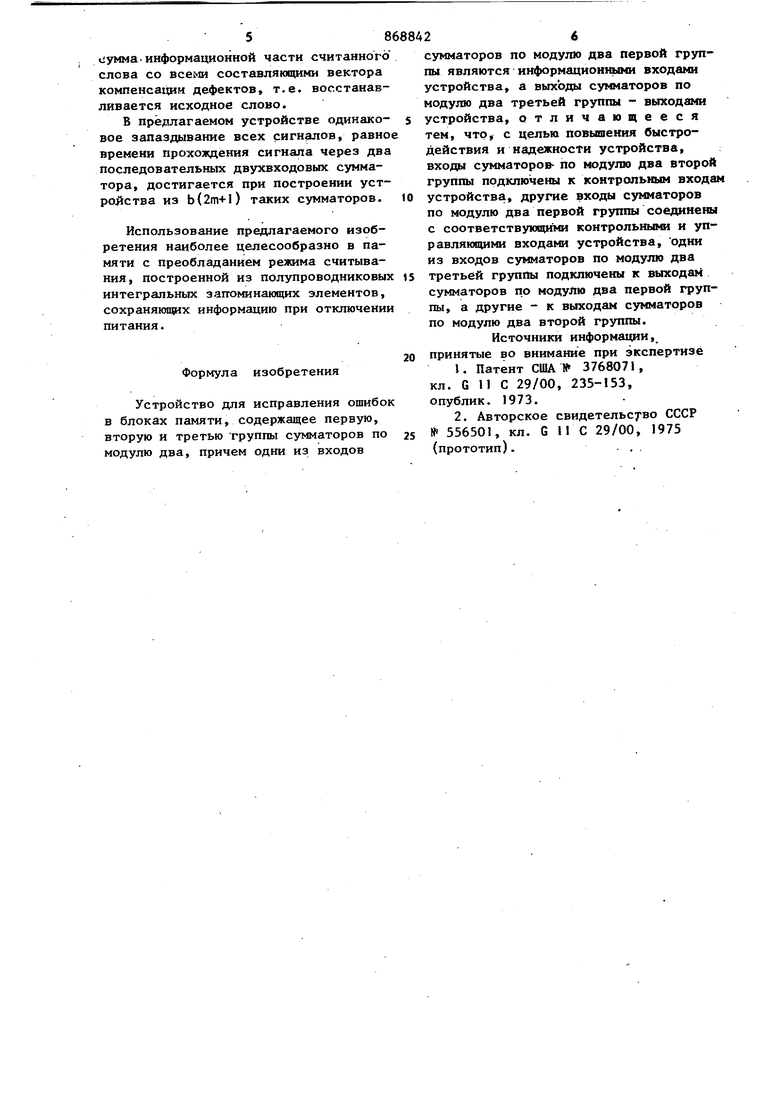

Цель изобретения - повьш1ение быстродействия и надежности устройства для случая, когда максимальное число дефектных блоков памяти в слове и число информационных блоков памяти m b, где число Ь+1 - простое. Поставленная цель достигается тем что в устройстве для исправления оши бок, в блоках памяти, содержащем первую, вторую и третью группы сумматоров по модулю два, причем одни из вх дов сумматоров по модулю два первой группы являются информационными входами устройства , а выхода сумматоров по модулю два третьей группы - в ходами устройства, входы сумматоров по модулю два второй группы подключе ны к контрольным входам устройства, .другие входы сумматоров по модулю дв (первой группы соединены с соответствующими контрольными и управляющим входами устройства, одни из входов сумматоров по модулю два третьей гру пы подключены к выходам сумматоров п модулю два первой группы, а другие к выходам сумматоров, по модулю два второй группы. На фиг. 1 изображена блок-схема устройства (для случая т b 4); на фиг. 2 - порождающая матрица векторов компенсации дефектов для этого устройства. Устройство содержит (фиг. 1) b2m +l) одинаковых двухвходовых сумматоров 1 по модулю два, которые разделень на первую группу 2, содержащую brn сумматоров 1 , вторую группу 3 из b сумматоров I и третью группу 4 из bm сумматоров 1. Каждый из сумматоров 1 групп 2 и 4 соответствует одно му информационному разряду памяти, каждый из сумматоров 1 группы 3 соот ветствует двум контрольным разрядам с одинаковыми порядковыми номерами в двух контрольных блоках памяти (на фиг. 1 не показаны). Одни из входов сумматоров I группы 2 являются инфор мационными входами устройства 5. t Входы сумматоров 1 группы 3 подключе ны к контрольным входам устройства 6 и 7. Другие входы сумматоров 1 группы 2 соединены со входами 7 и управлякицим входом 8, на который подается сигнал , о . Одни из входов сумматоров J группы 4 подключеИ) к выходам сумматоров 1 группы 2, а другие - к выходам сумматоров 1 группы 3. Действие устройства основано на ITOMi что устройство соответствует дв ичной матрице вида: I II ... I I 0 1Т Т, Н..... т„1 и . 4 де О и 1 - нулевая единичная (диатоальная) матрица порядка Ь, а Т. атрица такого жепорядка, получаемая з исходной матрицы размера ()xb. т- . Го О ... 0 -1-1 I J иклической перестановкой строк и отрасывания последней строки, которая е должна быть нулевой Если b и Ь+1 ростое число, любая пара подматриц Гит . . in Г1 01 ГО Ь4 1таИт,1И11 образует матрицу ранга 2Ь, т.е. матрицу, все 2 to строк и 2Ъ столбцов которой линейно независимы. Поэтому линейные комбинации (поразрядные суммы по модулю два) строк приведенной матрицы порождают все векторы,, необходимые для компенсации произвольных дефектов в любых двух изт+2 -Ъ-разрядных блоков памяти. Порождающая матрица векторов компенсации дефектов для устройства изображена на фиг. 2. При записи информации в блоки памяти для согласования с дефектами, к исхддному слову, содержащему нули в контрольных разрядах, поразрядно добавляется вектор компенсации дефектов , представленный суммой определенных строк матрицы. Задачей предлагаемого , устройства является восстановление исходного слова при считывании. Это Достигается путем восстановления вектора компенсации дефектов по содержанию контрольных разрядов и поразрядного сложения его с Информационной ; . частью считанного слова; контрольным блокам памяти соответствуют две последние подматрицы (на фиг. 2 отделены вертикальной линией). Устройство работает следующим образом. Двоичные сигналы, считанные с информационных и контрольных разрядов памяти, поступают на входы устройства 5, 6 и 7. На выходах сумматоров 1 группы 2 образуется поразрядная сумма информационных частей считанного из памяти слова и составляющих вектора компенсации дефектов из нижней половины матрицы. В сумматорах 1 третьей группы 4 к этой сумме добавляется поразрядная сумма составляющих вектора компенсации дефектов из верхней половины матрицы. В результате на выходах устройства образуется поразрядная информационной части считанного слова со всеми составляющими вектора KOMneHcaiQiM дефектов, т.е. восстанавливается исходное слово. В предлагаемом устройстве одинаковое запаздывание всех сигналов, равно времени прохождения сигнала через два последовательных двухвходовых сумматора, достигается при построении устройства из b{2m+l) таких сумматоров. Использование предлагаемого изобретения наиболее целесообразно в памяти с преобладанием режима считывания, построенной из полупроводниковых интегральных запоминающих элементов, сохраняклщх информацию при отключении питания. Формула изобретения Устройство для исправления ошибок в блоках памяти, содержащее первую, вторую и третью группы сумматоров по модулю два, причем одни из входов сумматоров по модулю два первой груп- пы являются информационными входами устройства, а выходы сумматоров по модулю два третьей группы - выходами устройства, отличающееся тем, что, с целью повышения быстродействия и надежности устройства, ; входы сумматоров- по модулю два второй группы подключены к контрольным входам устройства, другие входы сумматоров по модулю два первой группы соединены с соответствующими контрольными и управляющими входами устройства, одни из входов сумматоров по модулю два третьей группы подключены к выходам сумматоров по модулю два первой группы, а другие - к выходам сумматоров по модулю два второй группы. Источники информации, принятые во внимание при экспертизе 1.Патент США № 3768071, кл. G 11 С 29/00, 235-153, опублик. 1973. 2.Авторское свидетельство СССР № 556501, кл. G ПС 29/00, 1975 (прототип).. , ,

(

Авторы

Даты

1981-09-30—Публикация

1979-01-26—Подача