Изобретение отводится к области контрольно-измерительной техники и может быть использовано для оценки технического состояния широкого клас са динамических систем и электронных приборов. Известно устройство для контроля запаса эффективности динамических систем, содержащее двоичные и реверсивный счетчики, сумматор, шифратор, ключи управления, триггеры 1}. Это устройство позволяет на базе метода статистических испытаний определить запас эффективности системы, выраженный в виде определенной оценки, учитывающий вес каждого парс1метра из контролируемой совокупности. Однако такие устройства не анализируют полу ченный результат с целью прогнозирования техническозго состояния систил. Из известных устройств такого типа наиболее близким по технической сущнос-ги к изобретению является устройство 2 . Это устройство содержит аналого-цифровой переобразователь, дешифратор, реверсивный счетчик, циф ровой квадратор, первый логический блок, первый суммирукидий счетчик, вход которого соединен с выходом пер вого элемента ИЛИ, а первый выход - с первым входом элемента И, второй вход которого подключён к выходу первого триггера; дифференцирующий блок одним из выходом соединен с аналогоцифровым преобразователем, а другой - с блоком управления. Дифференцирующий блок предназначен для выделения участков стационарности контролируемого процесса, на которых проводится вычисление оценки дисперсии и последующее прогнозирование ее изменения. Од-, нако при определении участков стационарности с помощью дифференцирующего блока возникают погрешности, которые объясняются наличием в структуре контролируемого процесса x(t) случайной составляющий x(t). Так, изменение этой составляющей и изменение математического ожидания mx(t) может привести к тому, что производная сигнала будет равна нулю, хотя на самом деле процесс нестационарен по mH(t). Этот недостаток усугубляется наличием конечного значения порога чувствительности, устанавливаемым в дифференцирующем блоке на значения производной. Кроме того, изменение x(t) при mx(t) const приводит к тому, что производная сигнала не будет равна нулю. Продолжительность участков

етационарности определяемых с помощью дифференцирующего блока, при этом может быть недостаточной для проведения анализа, например, при наличии в структуре процесса высокочастотной составляющей, что ограничивает оЬйасть применения устройства в целях оценки технического состояния широкого класса динамических систем.

. Устройство является сложным вследствие наличия в нем решающих узлов, выполненных по двойной схеме преобразования, как цифрового, так и аналогового, что приводит к усложнению управления процессами вычислений. Использование в известном устройстве второго реверсивного счетчика по своим функциональным возможностям требует сложного управления вычислительными операциями при оригинальности выполнения реверсивного счетчика и регистрирующего устройства, что противоречит требованиям максимального использования в сложных устройствам схем типовых узлов. Кроме того, устройство содержит блок памяти, наличие которого обусловлено требованием предварительного центрирования стационарного случайного процесса при его анализе, это снижает оперативность обработки контролируемого сигнала.

Цель изобретейия - повышение точности прогнозирования и расширение области применения устройства.

Поставленная цель достигается тем, что в устройство для прогоновирования постепенных отказов, содержащее аналого-цифровой преобразователь, дешифратор, реверсивный счетчик, цифровой квадратор, первый логический блок, первый суммирующий счетчик, регистратор, два триггера, элементы ИЛИ и второй суммирующий счетчик, вход которого соединен с выходов первого элемента ИЛИ, а первый выход - с первым входом элемента И, второй вход которого подключен к выходу первого триггера, введены .сумматор и узел дискретной фильтрации, вход которого соединен с первым выходом аналогоцифрового преобразователя, а выходы - с первыми входами первого логического блока, подключенного первым и вторым выходами к первому и второму входам аналого-цифрового преобразователя соофвётственно, третьим и четвертым выходами - к первому и второму входам реверсивного счетчика соответственно, а вторым входом - к выходу пер:вого триггера, первый вход которого непосредственно, а второй вход через второй элемент ИЛИ соединены сйот ёетст вённо бО вторым и третьим выходами второго суммирующего счетчика, подключенного четвертыми выходами через дешифратор к первым входам и пёрвогЪ еуммирующего счетчШ а и к йёрвйм входам третьего и четвертого элементов ИЛИ, вторые входы которых соединены с первым входо. пятого элемента ИЛИ, вторым входом суммирующего счетчика и с первым выходом второго триггера, подсоединенного вторым выходом к первому входу первого элемента ИЛИ, первым входом к первому управляющему входу устройства, а вторым входом - ко второму управляющему входу устройства и ко второму входу второго элемента ИЛИ. Выходы реверсивного счетчика через последовательно соединенные цифровой квадратор, первый суммирующий счетчик и сумматор подключены ко входам регистратора, третий вход через пятый элемент ИЛИ - к пятому выходу второго суммирующего счетчика, а четвёртый вход - ко второму выходу аналого-цифрового преобразователя, третий вход и выход которого соединены с первым выходом второго суммирующег счетчика и вторым входом первого элемента ИЛИ соответственно. Третьи входы сумматора и первого суммирующего счетчика подключены к выходам третьего и четвертого элементов ИЛИ соответственно, а выход элемента И соединен со вторым входом дешифратора.

Узел дискретной фильтрации содержит второй логический блок, соединенный выходами с выходами узла, а входами непосредственно и через шесть расширителей импульсов - с соответствующими выходами третьего, четвертого и пятого триггеров, счетный вхо третьего триггера подключен ко входу узла, а выходы - к счетным входам четвертого и пятого триггеров.

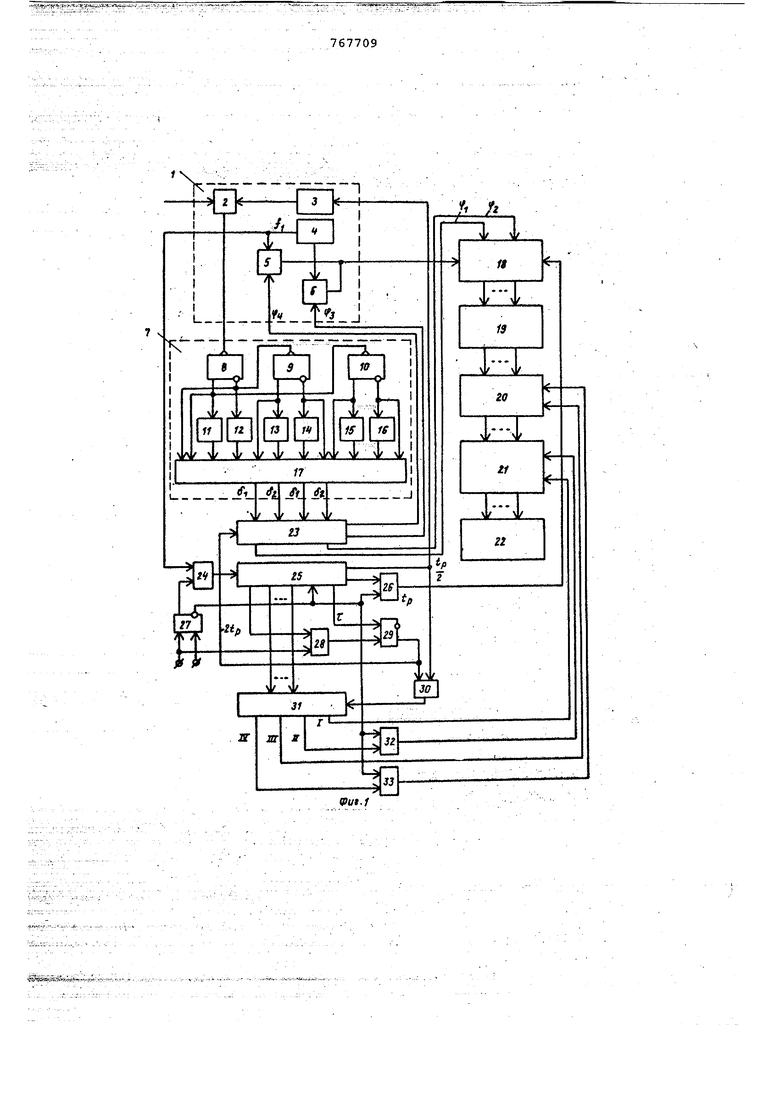

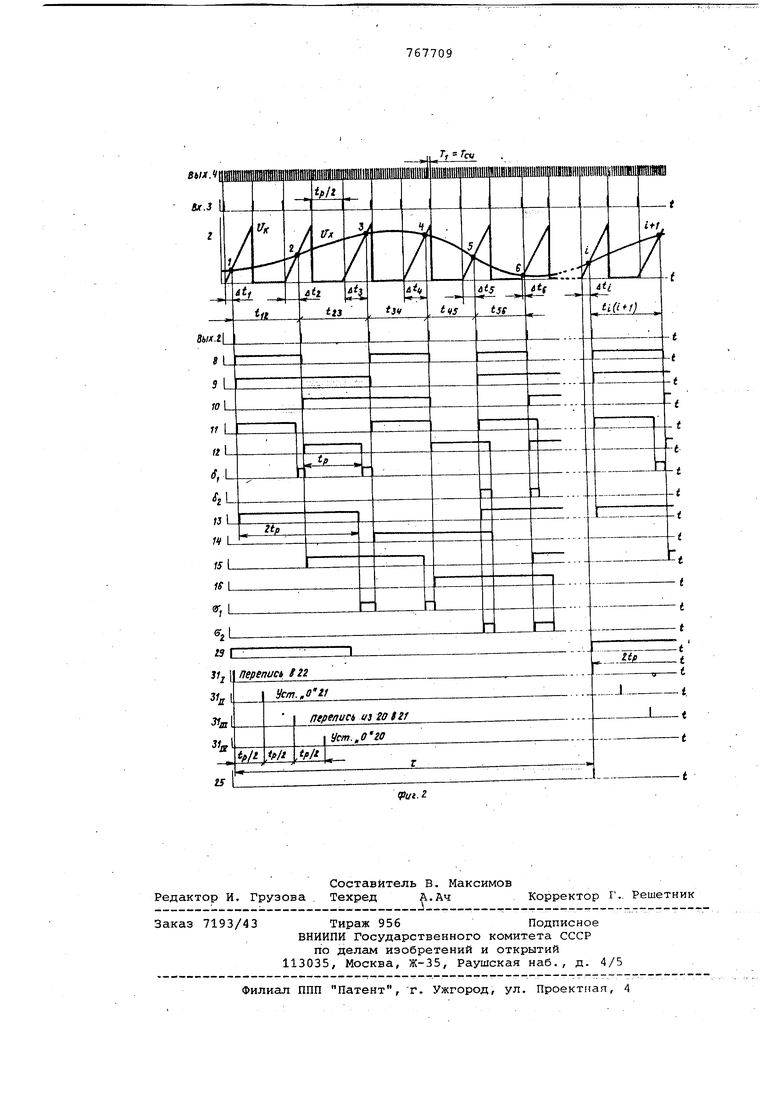

На фиг. 1 изображена функциональная схема предлагаемого устройства; на фиг. 2 - временные диаграммы его работы.

Устройство содержит аналого-цифровой квадратор 1, состоящий из нульоргана 2, генератора 3 пилообразного напряжения, генератора 4 счетных импульсов и ключей 5, 6. Первый выход аналого-цифрового преобразователя 1 соединен со входом узла 7 дискретной фильтрации, состоящим из счетных триггеров 8, 9, 10, расширителей 1116 импульсов и логического блока 17. Второй выход аналого-цифрового преобразователя 1 связан с четвертым вхдом реверсивного счетчика 18, выход которого через последовательно соединенные цифровой квадратор 19, первый суммирующий счетчик 20 и сумматор 21 подключены ко входам регистратора 22. Первый и второй входы реверсивного счетчика 18 соединены соответственно с третьим и четвертым выходами первого логического блока 23. Третий выход аналого-цифрового преобразователя 1 связан со вторым входом первого элемента ИЛИ 24, выход которого .подключен к первому входу второго суммирующего счетчика 25. Второй вход суммирующего счетчика 25

соединен с первыми входом и выходом пятого элемента ИЛИ 26 и второго триггера 27 соответственно, а третий .выход через второй элемент ИЛИ 28 - с первым триггером 29, выход которйго подключен через элемент И 30 на второй вход дешифратора 31. Соответствующие выходы дешифратора 31 соединены с первыми входами третьего 32 и четвертого 33 элементов ИЛИ.

Работает устройство следующим образом.,

Контролируемый параметр х(t) в виде напряжения Ux{t) (фиг. 2) поступает Н4 вход аналого-цифрового преобразователя 1, в качестве которого применен преобразователь циклического действия с промежуточным преобразованием напряжения во временной интервал. Преобразуемое напряжение их подается на вход нуль-органа 2, где оно сравнивается с линейно-возрастающим напряжением UK, поступающим с генератора 3 пилообразного напряжения. Период пилообразного напряжения UK засинхронйзирован через суммирующий счетчик 25с периодом счетных импульсов, генерируемых генератором 4 счетных импульсов. Приме.нение суммирующего счетчика 25 позволяет получить ряд управляющих импульсов, синхроннных со счетными импульсами.

В момент выполнения равенства и X и на выходе нуль-органа 2 появляется короткий .импульс, который поступает на счетный вход триггера 8 в узле 7 дискретной фильтрации. В этот момент счетный триггер 8 изменяет свое состояние. Прямой и инверсный выходы триггера 8 соединены соответственно с расширителями 11 и 12, на выходе которых формируются импульсы длительностью, равной длительности периода tp пилообразного напряжения и. Зная моменты времени срабатывания нуль-органа 2 t , tj , . . . , ti. в каждом цикле преобразования и соответственно отрезки времени , 132 . t(i,-tl)t (фиг. 2) и длительность периода tp, с помощью логического блока 17 можно выделить разность первого порядка, контролируемого нестационарного случайного процесса х(t)

VW

(ti;)x( ) -. x(ft) Krf ,;

где cr,-ikti,+i - Д Ч t(tn) - tp, i 1 , 2, . , . , n ; ) - значение длительности вреМя-и1у1пульсного сигнала, пропорциональное значению разности первого порядка UK в точке Г;

К - крутизна развертки; ,At - интервал времени между началом цикла преобразования и моментом Ux U. Аналогичным путем выделяется время-импульсные сигналы, соответствуюдие попарной алгебраической сумме двух соседних разностей первого поряд а с помощью схем: счетных тригреров 9, 10, логического блока 17 и оасширителей 13-16, на выходе которых формируются импульсы, длительностью равной 2t .

rf cyg (itu, -Att ) +

+ (&4-&t|.., ) чы)а-1) - 2tp.,

Если выходы расширителей 11-16 обозначить в зна 1ениях логических

функций )Ь,,(b,j ,. . . Jbjj, причем присутствие сигнала на выходе расширителя соответствует логической 1,..отсутствие - логическому О, то алгоритм работы логического блока 17 записывается с помощью уравнений алгебры-логики в следующем виде:

оИ5

d;.cr--jb,p,,

0

./ь..

to, -«-Id |bj-jb |b5jb,

4-l PVib4 /b5br

5

, cf/j - соответственно положигдетельное и отрицательное значения попарной алгебраической суммы двух значений разности первого поРрядка.

Работа логического блока 17 в соответствии с приведенным алгоритмом прослеживается на временной диаграмме (фиг. 2).

5

С выхода узла 7 дискретной фильтрации импульсы,длительность которых соответствует положительной или отрицательной разности первого порядка и их алгебраической сумме, поступают 0 на вход логического блока 23. На выходе логического блока 23 формируются логические функции ,-j , , каждая из которых означает выполнение следующей операции: Ф - управление f Вычитанием реверсивного счетчика 18, 0 - управление сложением реверсивного счетчика 18,S5j - разрешение прохождения через ключ 6 импульсов частоты f,. 2 f с генератора 4 на счетный вход реверсивного счетчика 18,

0

Необходимость использования двои- ной частоты время-импульсного сигнала Ф, вызвана совпадением повремени слагаемых при вычитании разности вто:рого порядка реверсивным счетчиком; 18.

5

Логика получения управляющих сигнсшов 1 Pi с помощью логического блока 23 описывается следующим алго-, ритмом: -X :; - л л

- . сЯ,ЧЪ,,+ с,сС,

О

.

.,--,(3l6,

В nfibctecce вЕочислёния рсьзнбсти в рого порядка функции х (t) на выходе реверсивного счетчика 18 фбрмируетс Ttdfl вспомогательного случайного ста ционарного . процесса (ВССП), соответ ствующего в каждом цикле преобразованйя разности второго порядка НСП: (tL) )(4-, )к-, где Nj - число импульсов частоты f, заполняющих интервал време ни, соответствующий значению разности второго пЪряд ка в точке i ; Перед каждым циклом вычислений счетчик 18 устанавливается в нулевое сбстЪйниё импульсом с суммирующего счетчика 25 через элемент ИЛИ 26. STdT момент соответствует моменту за пуска генератора 3 в каждом цикле;.; прёдбЕ)азо вателя и моменту окончания анализа. Снимаемый с выхода счетчик 18 параллельный код за один цикл вычислений пропорционален значению слу чайной составляющей xi V(t.), предполагая, что на интервале СО,2t. где .ii, - интервал корреляции процесса, математическое ожидание mx(t апг1роксимир1 ется полиномом первой .степени. В соответствии с теорией конечных разностей можно записать, что (t) 0. ( С выхода счетчика 18 параллельный код поступает на цифровой квадратор 19, где образуется параллельный код сбответствующий квадрату, величины значенийВССП контролируемого параМетра с выхода квадратора 19 параллельный код приходит навход счетчика 20, в котором производится последовательное суммирование кодов за оп ределенное время t, равное длительности периода выборки (см. фиг. 2). За промежуток времени в счетчике 20 образуется двоичный код оценки дисперсии ВССП: ,1 (x,f , (j 1,2,.. .,m), . - j где n-ЧИСЛО циклов преобразования за промежуток временив ; т-ЧИСЛО расчетных интервалов выборки tr на реализации. При достижении периодом выборки расчетной величины на выходе дешиф .ратора 31 начинают формироваться короткие тактовые импульсы за время, равное длительности двух циклов преобразования (фиг. 2). Первым такто вым импульсом в регистрирующее уст.ройство 22 переписывается результат сравнения кодов, записанных в накопи тельном счетчике 20 и сумматоре 21. Втбрам тактовым импульсом через элемент ИЛИ 32 сумматор 21 устанавливается в нулевое состояние. Третьим тактовым импульсом код, записанный в накопительном, счетчике 20, переписывается в сумматор 21, четвертым тактовым импульсомчерез элемент ИЛИ 33 осуществляется сброс накопительного счетчика 20 в нулевое состояние. Таким образом, регистратор 22 регистрирует величину и знак разности оценок дисперсий ВССП, вычисленных на соседних промежутках времени t, что позволяет непосредственно провести прогнозирование отказа прибора, так как дисперсии процессов S(t) и x(t) связаны постоянной масштабной зависимостью на временных интервалах Т одинаковой длительности. Вланкирующий триггер 29 запрещает выдачу управляющих импульсов Ч, -а, с выхода логического блока 23 вовремя пёрвый двух циклов преобразования с момента начала дисперсионнозЬб анализа, поскольку первое значение разНосТи второго порядка появляется только в третьем цикле. Использование узла дискретной фильтра;ции в схеме предлагаемого устрбйства выгодно отличает его от указанного прототипа, так как повышается точность и достоверность прогнозирования изменения оценки дисперсии контролируемого процесса при достижении возможности проведения его оперативной непрерывной обработки. Точность прогнозирования определяется прежде всего статистической погрешностью вычисления оценки дисперсии и так называемой динамической ошибкой второго рода Х, связанной с изменением статистических характеристик исследуемого процесса в течение определенного значения периода сглаживания Т. Устройство приводит дисперсионный анализ на интервалах локальной стационарности, длительность которых определяется дифференцирующим блоком. При этом относительная ошибка в определении стациОйарности реализации может достигать 100%, что в дальнейшем пря вычислёнии оценки дисперсии определяет с щественный вес составляющей в f руктуре погрешности прогнозирова. 1Я. Использование узла дискретной ф.льтрации в схеме предлагаемого устройства позволяет привести контролируемый в общем случае нестационарный процесс к стационарному через разности второго порядка для .исключения влияния скорости изменёнй.я Математического ожидания на участке Тд 2..., В этом случае составляющая РП.К, . О и погрешность прогноза будет в основном Определяться составляющей gg.,.,, которая в свою Очередь зависит от принятого алгоритма вычисления - . оценки дисперсии, йнтЬрва.ла дискретизации процесса и длительности участка t, на кото аОмвьмисляется оценка Дисперсиии. Оптимальный выбор этих величин определяет погрешность вычисления оценки дисперсии на расчетном интервале . Наличие непрерывной простой линейной зависимости между значениями дисперсии исходного нестационарного процесса x(t) и вспомогательного x(t). т.е. Dc г 0.j, позволяет вести прогнозирование непосредственно по оценке дисперсии 5 вспомогательного стационарного процессах(t). Возможность непрерывного приведения нестационарного, по математическому ожиданию, случайного процесса к стационарному процессу, точная и оперативная обработка которого не представляет трудностей, позволяет расширить область применения устройства в целях оценки технического состояния широкого класса динамических систем и электронных приборов. Повсеместное использование в устройстве унифицированных цифровых узлов позволяет упростить устройство и применить стандартные микросхемы средней интеграции, выпускаемые отечественной промышленностью без приме нения дополнительных элементов, что повышает надежность работы устройст.ва-и облегчает его конструктивное ис пользование. Указанные положения подтверждены результатами исследований, полученны ,ми в процессе лабораторного макетиро вания устройства. Формула изобретения 1. Устройство для прогнозирования постепенных отказов, содержащее аналого-цифровой преобразователь, дешиф ратор, реверсивный счетчик, цифровой квадратор, первый логический блок, первый суммирующий счетчик, регистра тор, два триггера, элементы ИЛИ и вт рой суммирующий счетчик, вход которо го соединен с выходом первого элемен та ИЛИ, а первый выход - с первым входом элемента И, второй вход которого подключен к выходу первого триг гера, отличающееся тем, что, с целью повышения точности и ра ширения области применения устройства, оно содержит сумматор и узел дискретной фильтрации, вход которого соединен с первым выходом аналогоцифрового преобразователя, а выходы с первыми входами первого логического блока, подключенного первым и вто рым выходами к первому и второму вхо дам аналого-цифрового преобразовател соответственно, третьим, и четвертым выходами - к первому и второму входам С)еверсивнрго счетчика соответственно, а вторым йходом - к выходу первого триггера, первый вход которого непосредственно, а второй вход через второй элемент ИЛИ соединены соответственно со вторым и третьим выходами второго суммирующего счетчика, подключенного четвертыми выходами через дешифратор к первым входам сумматора и первого суммирующего счетчика И к первым входам третьего и четвертого элементов ИЛИ, вторые входы которых соединены с первым входом пятого элемента ИЛИ,вторым входом суммирующего счетчика и с первым выходом второго триггера, подсоединенного вторым выходом к.первому входу первого элемента ИЛИ, первым входбм - к первому управляющему входу устройства, а вторым входом - ко второму управляющему входу устройства и ко второму входу второго элемента ИЛИ, выходы реверсивного счетчика через последовательно соединенные цифровой квадратор, первый суммирующий счетчик и сумма- тор подключены ко входам регистратора, третий вход через пятый элемент ИЛИ - к пятому выходу второго суммирующего счетчика, а четвертый вход - ко второму выходу аналого-цифрового преобразователя, третьи вход и выход которого соединены с первым выходом второго суммирующего счетчика и вторым входом первого элемента ИЛИ соответственно, причем третьи входы сумматора и первого суммирующего счетчика подключены к выходам третьего и четвертого элементов ИЛИ соответственно, а выход элемента И соединен со вторым входом дешифратора, 2. Устройство по п. 1, отличающееся тем, что узел дискретной фильтраций содержит второй логический блок, соедине1 ный выходами с выходами узла, а входами непосредственно и через шесть расширителей импульсов - с соответствующими выходами третьего, четвертого и пятого триггеров, счетный вход третьего триггера подключен ко входу узла, а выходы - к счетным входам четвертого и пятого триггеров. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 429418, кл. G 05 В 23/02, 1972. 2.Авторское свидетельство СССР 428361, кл. G 05 В 23/02, 1971.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для ОПРЕДЕЛЕНИЯ ДИСПЕРСИИ РАЗЛ1АХОВ И ПЕРИОДОВ СЛУЧАЙНОГО ПРОЦЕССА | 1973 |

|

SU383058A1 |

| Адаптивный кодирующий преобразователь стационарных случайных процессов | 1980 |

|

SU960846A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР КАЧЕСТВА ПАРАМЕТРОВ ЭЛЕКТРИЧЕСКОЙ ЭНЕРГИИ | 1993 |

|

RU2096788C1 |

| Аналого-цифровой квадратор | 1983 |

|

SU1120374A1 |

| Устройство для определения дисперсии длительностей выбросов случайных процессов | 1976 |

|

SU650083A1 |

| УСТРОЙСТВО ДЛЯ ПРОГНОЗИРОВАНИЯ ПОСТЕПЕННЫХ ОТКАЗОВ ЭЛЕКТРОННЫХ ПРИБОРОВ | 1971 |

|

SU428361A1 |

| Адаптивное устройство для передачи информации | 1984 |

|

SU1244693A1 |

| Устройство для автоподстройки частоты | 1988 |

|

SU1653159A1 |

| Адаптивный статистический анализатор | 1974 |

|

SU642714A1 |

| Устройство для измерения коэффициента пульсаций постоянного напряжения | 1989 |

|

SU1742644A1 |

Авторы

Даты

1980-09-30—Публикация

1978-05-04—Подача