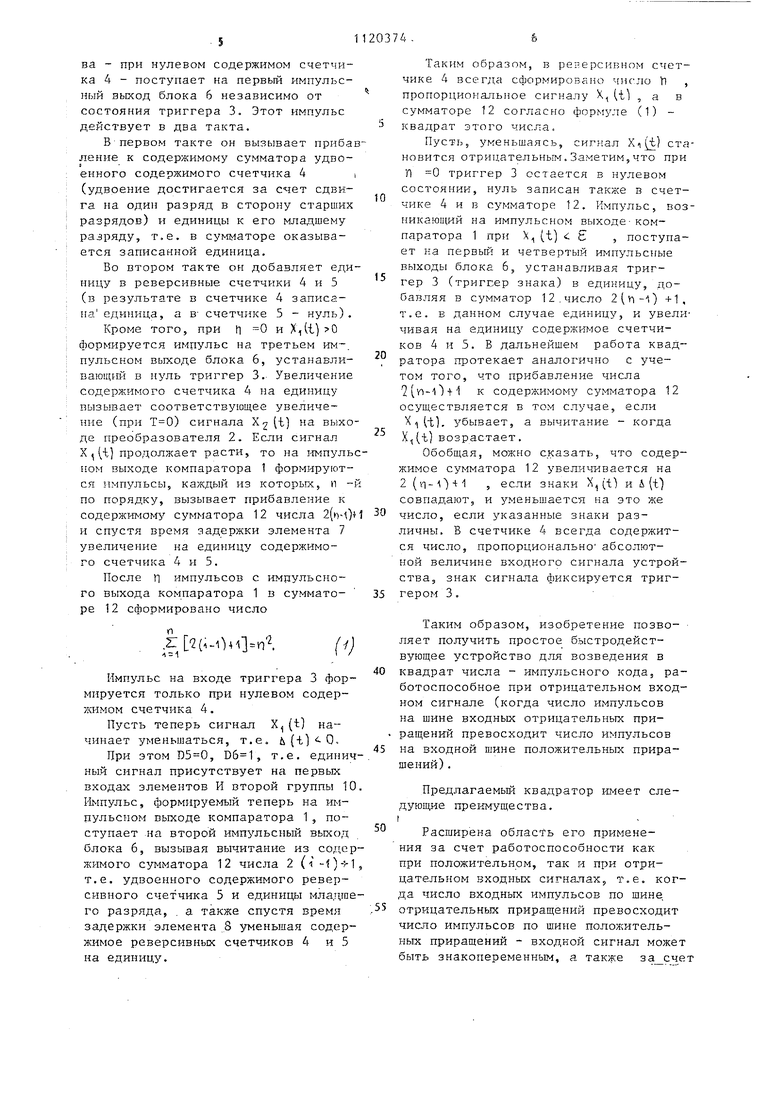

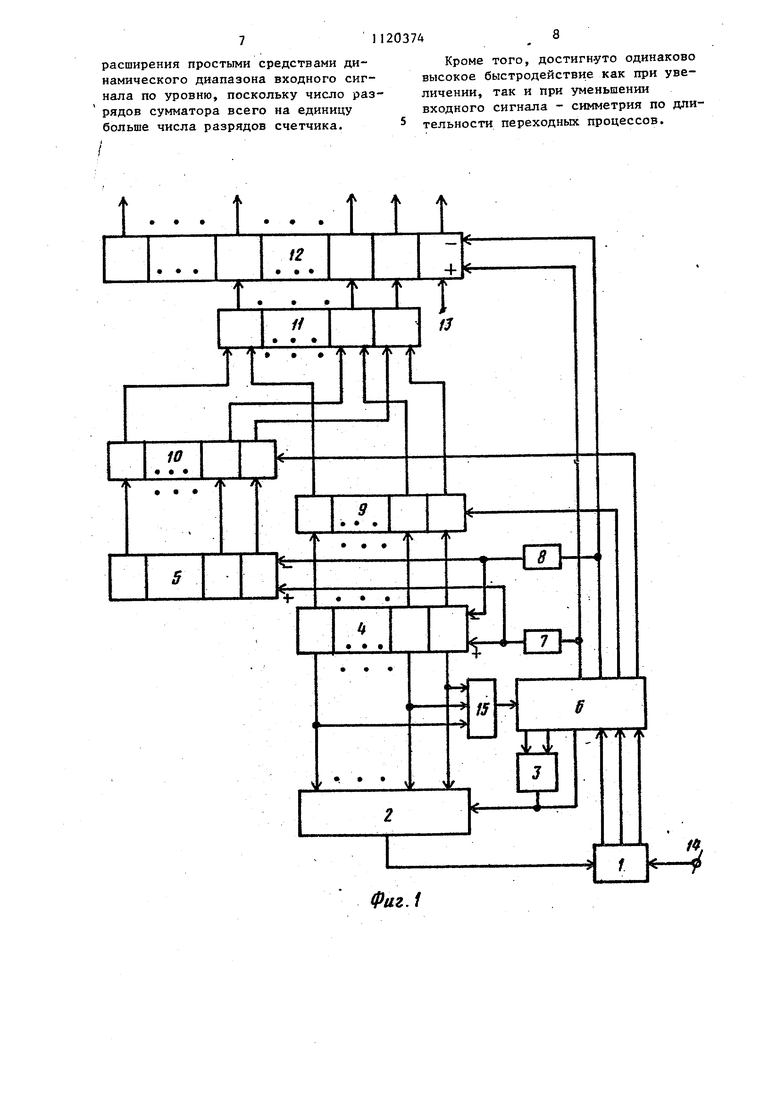

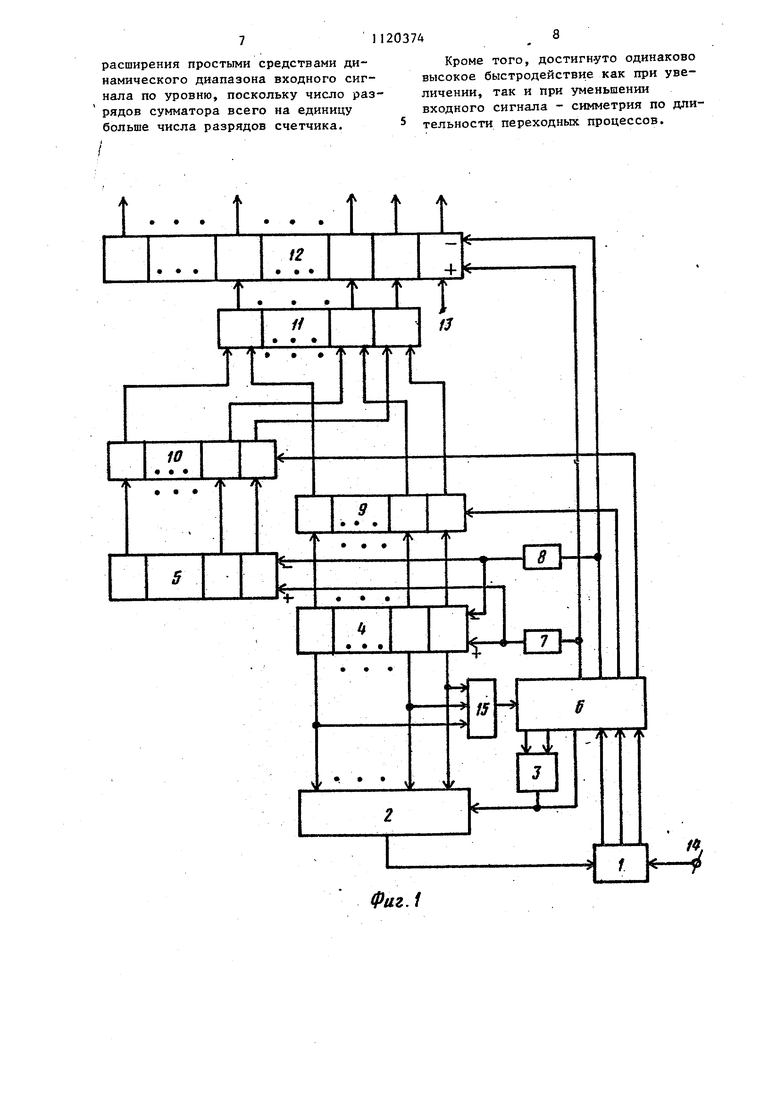

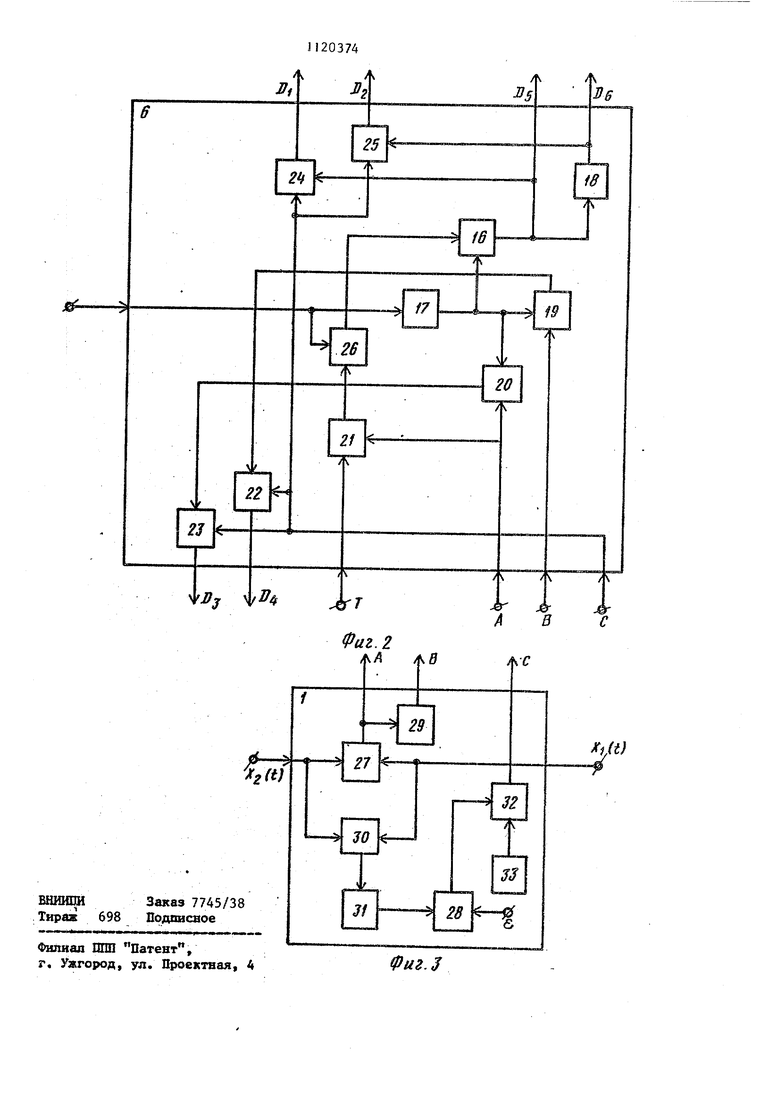

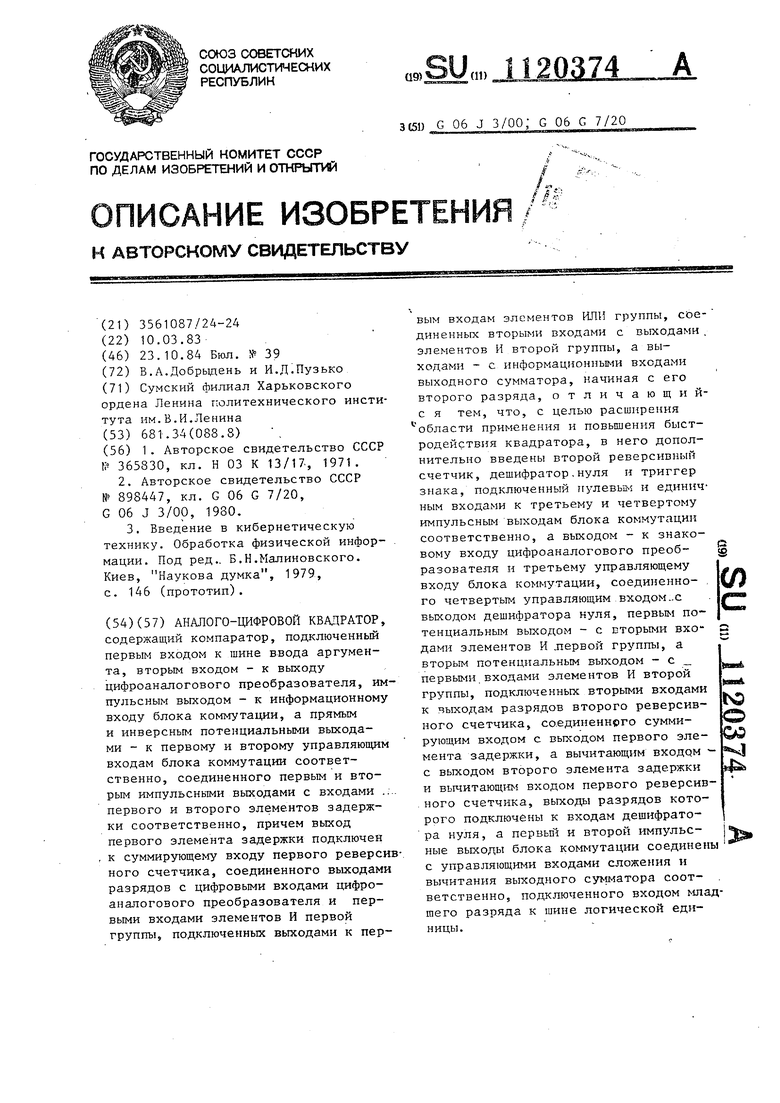

Изобретение относится к автомати ке и вычислительной технике иможет быть использовано в составе специализированных вычислительных и управляющих устройств и систем. Известен аналого-цифровой квадратор, содержащий генератор импульсов распределитель импульсов, элементы И и liTIH, регистры, сумматор, цифроаналоговый преобразователь и компаратор l . : Известен также аналого-цифровой квадратор, содержащий генератор им: пульсов-5 делители частоть, распределитель импульсов, генератор линейно изменяющегося напряжения, }1ульорган, ключи, элемент ИЛИ и счет: ЧИК 2j . Недостатком квадраторов является пониженное быстродействие. : Наиболее близким к изобретению является аналого-цифровой квадратор :содержащий компаратор, подключенный пер1зьи входом к шине ввода аргумента, вторым входом - к выходу цифроаналогового преобразователя, импуль ным выходом - к информационному вхо ду блока коммутации, а прямым и инверспым потенциальными выходами - к первому и второму управляющим входам блока коммутации соответственно, со диненного первым и вторым импульсны ми выходами с входами первого и вто рого элементов задержки соответстве но, причем выход первого элемента задержки подключен к суммирующему вх ду первого реверсивного счетчика, соединенного выходами разрядов с цифровыми входами цифроаналогового преобразователя и первыми входами элементов И первой группы, подклюtieHHbix выходами к первым входам эле ментов 1-1ПР группы, соединенных вторыми входами с вькодами элементов И второй групы, а выходами - с ин .формацнонными входами выходного сум kaTopa, начиная с его второго разряд причем его первый разряд,подключен к первому импульсному выходу блока коммутации и вторым входам элементов И первой группы, а элементы И второй группы соединены первыми входами с инверсными выходами разрядов первого реверсивного счетчика, -а вто рыми входами - с. выходом втопо- , го элемента задержки, подклгоченпого входом к вьrчит;lшtt e входу первого реверсивного счетчика з 74г 1едостатком известного устройства является ограниченная область применения из-за невозмоясности работы со зьакоперемениыми входными сигналами и сигналами большого уровня, а также noHi-DseFiHoe быстродействие при умепыие}И-1и входного сигнала по абсолк)Т ной величине из-за того. что в этом случае |} Ормирование нового со/держимого сумматора начинается спустя время задержки импульса элементом задержки. Цель изобретения -- расширение области применения и позьвиение быстродействия квадратора. Поставленная цель-достигается тем. что в аналого-цифровой квадратор, содержащий компаратор, подключенный первым входом к шине ввода аргумента, BTOpuLM входом - к выходу цифроаналогового преобразователя, импульсным выходом - к ин(Ьорма1.р- омному входу блока коммутации, а прямым и инверсным потенциалыалги выходами - к первому и BTOpoNfy управляющим входам блока коммутации соответствень о, соединенного первьм и зторым импульсными выходами с входами первого и второго элементоз задержки соответственно, причем выход пер)зого элемента задержки подключен к суммирующему входу .первого реверсивного счетчика, соединенного выходами разрядов с цифроБьими входами цифроан,алогового преобразователя и первьми входами элементов И первой группы, подключенных выхода№-1 к первым входам элементов ИЛИ группы,, соединенных вторыми входами с выходами элементов И второй группы, а зьшодами с информационными входами выходного сумматора, начиная с его второго раз- ряда, дополнительно введены второй реверсивный счетчик, дешифратор нуля и триггер знака, подключенный нулевым и единичны;-- входами к третье гу и четвертому импульсиьгм выходам блока коммутации соответственно, а выходом - к знаковому входу цифроаналогового преобразователя и третьему управляющему входу .блока коммутации., соединенкого четвертью управляющим входом с выходом дешифратора нуля, первым потенциальным вьходом - с вторыми входами элементов И первой группы5 а вторьп.1 потенциальным выходом - с первыми вхоами .элементов И второй группы, подклгочен ых вторыми входами, к выходам разрядов второго реверсивного счетчика, соединенного суммирующим входо с выходом первого элемента задержки, а вычитающим входом - с выходом второго элемента задержки и вычи-паюищм входом парного реверсивного счет чика, выходы разрядов которого подключены к входам дешифратора нуля, а первый и второй импульсные выходы блока коммутации соединены с управляющими входами сложения и вычитания выходного сумматора соответственно, подключенного входом младшего разряда к шине логической единицы. На фиг.1 изображена блок-схема предлагаемого аналого-цифрового квадратора, на фиг. 2 и 3 - aapiiauты выполнения функциональных схем блока коммутации и компаратора соответственно. Аналого-цифровой квадратор (фиг.1 содержит компаратор 1, цифроаналоговый преобразователь 2, триггер 3 зна ка, первый и второй реверсивные счетчики 4 и 5, блок 6 -коммутации, первый и второй элементы 7 к 8 заде;р ки, первую и вторую группы 9 и 10 элементов И, группу 11 элементов ИЛИ выходной сумматор 12, шину 13 логической единипдз, шину 14 ввода аргумента и дешифратор 15 нуля (который может быть выполнен на элементе ИЛИ или на элементе И-НЕ). Блок коммутации может быть выполнен, например, содержащим элементы ИЛИ16, НЕ 17 и 18, И 19-21, ключи 22-25 и элемент 26 равнозначности (фиг,2), Компаратор может содержать схему 27 сравнения, пороговую схему 28, элемент НЕ 29, вычитающий узел 30, узел 31, выделения модуля, ключ 32 и генератор 33 импульсов (фиг.З), Компаратор 1 имеет два.аналоговых входа: на первьм вход с тины 14 подается аргумент Х (t) , а на второй вход - компенсирующий сигнал X 1 (t) с выхода преобразователя 2, Если входной сигнал больше компенсирующего, то , .(где А и В сигналы на прямом и инверсном потенциальных выходах компаратора 1 ), На импульсном вькоде С компаратора последовательность импульсов формируется только .в том случае, когда модуль разности .& .входного и компен74&сирующего напряжеь:ии превышает заданное пороговое значение ЦифроамалоговыГ преобразователь 2 имеет лннейную характеристику, знак его выходного напряжения определяется состоянием выходного сигнала Т триггера (плюс - при нулевом и минус - при единичном). Вькодные сигналы блока б являются попаг-но-инверсными, обозначая D1 --D4 состояния первого, второго, третьего и четвертого импульсных выходов и D5 и D6 состояния первого и второгопотенциальных выходов соотв(тственно, имеем , D3-DA,,D5-D6 (причем для импульсных выходов это условие выполняется только при поступлении очередного Илчпульса на информационный вход блока коммутации если таких импульсов нет, то D1.-D2-D3 D4()). Блок 6 предсталяет собой комбинационную схему, огфеделяемую таблицей состояния входы-вы.ходы.5 которая для случая использования в качестве дешифратора 15 нуля элемента ИЛИ (сигнал а вь1ходе которого равен , только в том спучае; когда код и счетчика 4 отличен от нуля) имеет .ви,д: Устройство работает следующим обазом. В исходном состоянии суътатор 12 счетчик 4 обнулены, а в счетчике записано шсло (где К - число разрядов счетчика.) , Пусть, для определенности, Х,(4,)0 При этом согласно таблице D5 1 , т.е. на вторьк входах элементов И группы 9 присутствует едипичньш сигнал. Когда величина / Х {t) достигает значения , вырабатывается кмпульс на выходе С компаратора, котог-)ый в этом состоянии устройства при нулевом содержимом счетчика 4 - поступает на первый импульсный выход блока 6 независимо от состояния триггера 3. Этот импульс действует в два такта.

В первом такте он вызывает прибавление к содержимому сумматора удвоенного содержимого счетчика 4 i (удвоение достигается за счет сдвига па одип разряд в сторону старших разрядов) и единицы к его младшему разряду, т.е. в сумматоре оказывается записанной единица.

Во втором такте он добавляет единицу в реверсивные счетчики 4 и 5 (в результате в счетчике 4 записана единица, а в- счетчике 5 - нуль).

Кроме того, при П 0 и Xi(t) 0 формируется импульс на третьем им. пульсном выходе блока 6, устанавливающий в нуль триггер 3. Увеличение содерлсимого счетчика 4 на единицу вызывает соответствующее увеличение (при ) сигнала X2(t) на выходе преобразователя 2. Если сигнал X , (i) продолжает расти, то на импульсном выходе компаратора 1 формируются импульсы, каждый из которых, п -и по порядку, вызывает прибавление к содержш-гаму сумматора 12 числа 2(ti-i) и спустя время задержки элемента 7 увеличение на единицу содержимого счетчика 4 и 5.

После п импульсов с импульсного выхода компаратора 1 в сумматоре 12 сформировано число

f 2(.-Ои п.

()

Импульс на входе триггера 3 формируется только при пулевом содержимом счетчика 4,

Пусть теперь сигнал Х(t начинает уменьшаться, т.е. ii {-t 0.

При этом , , т.е. единичный сигнал присутствует на первых входах элементов И второй группы 10. 1-1мпульс, формируемый теперь на импульсном выходе компаратора 1 , поступает на второй импульсный выход блока 6, вызывая вычитание из содерлснмого сумматора 12 числа 2 (i-t),, т.е. удвоенного содержимого реверсивного счетчика 5 и единицы младгпего разряда, . а также спустя время задержки элемента ,8 уменьшая содержимое реверсивных счетчиков 4 и 5 на единицу.

Таким образом, в ререрсивном счетчике 4 всегда сформироБано число Y , пропорциональное сигналу X, (t ., а в сумматоре 12 согласно формуле (1) квадрат этого числа.

Пусть, уменьшаясь, сигнал Xi(i) становится отрицательным.Заметим,что при Л 0 триггер 3 остается в нулевом состоянии, нуль записан также в счетчике 4 и в сумматоре 12. Импульс, возЕ икаю1дий на импульсном выходе-компаратора 1 при X, (t) : , поступает ка первый и четвертый импульсные выходы блока 6, устанавливая триггер 3 (триггер знака) в единицу, добавляя в сумматор 1 2 . число 2(vi-i) +1, т.е. в данном случае единицу, и увеличивая на единицу содержимое счетчиков 4 и 5. В дальнейшем работа квадратора протекает аналогично с учетом того, что прибавление числа 7 n-Of1 к содержимому сумматора 12 осуществляется в том случае, если чН). убывает, а вычитание - когда X,(t) возрастает.

Обобщая, можно сказать, что содержимое сумматора 12 увеличивается на 2 (11-(41 , если знаки ,(1;) и & (t) совпадают, и уменьшается на это же

число, если указанные знаки различны. В счетчике 4 всегда содержится число, пропорционально абсолютной величине входного сигнала устройства, знак сигнала фиксируется триггером 3.

Таким образом, изобретение позволяет получить простое быстродействующее устройство для возведения в

квадрат числа - импульсного кода, работоспособное при отрицательном входном сигнале (когда число импульсов на шине входных отрицательных приращений превосходит число импульсов

на входной шине положительных прирашений),

Предлагаемый квадратор имеет следующие преимущества. I

Расширена область его применения за счет работоспособности как при положительном, так и при отрицательном входных сигналах, т.е. когда число входных импульсов по шине,

отрицательных приращений превосходит число импульсов по шине положительных приращений - входной сигнал может быть знакопеременным, а также за счет расширения простыми средствами динамического диапазона входного сигнала по уровню, поскольку число разрядов сумматора всего на единицу больше числа разрядов счетчика.5 Кроме того, достигнуто одинаково высокое быстродействие как при увеличении, так и при уменьшении входного сигнала - симметрия по длительности переходных процессов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для коррекции нелинейности | 1982 |

|

SU1056228A1 |

| Вероятностный интегрирующий преобразователь аналог-код | 1987 |

|

SU1441476A1 |

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| Следящий аналого-цифровой преобразователь | 1990 |

|

SU1802413A1 |

| Устройство для интегрирования функций | 1984 |

|

SU1242993A1 |

| Устройство для определения максимальной гармоники спектра Уолша | 1984 |

|

SU1211751A1 |

| Дискретно-цифровой электропривод | 1985 |

|

SU1350800A1 |

| УСТРОЙСТВО ДЛЯ РЕГУЛИРОВАНИЯ КОЛЕБАНИЙ | 1991 |

|

RU2024912C1 |

| Генератор периодических колебаний инфразвуковых частот с автоматической калибровкой | 1987 |

|

SU1497722A1 |

| Устройство для интегрирования функций | 1982 |

|

SU1070570A1 |

АНАЛОГО-ЦИФРОВОЙ КВАДРАТОР, содержащий компаратор, подключенный первым входом к шине ввода аргумента, вторым входом - к выходу цифроаналогового преобразователя, импульсным выходом - к информационному входу блока коммутации, а прямым и инверсным потенциальными выходами - к первому и второму управляющим входам блока коммутации соответственно, соединенного первым и вторым импульсными выходами с входами .... первого и второго элементов задержки соответственно, причем выход первого элемента задержки подключен к суммирующему входу первого реверсивного счетчика, соединенного выходами разрядов с цифровыми входами цифроаналогового преобразователя и первыми входами элементов И первой группы, подключенных выходами к первым входам элементов ИЛ15 группы, соединенных; вторыми входами с выходами . элементов И второй группы, а выходами - с информационными входами выходного сумматора, начиная с его второго разряда, отличающийс я тем, что, с целью расширения области применения и повышения быстродействия квадратора, в него дополнительно введены второй реверсивный счетчик, дешифратор,нуля и триггер знака, подключенный пулевьм и единичным входами к третьему и четвертому импульсным выходам блока коммутации соответственно, а выходом - к знако вому входу цифроаналогового преобразователя и третьему управляющему (П входу блока коммутации, соединенно- , го четвертым управляющим .входом..с выходом дешифратора нуля, первым потенциальным выходом - с вторыми ВХО дами элементов И .первой группы, а вторым потенциальным выходом - с первыми входами элементов И второй группы, подключенных вторыми входами к выходам разрядов второго реверсивного счетчика, соединенного суммирующим входом с выходом первого элемента задержки, а вычитающим входам с выходом второго элемента задержки и вычитающим входом первого реверсивного счетчика, выходы разрядов которого подключены к входам дешифратора нуля, а псрвьш и второй импульсные выходы блока коммутации соединены с управляющими входами сложения и вычитания выходного су 1матора соответственно, подключенного входом младшего разряда к шине логической единицы.

...... t

Фаг. 1

ipaz.Z

Xiit)

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 0 |

|

SU365830A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для возведения в квадрат | 1980 |

|

SU898447A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Введение в кибернетическую технику | |||

| Обработка физической инфор- | |||

| мации | |||

| Под ред. | |||

| Б.Н.Малиновского | |||

| Киев, Наукова думка, 1979, с | |||

| Приспособление, увеличивающее число оборотов движущихся колес паровоза | 1919 |

|

SU146A1 |

Авторы

Даты

1984-10-23—Публикация

1983-03-10—Подача