выход каждого i-ro узла коммутации соединен с i-biM входом (т + 2)-го элемента ИЛИ, выход которого подключен к первому входу первого элемента И и к первому управляющему входу узла .перезаписи, информационные входы которого соединены с выходами первого счетчика, а выходы - со входами регистра, выходы которого подключены к информа;цио,нным входам узла анализа на равенство, выход которого соединен с .первым входом (/п + 3)-го элемента ИЛИ и входом сброса первого счетчика, триггер, счетчики и элементы И, ИЛИ, НЕ, выход каждого /-го элемента ИЛИ через /-и элемент НЕ соединен с /-м.и входами всех узлов анализа и с первым входом (/-Ы)-го, а+т+1)-го и (/ + 2/7г+1)-го элементов И. Выход (т-h 1)-го элемента ИЛИ подключен к первым входам пятого (3/и + 2)-го элемента И, (т+ 4)-го элемента ИЛИ, ко вторым входам (от-f 2)-го, (/п + 3)-го, (2т-Ы)-го элементов И, ко второму управляюы1,ему входу узла перезаписи, к первым входам каждого (/Ч-Зт + 2)-го элемента И, и через (т+1)-н элемент НЕ к первому управляющему входу ззла анализа на равенство, к первому входу (4т + 3)-го элемента И и ко второму .входу первого элемента И. Выходы каждого /-го элемента НЕ соединены со вторым входом (/ + 3/п + 2)-го элемента И. Выходы (Зт + + 3)-го, (Зот + 4)-го и (4от + 2)-го элементов И .подключены к соответствующим информационным входам второго счетчика. Вход управления устройства соединен с четвертыми входами узлов анализа, со вторыми входами (Зт + 2)-го и (4т + 3)-го элементов И. Выходы (/Ч-1)-го, (/ + 2)-го, ..., (от+1)-го элементов И подключены ко входам третьего счетчика. Выход (З/п + 2)го элемента И соединен со входами сложения второго И третьего счетчиков и с первым входом ()-го элемента ИЛИ, вы.ход которого подключен ко входу сложения первогосчетчика. Выход первого элемента И соединен со вторым входом (т + 3)-го элемента ИЛИ, выход которого подключен ко входу установки в единичное состояние триггера, инверсный выход которого соединен с третьим входом (4отН-3)-го элемента И, выход которого подключен ко вторым входам (т+ 4)-го и (т+ 5)-го элементов ИЛИ, ко входу вычитания второго счетчика, ко вторым входам (2/72+2), (2т+ 3), .. ., (3/п-Ы)-го элементов И, выходы которых соединены со входами второго счетчика, выходы которого подключены .ко вторым информационным входам узла анализа на равенство. Прямой выход триггера соедпнеи с первым входом (4т+ 4)-го элемента И, второй вход которого через (т + 2)-й элемент НЕ подключен к выходу узла анализа на равенство, а выход (4т-|-4)-го элемента И соединен со входом сброса регистра. Выход (fn + Ч.ГТР.1РНТЯ И.ГТИ пптпгптири vn

вторым входам (от+2), (т + З), ..., (2т+1)-го элементов И, выходы которых подключены ко входам первого счетчика. Каждый из узлов анализа содержит счетчик, элементы И, ИЛИ. Каждый /-и информационный вход счетчика соединен с /-ым входом узла, где ,2,..., т. Прямые выходы счетчика подключены ко входам элемента ИЛИ, а инверсные выходы - к первым входам каждого /-го элемента И соответственно. Выход каждого /-го элемента И соединен с /-ым выходом узла. Выход элемента ИЛИ подключен к (т+1)-му выходу узла и к первому входу {т+ 1)-го элемента И .и вторым входам 1,2, . . . , т-го элементов И. Второй вход (т+1)-го элемента И соединен с (т+1)-ы,м вхо.дом узла, выход (т-М)-го элемента И подключен ко входу вычитания счетчика. Узлы коммутации содержат элементы И и НЕ, причем информационный вход узла соединен с первым входом первого элемента И и через элемент НЕ с первым входом второго элемента И. Вторые входы элементов И подключены ко входу управления, выходы первого н второго элементов И соединены с первым и вторым выходами узла соответственно.

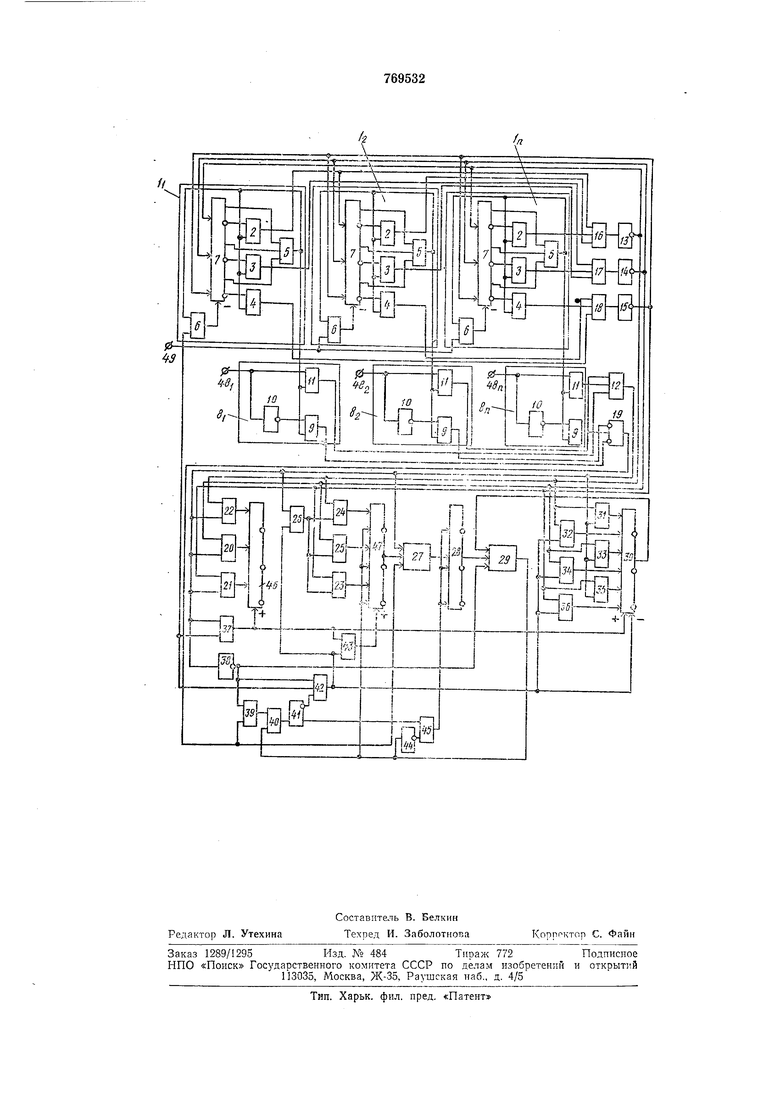

Функциональная схема устройства ири.ведена на чертеже. В качестве примера рассматривается сравнение трехразрядных чисел.

Устройство содержит узлы апализа li- /„, каждый из которых состоит из элементов И 2-4, элемента ИЛИ 5, элемента И 6 и счетчика 7, узлы коммутации 8i-5„, каж.дый из ivOTOpbix состоит из элемента И 9, элемента ИЛИ 10, элемента И //, элемент ИЛИ 12, элементы НЕ 13-15, элементы ИЛИ 16-18, элемент ИЛИ 19, элементы И 20-25, элемент ИЛИ 26, узел перезаписи 27, регистр 28, узел а.нализа на равенство 29, счетчик 30, элементы И 31-37, элемент НЕ 38, элемент И 39, элемент ИЛИ 40, триггер 41, элемент И 42, элемент ИЛИ 43, элемент НЕ 44, элемент И 45, счетчики 46, 47.

Устройство работает следующим образом.

В исходном состоянии сравниваемые числа записаны в счетчиках узло.в анализа h-ln, счетчики 46, 47, 30 и регистр 28 очищены, триггер 41 установлен в «О. На выходах элементов ИЛИ узлов анализа, а следовательно, на первых входах элементов И 6 имеется сигнал. Заданное число устана.вливается иодачей на один из информационных входов 4:8i-48п сигнала, сохраняемого в течение всего времени работы Зстройства. При этом появляется сигнал на первом входе соответствующего элемента И узла кО|М;мутац,ии 5i-5„, .на входе и, соответствепно, на выходе элемента ИЛИ 12.

И 22, 20, 21, 24, 25, 23, 31, 33, 35 и 37 и первый вход узла перезаписи 27.

После лоступления на вход управления 49 разрешающего сигнала, который сохраняется в течение всего времени работы устрой-ства. Сигнал через все элементы И 6 проходит на вычитающие входы счетчиков 7 узлов анализа /i-/„, и из всех чисел вычитается единица.

Сигнал через элемент И 37 поступает на суммирующий вход счетчиков 46 }i 30 w. через элемент ИЛИ 43 на суммирующий вход счетчика 47. К содержимому счетчиков прибавляется единица.

В случае, если в процессе вычита«ия единиц из счетчиков 7 узлов анализа h-i-/n, в их одноименных разрядах одновременно окажутся записанными единицы, исчезают сигналы на нервых входах, а следовательно, на выходах всех элементов И данного разряда. В результате на выходе соответствующего инвертора появится сигнал, который стирает содержимое этого разряда во всех счетчиках 7 узлов анализа /1-/п и прибавляет единицу к этому разряду через элемент И 20 счетчика 46, элемент И 25 счетЧИка 47 и элемент И 38 счетчика 30.

После некоторого количества чередований стирания равных разрядов с вычитанием единиц содержимое одного (или нескольких) счетчиков 7 узлов анализа становится равным нулю. При этом исчезает сигнал на первом входе, а следовательно, на выходе соответствующего элемента И 9. Исчезновение этого сигнала фиксируется элементом ИЛИ 19. Сигнал проходит на разрешающий вход узла перезаписи 27, и содержимое счетчика 47 перезаписывается в регистр 28.

В случае, когда равным нулю становится содержимое счетчика, в котором записано заданное число, исчезает сигнал на первом входе, следовательно, на выходе соответствующего элемента И 11, исчезает сигнал на выходе элемента ИЛИ 12, и отключаются, таким образом, элементы И 22, 20, , 3.1, 33, 35, 37 и узел перезаписи 27. При этом появляется сигнал на выходе элемента НЕ 38, следовательно, на первом входе элемента И 42, на разрещающем входе узла анализа на равенство 29. В счетчике 46 остается записанным заданное число. Поступающие через элементы ИЛИ 26 и 43 сигналы продолжают сум мироваться в счетчике 47. Через элементы И 32, 34, 36 « с выхода элемента И 42 сигналы поступают теперь на вычитающие входы соответствующих разрядов и счетчика 30. Содержимое счетчика 30 с этого момента уменьщается. Если до обращения в нуль содержимого очередного счетчика (числа, большего заданного) содержимое счетчика 30 становится равным содержимому регистра 28, появляется сигнал на выходе узла

анализа на равенство 29. Это свидетельствует о том, что число, меньшее заданного, ближе к нему, чем больщее. Сигнал с выхода узла анализа на равенство 29 стирает содержимое счетчика 47, перебрасывает через элемент ИЛИ 40 триггер 41. Устройство прекращает работу, в регистре 28 записано число, ближайщее к заданному. Когда обращается в нуль содерл имое счетчика, в котором записано число, больщее заданного, исчезновение сигнала с выхода соответствующих элементов 5 и 9 фиксируется элементом ИЛИ 19. Сигнал с его выхода через элементы И 39 и элемент ИЛИ 40 перебрасывает триггер 41. Если при этом сигнал на выходе узла анализа на равенство 29 отсутствует, сигнал с выхода элемента И 45 стирает содержимое регистра 28. Устройство прекращает работу, а в счетчике 47 записано число, ближайшее к заданному.

Если при появлении сигнала на выходе элемента ИЛИ 19 есть сигнал и на выходе узла анализа на равенство 29, исчезает сигнал на втором входе, а следовательно, на выходе элемента И 45. В счетчике 47 и регистре 28 записаны оба числа, ближайшие ж заданному.

Устройство позволяет расширить функциональные возможности, поскольку при достаточной схемной простоте дает возможность выбрать из множества чисел ближайшее большее, ближайшее меньшее к заданному числу число или оба этих числа с записью каждого числа в конкретный регистр.

Формула изобретения

1. Устройство для сравнения чисел, содержащее п узлов анализа, причем /-Й выход каждого i-ro узла анализа, где i, 1,. .. ,п, 1, 2,...,т соединен с i-ым входом каждого /-го элемента ИЛИ соответственно, (т+ выход каждого i-ro узла анализа подключен к первому входу i-ro узла коммута1ции, второй вход каждого i-ro узла коммутации соединен с i-ьъм информационным входом, первый выход каждого i-ro узла коммутации подключен к i-му входу- (m-f 1)-го элемента ИЛИ, а второй выход каждого i-ro узла коммутации соединен с i-biM входом (/п + 2)-го элемента ИЛИ, выход которого подключен к первому входу первого элемента И и к первому упр.авляющему входу узла перезаписи, информационные входы которого соединены с выходами первого счетчика, а выходы - со входами регистра, выходы которого подключены к информационным входам узла анализа на равенство, выход которого соединен с первым входом (т + 3)-го элемента ИЛИ и входом сброса первого счетчика, триггер, счетчики, элементы И, ИЛИ, НЕ, отличающееся тем, что, с целью расширения функциональных возможностей

устройства путем определения числа, ближайшего к заданлому, в нем выход каждого г-го элемента ИЛИ через /-Й элемент НЕ соединен с /-ми входами Bicex узлов анализа |И с первым входом (j+i)-ro, (j + m+ +1)-го л (/ + 2/n-fil)-ro элементов И, выход (т+1)-го элемента ИЛИ подключен к первым входам (3т+ 2)-го элемента И, (т+ 4)-го элемента ИЛИ, ко вторым входам (m-f2)-ro, {т + 3)-т,..., (2т+1)-го элементов И, ко второму управляющему входу узла перезаписи, к первЫМ входам каждого (/-f-3/n-f 2)-го элемента И и через (т-Ы)-й элемент НЕ к первому управляющему входу узла анализа на равенство, к первому входу (4тН-3)-го элемента И и ко второму входу первого элемента И, выход каждого /-ГО элемента НЕ соединен со вторым входом (/-ЬЗт+|2)-го элемента И, .выходы (З/п-f 3)-го, (Зт+4)-го,. . ., (4т+ +2)-го элементов И подключены к соответствующим информационным входам второго счетчика, вход управления устройства соединен с четвертыми входами узлов анализа, со вторыми входами (Зт+2)-го и (4/п-ЬЗ)-го элементов И, выходы (/4-1)-го, (/+2)-го, .. ., (m-i-l)-ro элементов И подключены ко входам третьего -счетчика, выход (3т+ 2)-го элемента И соединен со входами сложения второго и третьего счетчн-ков и с первым входом (т+ 5)-го элемента ИЛИ, выход которого подключен ко входу сложения первого счетчика, выход первого элемента И соединен со вторым входом (т+3)-го элемента ИЛИ, выход которого подключен ко входу установки в единичное состояние триггера, инверсный выход которого соединен с третьим входом (4т + 3)-го элемента И, выход которого подключен ко вторым входам (т+4)-го и (т+ 5)-го элементов ИЛИ, ко входу вычитания второго счетчика, ко вторым входам (2/и+2)-го, (2т-ьЗ)-го, ..., (Зт+1)-го э/яементов И, выходы которых соединены со входами второго счетчика, выходы которого подключены ко вторым информационным входам узла анализа на равенство.

прямой выход триггера соединен с первым входом (т-ь4)-го элемента И, второй вход которого через (т-|-2)-й элемент НЕ подключен к выходу узла анализа на равенство, а выход (4т+ 4)-го элемента И соединен со входом сброса регистра; выход (m-f4)-ro элемента ИЛИ подключен ко вторым входам (т + 2)-го, (т + 3)-го, ..., (2т+1)-го элементов И, выходы которых подключены ко входам первого счетчика.

2.Устройство по п. 1, отличающеес я тем, что в нем каждый из узлов анализа содержит счетчик, элементы И, ИЛИ, причем каждый /-и информационный вход счетчика соединен с /-ьш входом узла, где ,2,..., т, прямые выходы счетчика подключены ко входам элемента ИЛИ, а инверсные выходы - к первым входам каждого /-ГО элемента И соответственно, выход каждого /-ГО элемента И соединен с /-ым выходом узла, выход элемента ИЛИ подключен к (т+1)-му выходу узла и к первому входу (т+1)-го элемента И и вторым входам 1,2,..., т-го элементов И, второй вход (т+1)-го элемента И соединен с (т+1)-ым входом узла, а выход (т+1)-го элемента И подключен жо входу вычитания счетчика.

3.Устройство по п. 1, отличающеес я тем, что в нем узлы коммутации содержат элементы И и НЕ, причем информационный вход узла соединен с первым входом первого элемента И и через элемент НЕ с первым входом .второго элемента И, вторые входы элементов И подключены ко входу управления, выходы первого и второго элементов И соединены с первым и вторым выходами узла соответственно.

Источники информации, принятые во внимание при экспертизе:

1.Авторское свидетельство СССР № 246924, кл. G 06 Е 7/06, 20.06.69.

2.Авторское свидетельство СССР № 603986, кл. G 06 F 7/04, 10.04.78 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления квадратного корня числа в модулярной системе счисления | 1985 |

|

SU1317434A1 |

| Устройство для упорядочивания чисел | 1980 |

|

SU932487A1 |

| Устройство для сортировки чисел | 1989 |

|

SU1793438A1 |

| Устройство для контроля параметров | 1979 |

|

SU842721A1 |

| Устройство аналого-цифрового преобразования узкополосных сигналов | 1986 |

|

SU1336234A1 |

| Устройство для сравнения чисел | 1980 |

|

SU903862A1 |

| Устройство для определения достоверности информации | 1975 |

|

SU610110A1 |

| Устройство для упорядочивания чисел | 1981 |

|

SU1012239A1 |

| Устройство записи-воспроизведения цифровой информации на магнитном носителе | 1981 |

|

SU980138A1 |

| Устройство для сравнения весов кодов | 1979 |

|

SU798810A1 |

Авторы

Даты

1980-10-07—Публикация

1978-03-21—Подача