тей периода центральной частоты сигнала. В полученной последовательности отсчетов мгновенных значений после преобразования их с помощью аналого- цифрового преобразователя 2 в цифровую форму формирователем 3 знака инвертируется знак каждой второй пары отсчетов. Четные отсчеты сформированной таким образом последовательности относятся к косинусной квадратурной

1

Изобретение относится к импульсной технике и предназначено для цифрового представления аналоговых узкополосных сигналов.

Цель изобретения - расширение функциональных возможностей устройства, за счет измерения квадратурных составляющих сигнала.

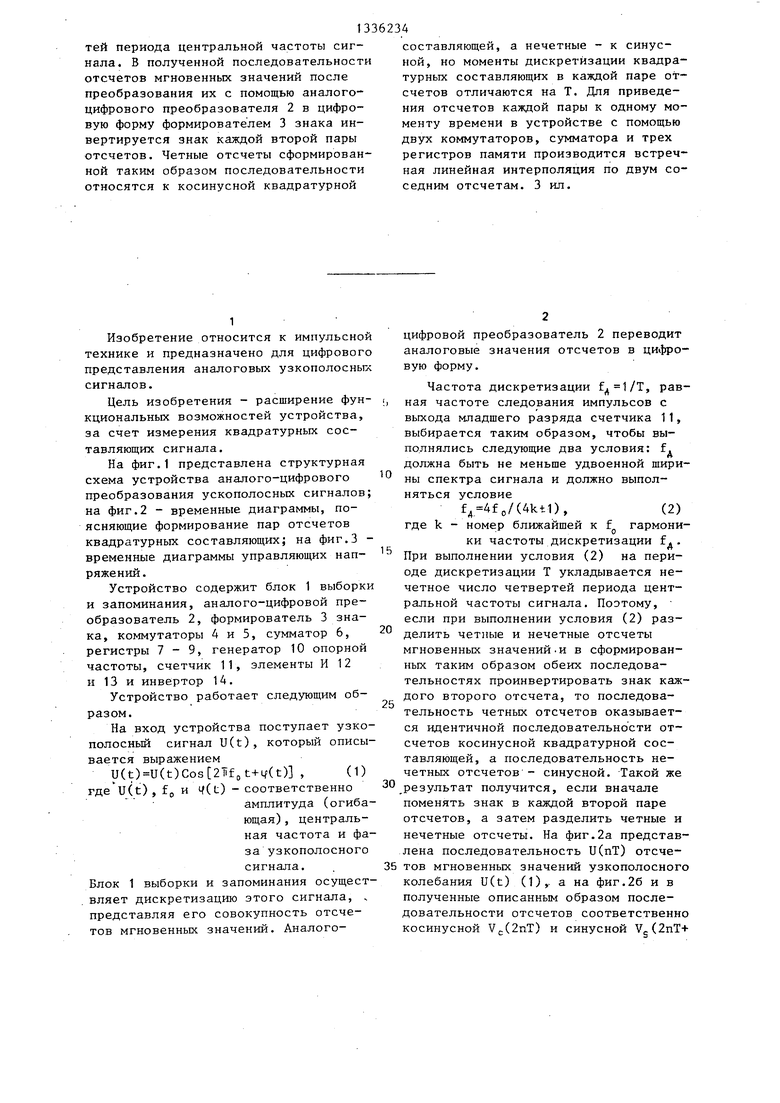

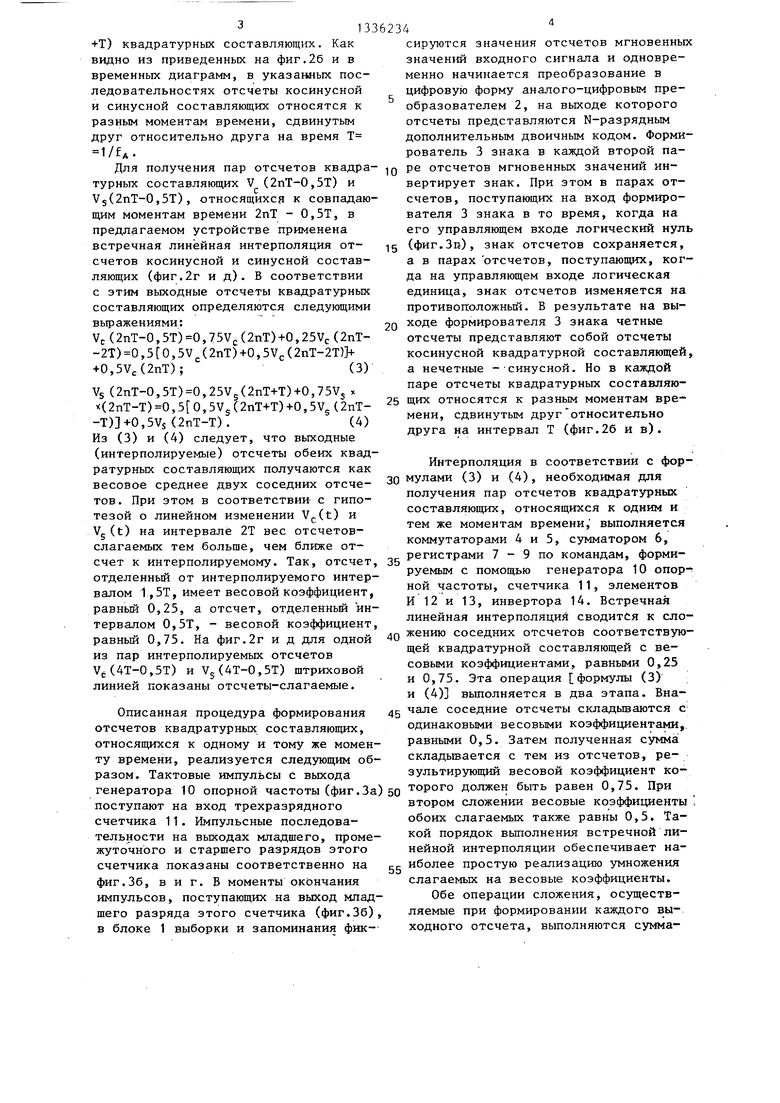

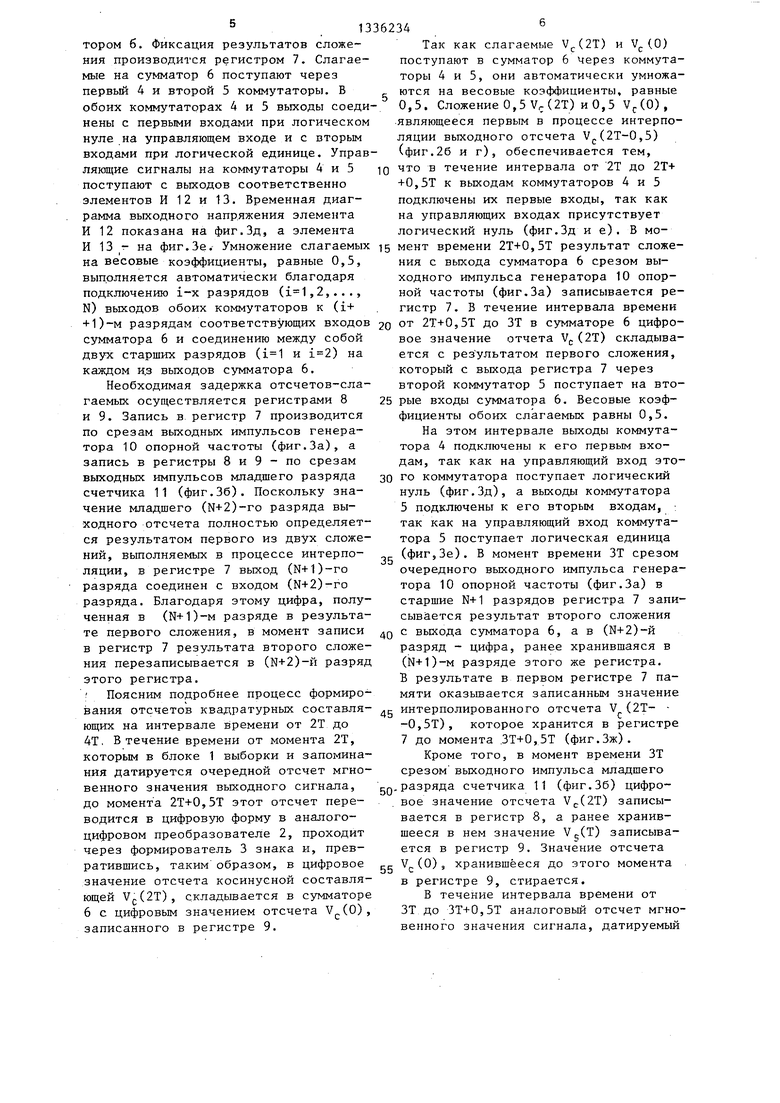

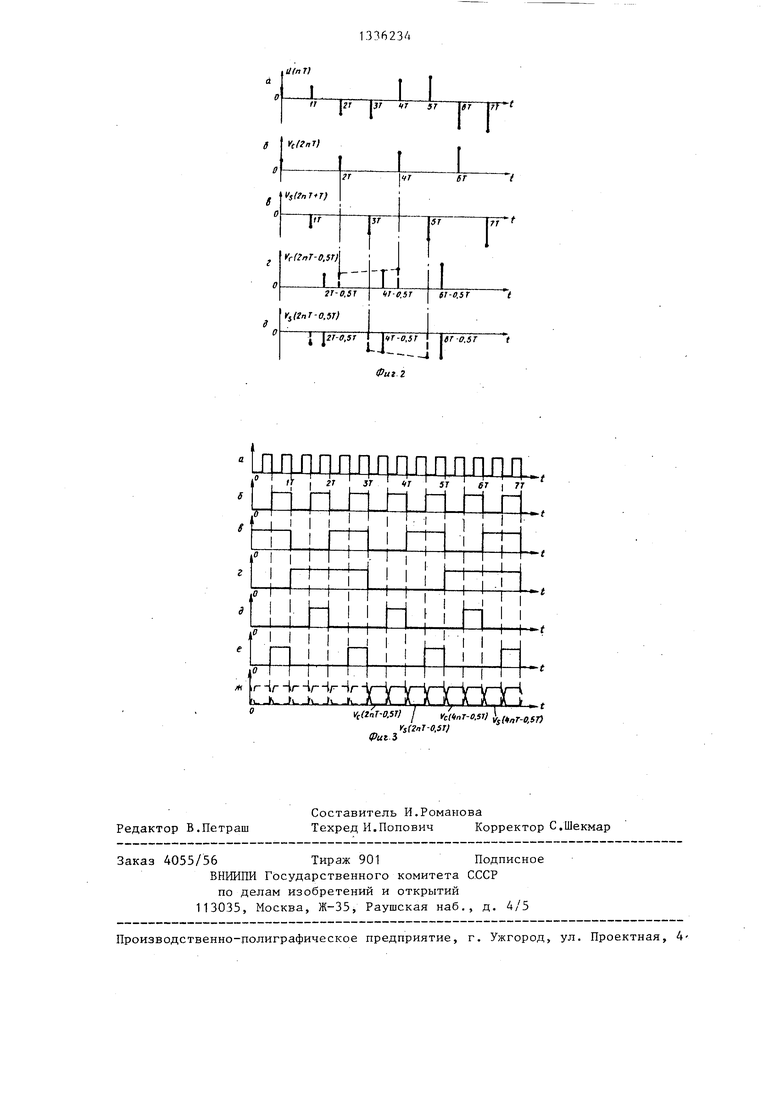

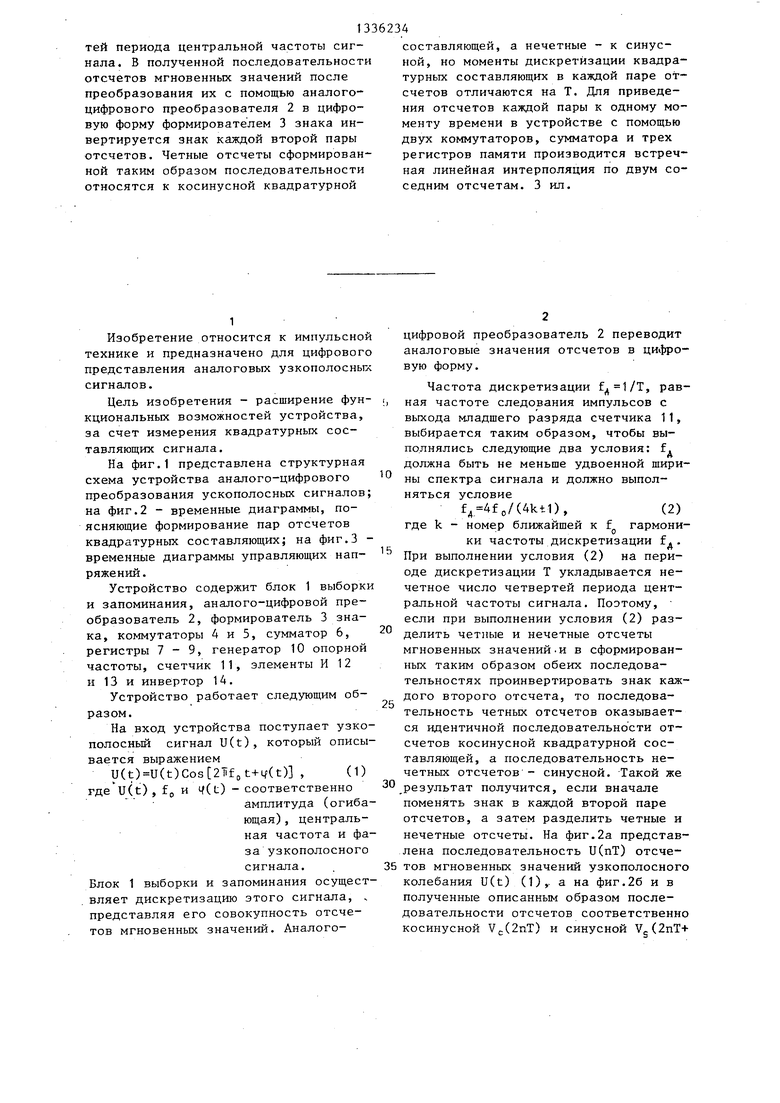

На фиг.1 представлена структурная схема устройства аналого-цифрового преобразования ускополосных сигналов; на фиг.2 - временные диаграммы, поясняющие формирование пар отсчетов квадратурных составляющих; на фиг.З - временные диаграммы управляющих напряжений.

Устройство содержит блок 1 выборки и запоминания, аналого-цифровой преобразователь 2, формирователь 3 знака, коммутаторы 4 и 5, сумматор 6, регистры 7-9, генератор 10 опорной частоты, счетчик 11, элементы И 12 и 13 и инвертор 14.

Устройство работает следующим образом.

На вход устройства поступает узкополосный сигнал U(t), который описывается выражением

y(t)U(t)Cos 2lift,t+M(t)l , (1) гдe u(t) , fo и i/d) - соответственно

амплитуда (огибающая) , центральная частота и фаза узкополосного сигнала.

Блок 1 выборки и запоминания осуществляет дискретизацию этого сигнала, . представляя его совокупность отсчетов мгновенных значений. Аналогосоставляющей, а нечетные - к синусной, но моменты дискретизации квадратурных составляющих в каждой паре отсчетов отличаются на Т. Для приведения отсчетов каждой пары к одному моменту времени в устройстве с помощью двух коммутаторов, сумматора и трех регистров памяти производится встречная линейная интерполяция по двум соседним отсчетам. 3 ил.

0

й

5

0

5

цифровой преобразователь 2 переводит аналоговые значения отсчетов в )ро- вую форму.

Частота дискретизации , равная частоте следования импульсов с выхода младшего разряда счетчика 11, выбирается таким образом, чтобы выполнялись следующие два условия: f. должна быть не меньше удвоенной ширины спектра сигнала и должно выполняться условие

(4kt1),(2)

где k - номер ближайшей к f гармоники частоты дискретизации f, . При выполнении условия (2) на периоде дискретизации Т укладывается нечетное число четвертей периода центральной частоты сигнала. Поэтому, если при выполнении условия (2) разделить четные и нечетные отсчеты мгновенных значений.и в сформированных таким образом обеих последовательностях проинвертировать знак каждого второго отсчета, то последовательность четных отсчетов оказывается идентичной последовательности отсчетов косинусной квадратурной составляющей, а последовательность нечетных отсчетов - синусной. Такой же ,результат получится, если вначале поменять знак в каждой второй паре отсчетов, а затем разделить четные и нечетные отсчеты. На фиг.2а представлена последовательность U(nT) отсчетов мгновенных значений узкополосного колебания U(t) (1),. а на фиг.26 и в полученные описанным образом последовательности отсчетов соответственно косинусной V(,(2uT) и синусной У5(2пТ+

+Т) квадратурных составляющих. Как видно из приведенных на фиг.26 и в временных диаграмм, в указанных последовательностях отсчеты косинусной и синусной составляющих относятся к разным моментам времени, сдвинутым друг относительно друга на время Т

1/fA.

Для получения пар отсчетов квадратурных составляющих V (2пТ-0,5Т) и V5(2nT-0,5T), относящихся к совпадающим моментам времени 2пТ - 0,5Т, в предлагаемом устройстве применена встречная линейная интерполяция отсчетов косинусной и синусной составляющих (фиг.2г и д). В соответствии с этим выходные отсчеты квадратурных составляющих определяются следующими выражениями:

Vc(2nT-0,5T)0,75V(.(2nT)+0,25Vc(2nT- -2Т) 0,5 0, 5V (2пТ) +0,5 V (2пТ-2Т)+ +0,);(3)

YS(2nT-0,5T)0,25Vs(2nT+T)+0,75V5 42nT-T)0,,5V5(2nT+T)+0,5V5(2nT- -T)+0,5Vs (2пТ-Т),(4)

Из (3) и (4) следует, что выходные (интерполируемые) отсчеты обеих квадратурных составляющих получаются как весовое среднее двух соседних отсчетов. При этом в соответствии с гипотезой о линейном изменении V(.t) и Vg (t) на интервале 2Т вес отсчетов- слагаемых тем больше, чем ближе отсчет к интерполируемому. Так, отсчет, отделенньш от интерполируемого интервалом 1,5Т, имеет весовой коэффициент, равный 0,25, а отсчет, отделенный интервалом 0,5Т, - весовой коэффициент, равный 0,75. На фиг.2г и д для одной из пар интерполируемых отсчетов Vt(4T-0,5T) и 75(41-0,51) штриховой линией показаны отсчеты-слагаемые.

Интерполяция в соответствии с фор- 30 мулами (3) и (4), необходимая для получения пар отсчетов квадратурных составляющих, относящихся к одним и тем же моментам времени, выполняется коммутаторами 4 и 5, сумматором 6, регистрами 7 - 9 по командам, формируемым с помощью генератора 10 опорной частоты, счетчика 11, элементов И 12 и 13, инвертора 14. Встречная линейная интерполяция сводится к сло- 4Q жению соседних отсчетов соответствующей квадратурной составляющей с весовыми коэффициентами, равными 0,25 и 0,75. Эта операция Формулы (3) и (4) выполняется в два этапа. Вначале соседние отсчеты складьшаются с одинаковыми весовыми коэффициентами,, равными 0,5. Затем полученная сумма складьшается с тем из отсчетов, результирующий весовой коэффициент ко45

Описанная процедура формирования отсчетов квадратурных составляющих, относящихся к одному и тому же моменту времени, реализуется следующим образом. Тактовые импул1зсы с выхода генератора 10 опорной частоты (фиг.За) 50 должен быть равен 0,75. При поступают на вход трехразрядного втором сложении весовые коэффициенты счетчика 11. Импульсные последовательности на выходах младшего, промежуточного и старшего разрядов этого счетчика показаны соответственно на фиг.Зб, в и г. Б моменты окончания импульсов, поступающих на выход младшего разряда этого счетчика (фиг.Зб),

55

обоих слагаемых также равны 0,5. Такой порядок вьшолнения встречной линейной интерполяции обеспечивает наиболее простую реализацию умножения слагаемых на весовые коэффициенты.

Обе операции сложения, осуществляемые при формировании каждого выв блоке 1 выборки и запоминания фйк6234

сируются значения отсчетов мгновенных значений входного сигнала и одновременно начинается преобразование в цифровую форму аналого-цифровым преобразователем 2, на выходе которого отсчеты представляются N-разрядным дополнительным двоичным кодом. Формирователь 3 знака в каждой второй па10 ре отсчетов мгновенных значений инвертирует знак. При этом в парах отсчетов, поступающих на вход формирователя 3 знака в то время, когда на его управляющем входе логический нуль

15 (фиг.Зп), знак отсчетов сохраняется, а в парах отсчетов, поступающих, когда на управляющем входе логическая

единица, знак отсчетов изменяется на противоаоложньш. В результате на выходе формирователя 3 знака четные отсчеты представляют собой отсчеты косинусной квадратурной составляющей, а нечетные --синусной. Но в каждой паре отсчеты квадратурных составляю- щих относятся к разным моментам времени, сдвинутым друг относительно друга на интервал Т (фиг.26 и в).

Интерполяция в соответствии с фор- улами (3) и (4), необходимая для получения пар отсчетов квадратурных составляющих, относящихся к одним и тем же моментам времени, выполняется коммутаторами 4 и 5, сумматором 6, регистрами 7 - 9 по командам, формируемым с помощью генератора 10 опорной частоты, счетчика 11, элементов 12 и 13, инвертора 14. Встречная инейная интерполяция сводится к сло- ению соседних отсчетов соответствующей квадратурной составляющей с весовыми коэффициентами, равными 0,25 и 0,75. Эта операция Формулы (3) и (4) выполняется в два этапа. Вначале соседние отсчеты складьшаются с одинаковыми весовыми коэффициентами,, равными 0,5. Затем полученная сумма складьшается с тем из отсчетов, результирующий весовой коэффициент ко

должен быть равен 0,75. При втором сложении весовые коэффициенты

50 должен быть равен 0,75. При втором сложении весовые коэффициенты

55

обоих слагаемых также равны 0,5. Такой порядок вьшолнения встречной линейной интерполяции обеспечивает наиболее простую реализацию умножения слагаемых на весовые коэффициенты.

Обе операции сложения, осуществляемые при формировании каждого выходного отсчета, выполняются сумма 1336234б

тором б. Фиксация результатов сложе- Так как слагаемые V(2T) и V. (0) ния производится регистром 7. Слагав- поступают в сумматор 6 через коммута- мые на сумматор 6 поступают через торы 4 и 5, они автоматически умножа- первый 4 и второй 5 коммутаторы. В ются на весовые коэффициенты, равные обоих коммутаторах 4 и 5 выходы соеди- 0,5, Сложение 0,5 V(2Т) и 0,5 V(0), иены с первыми входами при логическом являющееся первым в процессе интерпо- нуле на управляющем входе и с вторьм ляции выходного отсчета У(2Т-0,5) входами при логической единице. Управ- (фиг.26 и г), обеспечивается тем, ляющие сигналы на коммутаторы 4 и 5 ю что в течение интервала от 2Т до 2Т+ поступают с выходов соответственно +0,5Т к выходам коммутаторов 4 и 5 элементов И 12 и 13. Временная диаг- подключены их первые входы, так как рамма выходного напряжения элемента на управляющих входах присутствует И 12 показана на фиг.Зд, а элемента логический нуль (фиг.Зд и е). В мо- И 13 г- на фиг.Зе. Умножение слагаемых 5 мент времени 2Т+0,5Т результат сложена весовые коэффициенты, равные 0,5, ния с выхода сумматора 6 срезом вы- выполняется автоматически благодаря ходного импульса генератора 10 опор- подключению i-x разрядов (,2,..., ной частоты (фиг.За) записывается ре- N) выходов обоих коммутаторов к (i+ . гистр 7. В течение интервала времени +1)-м разрядам соответствующих входов 2о от 2Т+0,5Т до ЗТ в сумматоре 6 цифро- сумматора 6 и соединению между собой вое значение отчета V. (2Т) складыва- двух старших разрядов ( и ) на ется с результатом первого сложения, каждом и.з выходов сумматора 6. который с выхода регистра 7 через

Необходимая задержка отсчетов-сла- второй коммутатор 5 поступает на вто- гаемых осуществляется регистрами 8 25 рые входы сумматора 6. Весовые коэф- и 9. Запись в регистр 7 производится фициенты обоих слагаемых равны 0,5. по срезам выходных импульсов генера- На этом интервале выходы коммутатора 10 опорной частоты (фиг.За), а тора 4 подключены к его первым вхо- запись в регистры 8 и 9 - по срезам дам, так как на управляющий вход это- выходньпс импульсов младшего разряда зо коммутатора поступает логический счетчика 11 (фиг.36). Поскольку зна- нуль (фиг.Зд), а выходы коммутатора чение младшего (N+2)-ro разряда вы- 5 подключены к его вторым входам, ходного отсчета полностью определяет- так как на управляющий вход коммута- ся результатом первого из двух сложе- тора 5 поступает логическая единица НИИ, выполняемых в процессе интерпо- (фиг,3е). В момент времени ЗТ срезом ляции, в регистре 7 выход (N+1)-ro очередного выходного импульса генера- разряда соединен с входом (N+2)-ro тора 10 опорной частоты (фиг.За) в разряда. Благодаря этому цифра, полу- старшие N+1 разрядов регистра 7 запи- ченная в (N+1)-M разряде в результа- сывается результат второго сложения те первого сложения, в момент записи Q с выхода сумматора 6, а в (Н+2)-й в регистр 7 результата второго сложе- разряд - цифра, ранее хранившаяся в ния перезаписывается в (Н+2)-й разряд (Н+1)-м разряде этого же регистра, этого регистра.В результате в первом регистре 7 па Поясним подробнее процесс формиро- мяти оказьшается записанным значение вания отсчетов квадратурных составля- g интерполированного отсчета V (2Т- - ющих на интервале времени от 2Т до -0,5Т), которое хранится в регистре 4Т, В течение времени от момента 2Т, 7 до момента .ЗТ+0,5Т (фиг.Зж). которым в блоке 1 выборки и запомина- Кроме того, в момент времени ЗТ ния датируется очередной отсчет мгно- срезом выходного импульса младщего венного значения выходного сигнала, gg.разряда счетчика 11 (фиг.Зб) цифро- до момента 2Т+0,5Т этот отсчет пере- вое значение отсчета V(-(2T) записы- водится в цифровую форму в аналого- вается в регистр 8, а ранее хранив- цифровом преобразователе 2, проходит шееся в нем значение Vj-CT) записыва- через формирователь 3 знака и, прев- ется в регистр 9. Значение отсчета ратившись, таким образом, в цифровое gg V, (0), хранившееся до этого момента значение отсчета косинусной составля- в регистре 9, стирается, ющей Vj,(2T), складьшается в сумматоре В течение интервала времени от 6 с цифровым значением отсчета ,(0), ЗТ до ЗТ+0,5Т аналоговый отсчет мгно- записанного в регистре 9.венного значения сигнала, датируемый

7

моментом ЗТ, в аналого-цифровом преобразователе 2 переводится в цифровую форму, проходит через формирователь 3 знака и, превратившись в цифровое значение отсчета У;(ЗТ), складывается в сумматоре 6 с цифровым значением отсчета VgCT), поступающим с выхода регистра 9. Оба слагаемые суммируготся с весовыми коэффициентами, равными 0,5, так как они поступают на сумматор 6 через коммутаторы 4 и 5. Поступление этих слагаемых в течение указанного времени обеспечивается тем, что на управляющих входа коммутаторов в течение этого времени присутствует логический нуль (фиг.Зд и е). Описанное сложение является первым в процессе интерполяции отсчета Vs(2T-0,5T). В момент ЗТ+0,5Т результат сложения записывается в регистр 7.

В течение времени от ЗТ+0,5Т до 4т сумматор 6 производит сложение (с весовыми коэффициентами 0,5) результата предыдущего сложения и отсчета Vg(T). Результат предьщущего сложения поступает на сумматор 6 с выхода регистра 7 через первый коммутатор 4, на управляющем входе которого в это время присутствует логическая единица (фиг.Зд) и его выходы подключены к вторым входам. На управляющем входе коммутатора 5 в течение интервала от ЗТ+0,5Т до 41 присутствует логический нуль (фиг.Зе), и его выходы подключены к первым входам, пропуская цифровое значение отсчета Vg(T) с выхода регистра 9 на вход сумматора. В момент 4Т в регистр 7 записывается интерполированное значе

ние отсчета V5(2nT-0,5T), которое сохраняется в нем до момента 4Т+0,5Т

(фиг.Зж).

Формула изобретения Устройство аналого-цифрового преобразования узкополосных сигналов, содержащее блок выборки и запоминания вход которого является входной шиной, аналого-цифровой преобразователь, сумматор, выходы которого соединены с соответствующими входами первого регистра, N выходов которого являются выходной информационной шиной и соединены с соответствующими первыми информационными входами первого коммутатора, генератор опорной частоты

,

6234°

и счетчик, отличающееся тем, что, с целью расширения функциональных возможностей, введены форми- - рователь знака, второй и третий регистры, второй коммутатор, два элемента И и инвертор, вход которого объединен с первым входом первого элемента И и соединен с первым выходом счетчика,

IQ а выход соединен с первым входом второго элемента И, второй вход которого объединен с управляющими входами блока выборки и запоминания, аналого- цифрового преобразователя, вторым

15 входом второго элемента И и соединен с вторьп выходом счетчика, вход которого объединен с управляющим входом первого регистра и соединен с выходом генератора опорной частоты, а третий

20 выход - с управляющим входом формирователя знака, информационные входы которого соединены с выходами анало- го-цифрового преобразователя, информационный вход которого соединен с

25 выходом блока выборки и запоминания, выходы формирователя знака соединены с соответствующими вторыми информационными входами первого коммутатора и второго регистра, управляющий вход

30 которого объединен с управляющим входом третьего регистра и соединен с . вторым выходом счетчика, а выходы соединены с соответствующими информа ци- онными входами третьего регистра, вы35 ходы которого соединены с соответствующими первыми информационными входами второго коммутатора, управляющий вход которого соединен с выходом первого элемента И, а вторые информаци40 онные входы соединены с первого по N-й выходами первого регистра, (N+ +1)-й выход которого соединен с (N+ +2)-м входом первого регистра и совместно с (N+2)-M выходом является

45 выходной шиной признака, выход второго элемента И соединен с управляющим входом первого коммутатора, а первый и второй входы в первой и второй группах входов сумматора объединены

50 и соединены с первыми выходами первого и второго коммутаторов соответственно, выходы с второго по N-й первого и второго коммутаторов соединены с соответствующими с третьего

55 по (Ы+1)-й входами первой и второй групп входов сумматора соответственно.

11(пГ)

LA

pr p7 «r S7 pr r

L

r

VT

Уг{гпТ-0.5Т)

I-

LI

гг-o.sj Y(inT-o.sT)

I ZT-tt,sr I ,5г т er -о. 1 I

о.б

Редактор В.Петраш

Составитель И.Романова

Техред И.Попович Корректор С.Шекмар

Заказ 4055/56Тираж 901Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно

-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4LA

«r S7 pr r

rrt

JT

ST

rr

I

1

iir-e.ST

fr-ff.srt

-о.

о.бт t

IVij t У riJ. -k г

Vc(Znr-O.Sr) IVc(4nr-O.S1l .$П

Yf(2nJ-O.ST) Iput 3

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифровой фильтрации на основе дискретного преобразования Фурье | 1990 |

|

SU1795475A1 |

| Демодулятор сигналов с фазоразностной модуляцией | 1980 |

|

SU949838A1 |

| СПОСОБ РЕГИСТРАЦИИ ФАЗЫ КВАДРАТУРНЫХ СИГНАЛОВ | 2018 |

|

RU2692965C1 |

| Анализатор гармоник | 1985 |

|

SU1291894A1 |

| Цифровой линеаризатор | 1982 |

|

SU1056453A1 |

| Устройство для вычисления взвешенного временного ряда | 1976 |

|

SU636620A1 |

| Цифровой перестраиваемый полосовой фильтр | 1982 |

|

SU1166274A1 |

| Устройство для цифровой корреляционнойфильТРАции | 1978 |

|

SU799108A1 |

| Формирователь сигнала цифровой следящей развертки | 1980 |

|

SU936454A2 |

| Устройство для быстрого преобразования Фурье | 1982 |

|

SU1101836A1 |

Изобретение относится к импульсной технике и предназначено для цифрового представления аналоговых узкополосных сигналов. Цель изобретения Вл расширение функциональных возможностей, которое заключается в том, что устройство позволяет формировать как цифровые значения отсчетов мгновенных значений, так -и цифровые значения отсчетов квадратурных составляющих узкополосных сигналов. Устройство содержит блок 1 выборки и запоминания, аналого-цифровой преобразователь 2, формирователь 3 знака, два коммутатора 4 и 5, сумматор 6, три регистра памяти 7-9, генератор 10 опорной частоты, счетчик 11, два элемента И 12 и 13 и инвертор 14. Узкополосный ана- логовьй сигнал в блоке 1 выборки и запоминания дискретизируется с периодом Т, равным нечетному числу четверО (/) СО со О5 to со 4

| Аналого-цифровой преобразователь узкополосных сигналов | 1983 |

|

SU1115224A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство двухступенчатого аналого-цифрового преобразования | 1985 |

|

SU1266003A1 |

Авторы

Даты

1987-09-07—Публикация

1986-04-11—Подача