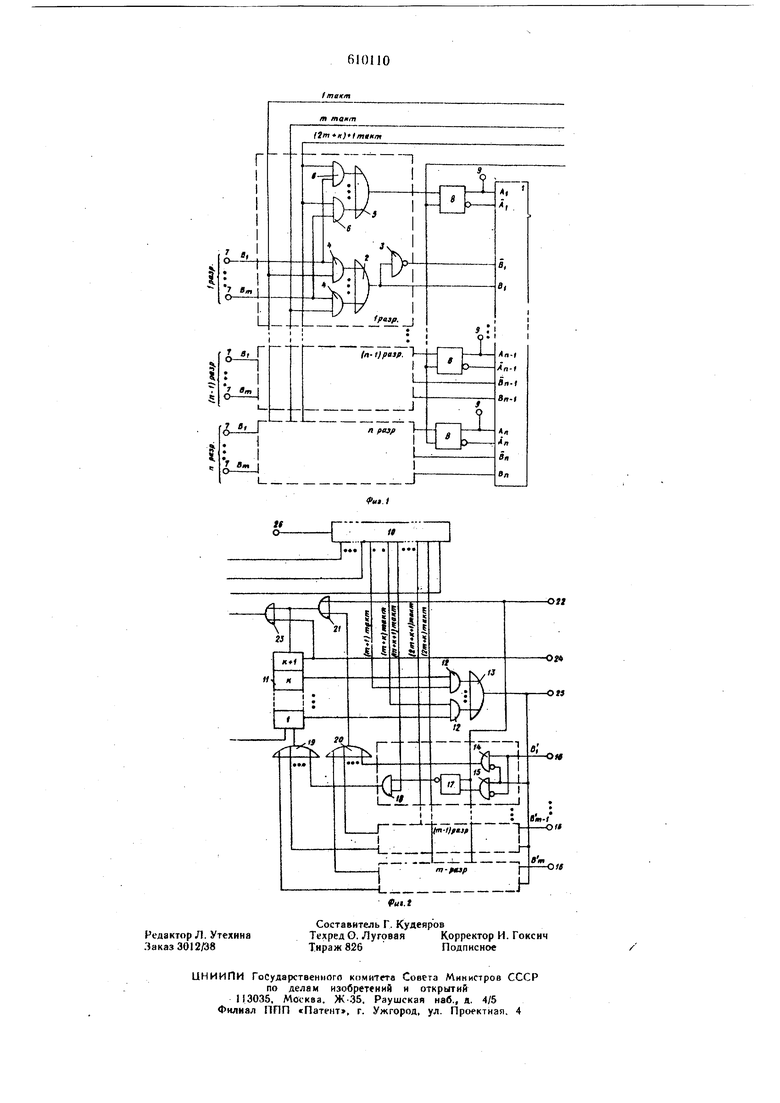

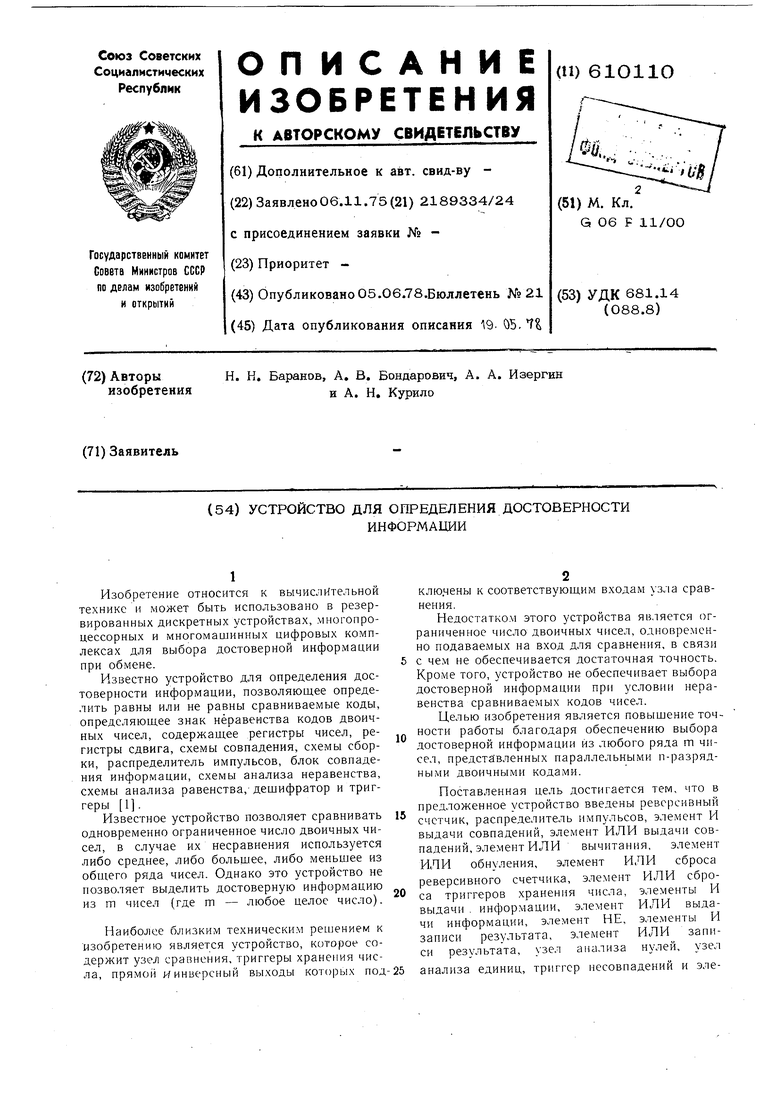

Изобретение относится к вычислительной технике и может быть использовано в резервированных дискретных устройствах, многопроцессорных и многомашинных цифровых комплексах для выбора достоверной информации при обмене. Известно устройство для определения достоверности информации, позволяющее определить равны или не равны сравниваемые коды, определяющее знак неравенства кодов двоичных чисел, содержащее регистры чисел, регистры сдвига, схемы совпадения, схемы сборки, распределитель импульсов, блок совпадения информации, схемы анализа неравенства, схемы анализа равенства,дешифратор и триггеры 1. Известное устройство позволяет сравнивать одновременно ограниченное число двоичных чисел, в случае их несравнения используется либо среднее, либо больщее, либо меньшее из общего ряда чисел. Однако это устройство не позволяет выделить достоверную информацию из m чисел (где m - любое целое число). Наиболее близким техническим ре1иением к изобретению является устройство, которое содержит узел сравнения, триггеры хранения числа, прямой и инверсный выходы которых под клю.чены к соответствующим входам узла сравнения. Недостатком этого устройства является ограниченное число двоичных чисел, одновременно подаваемых на вход для сравнения, в связи с чем не обеспечивается достаточная точность. Кроме того, устройство не обеспечивает выбора достоверной информации при условии неравенства сравниваемых кодов чисел. Целью изобретения является повышение точ ности работы благодаря обеспечению выбора достоверной информации из любого ряда m чисел, представленных параллельными п-разрядными двоичными кодами. Поставленная цель достигается тем, что в предложенное устройство введены реверсивный счетчик, распределитель импульсов, элемент И выдачи совпадений, элемент ИЛИ выдачи совпадений, элемент ИЛИ вычитания, элемент ИЛИ обнуления, элемент ИЛИ сброса реверсивного счетчика, элемент ИЛИ сброэлементы И са триггеров хранения числа, ИЛИ выдавыдачи . информации, элемент элементы И чи информации, элемент НЕ, ИЛИ запизаписи результата, элемент нулей, зел си результата, узел анализа анализа единиц, триггер несовпадений и эле36мент И несовпадений. Информационные входы устройства ерез элементы И выдачи информации иэлемент ИЛИвыдачи информации подключены к первому и через элемент НЕ ко второму входам узла сравнения, а также через элементы И записи результата и элемент ИЛИ записн результата к единичному входу триггера хранения каждого разряда числа, прямой вы ход которого подключен к информационному выходу устройства. Другие входы элементов И выдачи информации соединены с соответствующимн (1 - т) выходами распределителя импульсов, а выход узла сравнения подключен к суммирующему входу реверсивного счетчика, выходы разрядов которого через элемент И выдачи совпадений, другие входы которых соединены с соответствующими (т + I) -f (т + к) выходами распределителя импульсов, и через элемент-ИЛИ выдачи совпадений подключены к сравнивающему выходу устройства и в каждом разряде к инверсному входу узла анализа нулей, а,также к прямому входу узла знализа единиц, выход которого подключен к единичному входу триггера несовпадений, инверсный выход которого соединен с Первым входом элемента И несовпадений, ко второму входу которого под лючен соответствующий (гп -f -f к -f 1)-й вУход распределителя импульсов. Выходы элементов И несовпаденнй через элемент ИЛИ вычитания подсоединены к вычитающему в-оду {«версивного счетчика. Сравнивающие входы устройства подк-пючены к инверсному входу узла анализа единиц н к прямому входу узла анализа нулей, выход которого в каждом -разряде через элемент ИЛИ обнуления и элемент ИЛИ сброса реверсивного счетчика подсоединен ко входу начальной установкн реверсивного счетчика и к первому входу элемента ИЛИ сброса триггеров хранеи1 я 4HCJia, ко второму входу которого подключен выход (к + 1)-го разряда реверсивного счетчика, а к кулевым входам - выход элемента ИЛИ сброса триггеров хранения числа. Выход (к + + 1)-го разряда реверсивного счетчика подключен к выходу «брак устройства, -а вход начальной установки устройства - К другому входу элемента ИЛИ сброса реверсивного счетчика н в каждом разрядке - к «улевому йходу триггера несовпадений. Кроме того, (2т 4- к Ч- О-и выход распределителя импульсов подключен к вторым входам элементов И записн результата, .а вход распределителя импульсов - ко входу синхроимп гльсов устройства. На фиг. i и 2 представлена функциональная схема устройства. Предлагаемое устройство содержит узел 1 сравнения для определения .равенства двук п-разрядных двоичных чисел я в каждом разряде - элемент ИЛИ 2 выдачи информации, элемент НЕ 3, элементы И 4 выдачи ннформации, элемент ИЛИ. 5 записи результата, элемент И 6 записи результата, информационные входы 7 устройства; триггеры 8 хранения числа, информационные выходы 9 устройства, распределитель 10 импульсов. реверсивный счетчик II, элементы И 2 выдачи совпадений, элемент ИЛИ 13 выдачи совпадений и в каждом разряде -- узел 14 анализа нулей, узел 15 анализа , сравнивающий вход 16 устройства, триггер 17 несовпадений и элемент И 18 несовпадений, э.пемент ИЛИ 19 вычитания элемент ИЛИ 20 обнуления, элемент ИЛИ 21 сброса реверсивного счетчика, вход 22 начальной установки устройства, элемент ИЛИ 23 сброса триггеров хранения числа, выход 24 «брак устройства, сравнивающий выход 25 устройства и вход 26 синхроимпульсов устройства. В каждом разряде информационные входы 7 устройства через элементы И 4 выдачи информации и общий для них элемент ИЛИ 2 выдачи информации подключены к первому и через элемент НЕ 3 ко второму входам узла 1 сравнения, а через элементы И 6 записи результата и общий для них элемент ИЛИ 5 записи результата к единичному входу триггера 8 для хранения числа в каждом разряде. Прямой выход триггера 8 подсоединен к информационному выходу 9 устройства и к третьему входу узла 1 сравнения, а инверсный - к четвертому входу узла 1. сравнения. Выход узла I сравнеиня соединен с суммирующим входом счетчика 11, выходы разрядов которого через элемент И 12 выдачи совпадений и общий для них аиемевт ИЛИ 13 выдачи совпадений подключены к сравнивающему выходу 25 устройства, к инверсному входу узла 4 анализа нулей и к прямому входу узла 15 анализа единиц, выход которого подключен к единичному входу триггера J7 несовпаденкй. Инверсный выход триггера 7 несовпадений в Каждом разряде через элемент И 8 несовпаденнй и общий элеме гт 19 ИЛИ вычитания подсоединен к вычитающему входу счетчика 1. Выход узла 4 анализа нулей каждого разряда через общин элеме т ИЛИ 20 обнуления и элемент ИЛИ 2 сброса счетчика П. подключен ко входу начальной установки этого счетчика и к первому входу элемента ИЛИ 23 сброса триггеров хранения числа, ко второму входу которого подсоединен выход {к + 1)-го разряда счетчика 11, а выход элемента 23 - к нулевым входам триггеров хранения числа. Выход (к + )-го разряда счетчика П подключен . также к выходу 24 «брак устройства. Вход 22 начальной установки устройства подключен к другому входу элемента ИЛИ 21 сброса счет-, чика ПНЕ кансдом разряде - к нулевому входу триггера 17 несовпадений, а сравнивающие входы 16 устройства в каждом разряде - к прямому входу узла 14 анализа нулей и к инверсному входу узла 15 анализа единиц. Соответствующие выходы распределителя и.мпульсов, формирующего такты импульсов, следующих последовательно один за другнй, из последовательности синхроимпульсов, поступаю1цих на вход 26 устройства, лодключены в каждом разряде ко входам элементов И 4 выдачи информации, ко входам элементов И 6 записи результата, ко входу элемента И 18 несовпадений и ко входам соответствующих элементов И 2 выдачи совпадений каждого разряда счетчика 11.

Предлагаемое устройстпо работает совместно с гп аналогичными каналами с цедующим образом.

В исходном состоянии после прохождения сигнала начальной установки, подаваемого на вход 22 устройства, счетчик 11 и триггеры 17 находятся в нулевом состоянии, в триггерах 8 записано двоичное число, а на входы 7 поданы сигналы В|...Вя, от аналогичных устройств п-разрядным параллельным двоичным кодом.

При подаче на вход 26 синхроимпульсы преобразуются распределителем импульсов в последовательность, тактов i ч- (2. + к + 1).

По первому такту распределителя 0 импульсов п-разрядный двоичный код Bi через элемент И 4 и элемент ИЛИ 2 поступает на вход В и через элемент НЕ 3 на .вход В узла I сравнения. На входах А и А узла сравнения присутствует код, записанный в триггерах 8.

При равенстве двух кодов А н В„ поступающих на входы узла 1 сравнения, на выходе этого узла появляется сигнал сравнения, который поступает на суммирующий вход счетчика 11 и записывает единицу в младший разряд. По второму такту распределителя импульсов аналогично сравниваются коды В и А, при равенстве этих кодов, к содержимому счетчнка 11 прибавляется единица, а при иеравенстве кодов чисел содержимое счетчика I не изменяется.

По третьему такту распределителя импульсов сравниваются коды БЭ и А и т.д. пока не произойдет сравнение кодов всех чисел, поступающих на входы 7 устройства, с кодом числа А, хранящимся в триггерах 8.

Таким образом, в результате всех сравнений в счетчике 11 зафиксировано столько единнц, сколько раз код числа А сравнился с кодами В|...В„,. п-разрядных двоичных чисел, прнсутствующнми на входах 7 устройства. По такту ш распределителя импульсов попарное сравнение кодов заканчивается.

Минимальное число разрядов К счетчика I определяется из выражения

К ,

где К - ближайшее большее целое число;

т.- число кедов чисел, поступающих для сравнения на входы 7 устройства.

По тактам (т -f ) -f- (т -f к) распределителя импульсов содержимое счетчика i последовательно, начиная со старшего разряда, анализируется с одноименными разрядами кодов Bi...Brei, лоступаюш.йх на входы 16 устройства. При этом содержимое каждого разряда счетчика 11 по определенному такту поступает через элементы И 12 выдачи совпадений и элемент ИЛИ 13 выдачи совпадений на прямой вход узла 15 анализа единиц н на инверсный вход узла 14 анализа нулей для m разрядов, и на выход 25 устройства. Сигналы .со входов 16 устройства поступают на прямой вход узла 14 анализа нулей и инверсный вход узла 15 анализа единиц для каждого из m разрядов. Если в разряде счетчнка 1 i находился «О, а на вход 16 устройства поступил сигнал «1, то это свидетельствует о том, что число попарных сравнений и содержимое счетчика 11 не

являются наибольшим, н информация, находящаяся в триггерах 8 хранения числа, недостоверна. В этом случае на выходе узла 14 анализа нулей появляется сигнал, который через элемент ИЛИ 20 обнуления н через элемент ИЛИ 21 сброса обнуляет содержимое счетчика Пи через элемент ИЛИ 23 сброса сбрасывает в «нуль триггеры 8 хранения числа. Если в разряде счетчика 11 находилась «I, а на вход 16 устройства поступил Сигнал «О, то это условие Г1риводит к появлению сигнала на выходе узла 15 анализа единиц, который устанавливает в единичное состояние триггер 17 несовпадений.

Таким образом осуществляется анализ каждого разряда счетчика I и сигналов, поступающих на каждый вход 16.

По тактам (т - к + ) -- (2т -f к) распределителя импульсов на выходе элементов И 18 несовпадений в каждом разряде поочередно появляются сигналы, если триггер 17 остался в «нулевом состоянии, эти сигналы поступают через элемент ИЛИ 9 на вычитающий вход счетчика Я, и вычитаются «е.иницы из содрржнмого счетчика И .

содержимое счетчика И меньше, цем число триггеров 17 несовпадений, которые остались в «нулевом состоянии, то в результате вычитания устанавливается в единичное состояние (к ч- 1)ч°1 разряд счетчика 11, что свидетельствует о том, что число парных сравнений кодов чисел для данного устройства не является наибольшим из любого ряда чисел. При это.м сигнал с (к 4- 1)-го разряда счет-, чика 11 поступает на вь1ход 24 «брак устройства и через элемент ИЛИ 23 сбрасывает в «нуль триггеры 8 хранения числа. По такту (2т -f к) -f 1 открываются элементы И 6 и элемент ИЛИ 5 записи результата в каждом разряде, и в триггеры 8 хранения числа записывается достоверная информация с аналогичных устройств, поступающая на входы 7 устройства. На этом цикл выбора достоверной информации заканчивается.

Таким образом, введенные в каждый разряд устройства элементы И выдачи информации, элемент ИЛИ выдачи информации и элемент НЕ обеспечивают совместно с распределителем импульсов последовательную подачу параЛлельных кодов чисел на узел сравнения для поразрядного сравнения с кодом числа, запи. санным в триггерах хранения, а введение реверсивного счетчика обеспечивает накопление числа совпадений чисел и выборку наибольщего числа сравнении. Введенные в устройство элемент И выдачи совпадений, элемент ИЛИ выдачи совпадени и узлы анализа нулей и единиц позволякп совместно с распределителем импульсов гфовести анализ содержимого каждого разряда реверсивного счетчика с одноименнымиразрядами кодов, поступающих на сравнивающие входы устройства, и запомнить ЧИСЛО несовпадений в триггерах несовпадений. Введенный в каждый разряд элемент И несовоадений совместно с распределителем импульсов и узел вычитания обеспечивают определение наибольшего числа совпадеНИИ чисел, а введение э.юмснтов оонумсипя и c6pocii исключает выборку fieAocTOBOiiHoii информации. Введение в каждый разряд элементов И записи результата и элемента 11, III записи результата обеспечивает запись достоверной ииформации в триггеры хранения числа.

В результате предлагаемое устройство в отличие от известной с.хемы сравиения обеспечивает выборку достоверной информанин из любого ряда m чисел, представленных параллельными п-разрядными двоичными кодами, но результатам попарного сравнения каждого числа со всеми остальньгми и накопление чис.ча совпадений в реверсивном счетчике. При последующем анализе содержимого реверсивного счетчика выбирается больи1ее число сравнеинй, которое соответствует достоверной информании.

Формула изобретения

Устройство для определения достоверности информации, содержащее узел сравнения, триггеры хранения числа, прямой и инверсный выходы которых подключены к соответствующи.м входам узла сравнения, отличающееся тем, что, с целью иовьцнения точности работы, в него введены реверсивный счетчик, распределитель импу.чьсов, элемент И выдачи совпадений, элемент ИЛИ выдачи совпадений, элемент ИЛИ вычитания, элемент ИЛИ обнуления, элемент ИЛИ сброса реверсивного счетчика, элемент ИЛИ сброса триггеров хранения числа, элементы И выдачи информации, элемент ИЛИ выдачи информации, элемент НЕ, элементы И записи результата, элемент ИЛИ записи результата, узел анализа нулей, узел анализа единиц, триггер несовнадений и элемент И несовпадений; причем информационные входы устройства через элементы И выдачи информации и элемент ИЛИ выдачи информации подключены к первому и через элемент НЕ ко второму входам узла сравнения, а также через элементы И заниси результата и элемент Р1ЛИ записи результата к единично.му входу триггера хранения каждого разряда числа, прямой выход которого нодключен к информационному выходу устройства; при этом другие входы элементов И выдачи инфор.мации соединены с соответствующими (1 - m )-ми выходами распреде,|)пеля импульсов, а выход узла сравнения подк.лючеи к суммирующему входу реверсивного счетчика, р ыходы разрядов которого через элементы И выдачи совнаденнй, другие входы которых соединены с соответствующими (ш + 1);(т + к)-МП выходамн распределителя импульсов, и через элемент ИЛ-И выдачи совпадений подключены к сравнивающему выходу устройства и в каждом разряде к инверсному входу уз.па анализа ну.чей, а также к нрямому входу узла ана.чнза единиц, выход которого подключен к единичному входу триггера несовпаденнй, инверсный выход которого соединен с первым входом элемента И несовпадений, ко второму входу которого нодключен соответствующий (щ + к + 1)-й выход распределителя импульсов; а выходы элементов И несовпадений через элемент ИЛИ вычитания нодсоединеиы к вычитающему входу реверсивного счетчика; сравниваюн ие входы .устройства подключены к инверсному входу узла анализа едп; ниц и к пря.мому входу узла анализа нулей, выход которого в каждом разряде через элемент ИЛИ обнуления и элемент ИЛИ сброса реверсивного счетчика подсоединен ко входу начальной установки реверсивного счетчика и к первому входу элемента ИЛИ сброса триггеров хранения числа, ко второму входу которого подключеп выход (к + 1)-го разряда реверсивного счетчика, а к нулевым входам - выход элемента ИЛИ сброса триггеров хранения числа, выход (к + 1)-го разряда реверсивного счетчика подключен к выходу «брак устройства, а вход начальной установки устройства подключен к другому входу элемента ИЛИ сброса реверсивного счетчика и в каждом разряде к нулевому входу триггера несовпадений; кроме того, (2т + к + 1)-й выход распределителя импульсов подключен к вторым входам элементов И записи результата, а вход распределителя импульсов подсоединен ко,входу синхроимпульсов устройства.

Источники информации, принятые во внимание нри экспертизе:

1.Авторское свидетельство СССР № 443383, кл. G 06 F 7/02, 1971.2.Гаврилов Н. В. и др. Арифметическое устройство быстродействующих ЭЦВМ. М., «Советское радио, 1970, с. 242.

| название | год | авторы | номер документа |

|---|---|---|---|

| МОДУЛЬ ВВОДА-ВЫВОДА СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1991 |

|

RU2032201C1 |

| Система для управления экскаваторно-автомобильным комплексом | 1989 |

|

SU1647598A1 |

| УСТРОЙСТВО ВВОДА-ВЫВОДА ИНФОРМАЦИИ ДЛЯ СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1993 |

|

RU2042183C1 |

| Ассоциативное запоминающее устройство | 1987 |

|

SU1501163A1 |

| Устройство для формирования тестовой последовательности | 1984 |

|

SU1218389A1 |

| ЦИФРОВАЯ МАШИНА ДЛЯ ПОИСКА ИНФОРМАЦИИ | 1966 |

|

SU214201A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Устройство для упорядочивания чисел | 1981 |

|

SU1012239A1 |

| Устройство для циклового программного управления | 1986 |

|

SU1381432A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

Авторы

Даты

1978-06-05—Публикация

1975-11-06—Подача