1

Изобретение относится к аналоговой вычислительной технике, и может быть использовано в специализированных аналоговых вычислителях, контурах самонастройки, адаптивных системах, а также различных гибридных аналого-цифровых системах и преобразователях, контрольно-измерительных системах различного назначения.

Известно устройство аналоговой памяти 1, в котором используются элементы памяти и корректирующие цепи.

Иедостатком известного устройства является низкая точность работы.

Наиболее близким из известных по технической сущности к изобретению является аналоговое ЗУ 2, содержащее элемент памяти и корректирующую цепь, имеющую генератор, формирователь импульсов опроса и триггер, выход которого подключен ко входу управления. В этом устройстве корректирующая цепь имеет широтно-имнульсный модулятор, формирующий импульсы, относительная длительность которых пропорциональна подаваемому на его вход напряжению. Эти импульсы запускают генератор, фаза выходного сигнала которого в момент окончания импульса модулятора фиксируется с помощью формирователя импульсов опроса триггером. Узел управления формирует корректирующий сигнал с постоянной амплитудой и полярностью, определяемой состоянием триггера. В результате этого на выходе элемента памаяти устанавливается и поддерживается неограниченно долго напряжение, соответствующее определенному количеству импульсов генератора.

Недостатком известного устройства является низкая точность работы, гак как обеспечение высокой точности широтно-импульсного модулятора и управляемого генератора представляет собой достаточно сложную техническую задачу. Кроме того, релейность характеристики корректирующей цепи приводит к тому, что процессы в системе элемент памяти-корректирующая цепь носят автоколебательный характер. Кроме того, узел управления воздействует на элемент памяти постоянно, что также

20 снижает точность работы устройства.

Цель изобретения - повышение точности работы аналогового ЗУ.

Поставленная цель достигается тем, что в аналоговое ЗУ, содержащее элемент памяти, вход которого соединен с выходом коммутатора, выход элемента памяти подключен к выходу устройства, вход которого соединен с одним из входов коммутатора, блок управления, первый вход которого со3Q единен с одним из выходов триггера, формирователь импульсов и генератор опорных импульсов, введены двухтактный ннтегратор, источник эталонного напряжения и делитель частоты, вход которого соединен с выходом генератора опорных имнульсов, со вторым входом блока уиравления и с одним из входов триггера. Выход делителя частоты подключен к первому входу двухтактного интегратора, второй вход которого соединен с выходом элемента памяти. Третнй вход двухтактного интегратора подключен к выходу источника эталонного напряжения, а выход - ко входу формирователя импульсов, выход которого подсоединен к другому входу триггера и к третьему входу блока управления, выход которого соединен с другим входом коммутатора. Блок управления содержит последовательно соединенные переключатель и первый ключ, два источника разнополярного напряжения, выходы которых соответственно соединены со входами переключателя, последовательно включенные первую интегрирующую цепочку, второй и третий ключи, последовательно включенные вторую интегрирующую цепочку и. четвертый ключ и элемент НЕ, вход которого соединен с первым входом блока управления и управляющим входом четвертого ключа. Выход элемента НЕ соединен с управляющим входом второго ключа, выход которого соединен с выходом четвертого ключа. Управляющие входы первого ключа и переключателя соответственно соединены со вторым и третьим входами блока управления, выход которого подсоединен к третьего ключа.

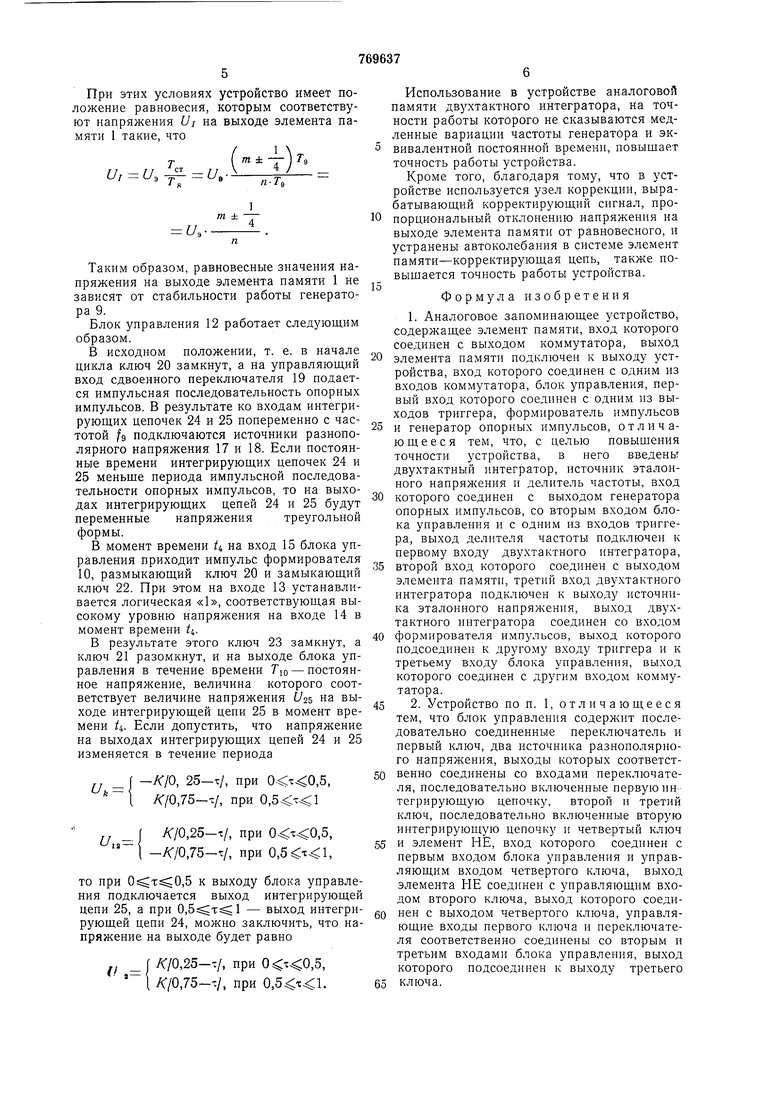

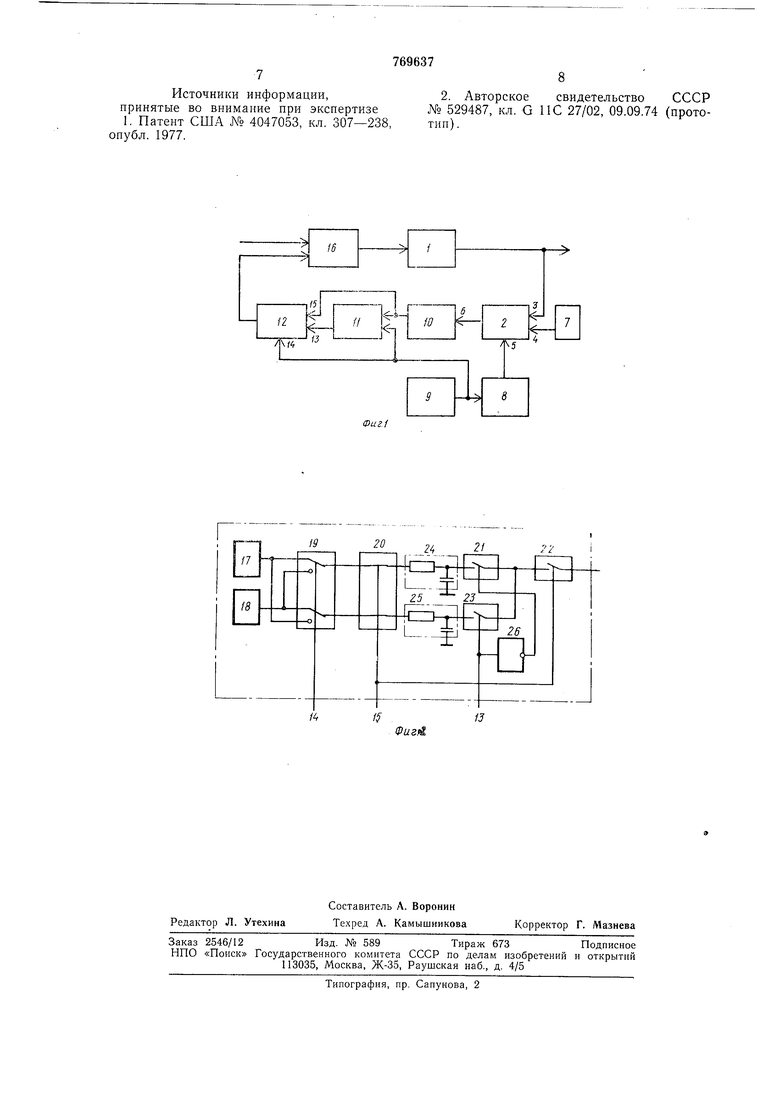

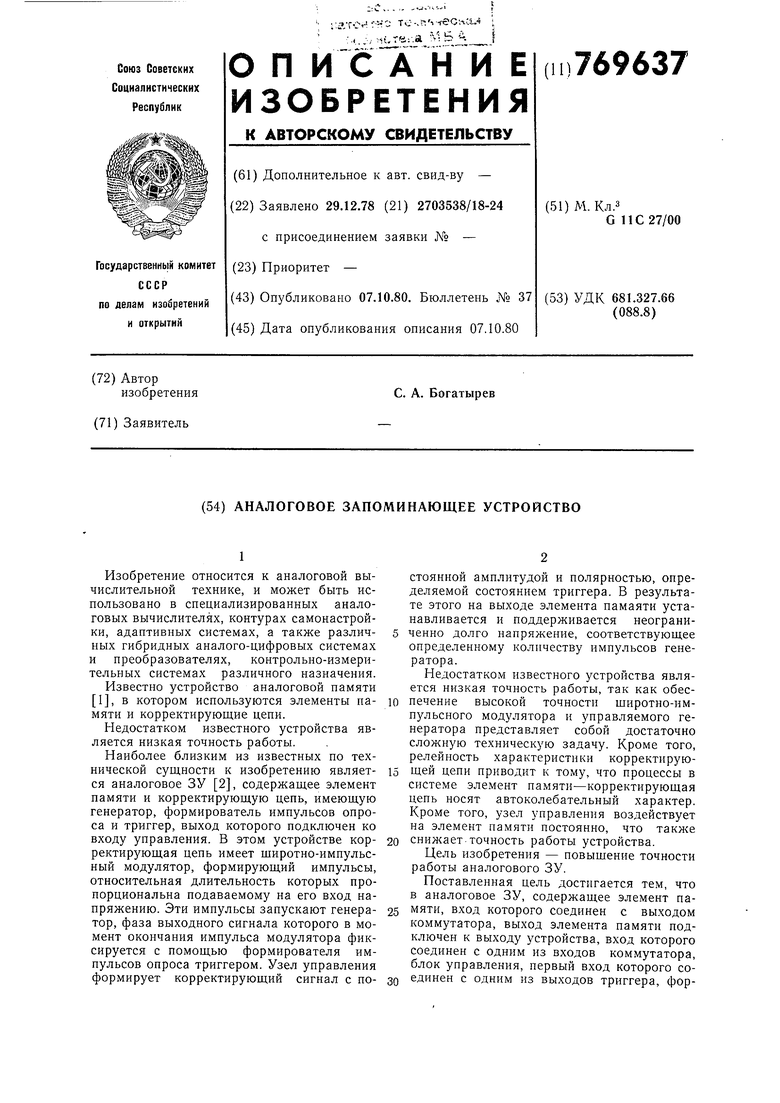

На фиг. 1 изображена функциональная схема предложенного устройства; на фиг. 2 - функциональная схема блока управления.

Устройство содержит элемент памяти 1, двухтактный интегратор 2 со входами 3-5 и выходом 6, источник эталонного напряжения 7, делитель частоты 8, генератор опорный импульсов 9, формирователь импульсов 10, триггер 11, блок управления 12 со входами 13-15 и коммутатор 16.

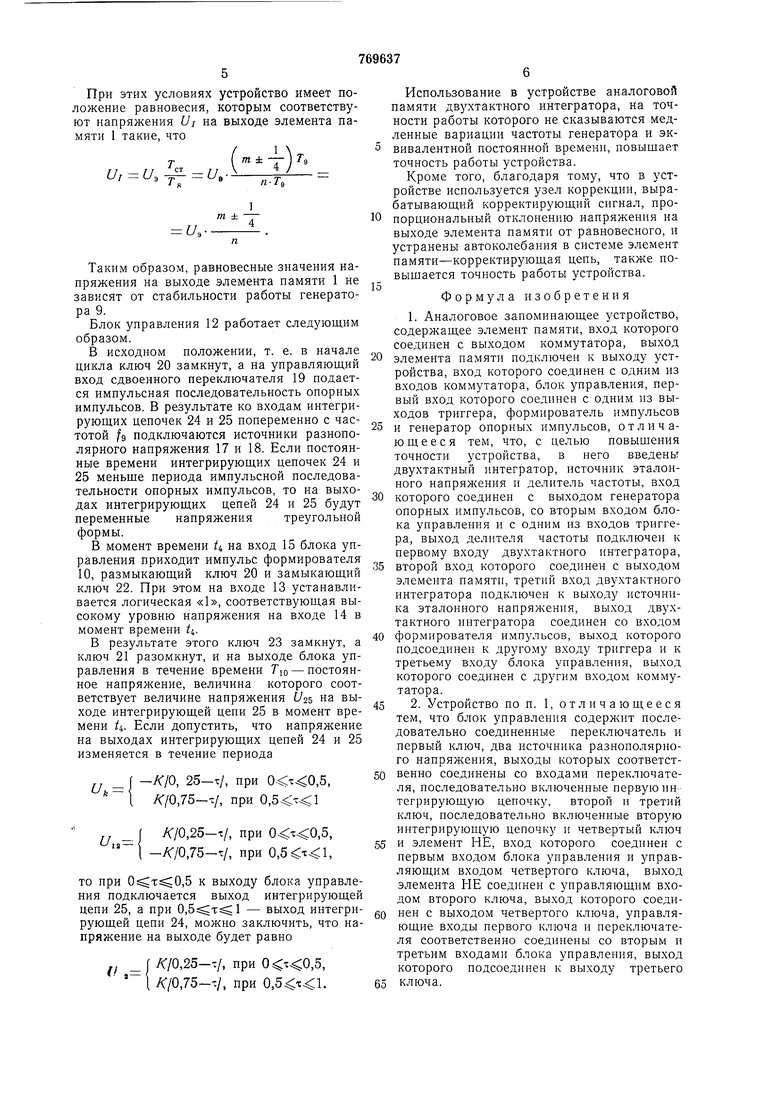

Блок управления содержит источники разнополярного напряжения 17 н 18, переключатель 19, ключи 20-23, интегрирующие цепочки 24 и 25 и элемент НЕ 26.

Работа устройства складывается из двух этапов.

На первом этапе (выборки) коммутатор 16 подключает напряженные, подлежащее запоминанию, ко входу элемента памяти 1.

На втором этапе (хранения) коммутатор 16 подключает к элементу памяти 1 выход блока управления 12. На этом этане устройство раобтает следующим образом. Опорные импульсы, имеющие длительность Тд И период следования 2Тд, с выхода генератора 9 подаются на вход делителя частоты 8, который формирует на выходе последовательность импульсов, длительность

которых , а период следования 278 (л - коэффициент деления делителя частоты 8).

Импульс с делителя частоты 8 появляется в момент времени /i и поступает на вход 5 интегратора 2.

Интегратор 2 работает таким образом, что он запускает формирователь импульсов 10 в момент 4, для которого выполняется условие

f f - т - т

4 1-2 - CTi -I ч

f/s

где Гст, -промежуток времени от момента окончания имплуьса делителя частоты 8 до момента 4; fy/, -напряжение на выходе элемента памяти 1 в интервале времени (/,, 4);

t/э -эталонное напряжение, подаваемое на вход 4 интегратора 2 с источником эталонного напряжения 7.

В результате этого на выходе формирователя импульсов 10 в момент /4 появляется импульс, длительность Гю которого постоянна. Этот импульс поступает на вход триггера 11 и устанавливает его в состояние логической «1, если в этот момент на другом его входе - высокий уровень напряжения, или состояние логического «О в нротивном случае. Опорные импульсы генератора 9, импульс формирователя 10 и сигнал с вы-хода триггера 11 поступают на блок управления 12. Блок управления 12 вырабатывает импульс коррекции, длительность которого постоянна и равна длительности импульса формирователя 10, а амплитуда Uiz и полярность являются функцией относительного сдвига по времени т переднего фронта импульса формирователя 10 (момент времени 4) и ближайщего предществующего начала периода последовательности импульсов генератора 9 (момент времени з), т. е.

„.

2. Г,

Эта функциональная зависимость выражается системой уравнений

I/(-(0,25--), при ,5, 1/C(0,75-T), при 0,,

где /С - постоянный коэффициент.

Импульс коррекции с блока управления 12, поступая на вход элемента.памяти 1, изменяет его выходное напряжение / на величину AL/I. Коэффициент К и длительность импульса коррекции Гю устанавливаются такими, чтобы новое значение Гст в следуюи ем цикле работы удовлетворяло условиям

Гст.

где т - целое положительное число, //Гст,-Гс..,.

При этих условиях устройство имеет положение равновесия, которым соответствуют напряжения Hi на выходе элемента памяти 1 такие, что

т ( Г) ст г 7 t у

и,и,,

П- Та

т ±

LJ,Таким образом, равновесные значения напряжения на выходе элемента памяти 1 не зависят от стабильности работы генератора 9.

Блок управления 12 работает следующим образом.

В исходном положении, т. е. в начале цикла ключ 20 замкнут, а на управляющий вход сдвоенного переключателя 19 подается импульсная последовательность опорных импульсов. В результате ко входам интегрирующих цепочек 24 и 25 попеременно с частотой fg подключаются источники разнополярного напряжения 17 и 18. Если постоянные времени интегрирующих цепочек 24 и 25 меньще периода импульсной последовательности опорных импульсов, то на выходах интегрирующих цепей 24 и 25 будут переменные напряжения треугольной формы.

В момент времени ti на вход 15 блока управления приходит импульс формирователя 10, размыкающий ключ 20 и замыкающий ключ 22. При этом на входе 13 устанавливается логическая «1, соответствующая высокому уровню напрял ения на входе 14 в момент времени t.

В результате этого ключ 23 замкнут, а ключ 21 разомкнут, и на выходе блока управления в течение времени Гю -постоянное напряжение, величина которого соответствует величине напряжения 1/25 на выходе интегрирующей цепи 25 в момент времени 4. Если допустить, что напряжение на выходах интегрирующих цепей 24 и 25 изменяется в течение периода

-К/О, 25-т/, при ,5, /(/0,75-т/, при 0,

/(/0,25-1/, при ,5, -К/0,, при 0,,

то при ,5 к выходу блока управления подключается выход интегрирующей цепи 25, а при 0, - выход интегрирующей цепи 24, можно заключить, что напряжение на выходе будет равно

fi ( /С/0,25-т/, при ,5, 1 /С/0,, при 0,.

Использование в устройстве аналоговой памяти двухтактного интегратора, на точности работы которого не сказываются медленные вариации частоты генератора и эквивалентной постоянной времени, повыщае.т точность работы устройства.

Кроме того, благодаря тому, что в устройстве используется узел коррекции, вырабатывающий корректирующий сигнал, пропорциональный отклонению напряжения на выходе элемента памяти от равновесного, и устранены автоколебания в системе элемент памяти-корректирующая цеиь, также повыщается точность работы устройства.

Формула изобретения

1. Аналоговое запоминающее устройство, содержащее элемент памяти, вход которого соединен с выходом коммутатора, выход

элемента памяти подключен к выходу устройства, вход которого соединен с одним из входов коммутатора, блок управления, первый вход которого соединен с одним из выходов триггера, формирователь импульсов

и генератор опорных импульсов, отличающееся тем, что, с целью повыщения точности устройства, в него введены двухтактный интегратор, источник эталонного напрял ения и делитель частоты, вход

которого соединен с выходом генератора опорных импульсов, со вторым входом блока управления и с одним из входов триггера, выход делителя частоты подключен к первому входу двухтактного интегратора,

второй вход которого соединен с выходом элемента памяти, третий вход двухтактного интегратора подключен к выходу источника эталонного напряжения, выход двухтактного интегратора соединен со входом

формирователя импульсов, выход которого подсоединен к другому входу триггера и к третьему входу блока управления, выход которого соединен с другим входом коммутатора.

2. Устройство по п. 1, отличающееся тем, что блок управления содержит последовательно соединенные переключатель и первый ключ, два источника разнополярного напряжения, выходы которых соответственно соединены со входами переключателя, последовательно включенные первую нн тегрирующую цепочку, второй и третий ключ, последовательно включенные вторую интегрирующую цепочку и четвертый ключ

и элемент НЕ, вход которого соединен с первым входом блока управления и управляющим входом четвертого ключа, выход элемента НЕ соединен с управляющим входом второго ключа, выход которого соедииен с выходом четвертого ключа, управляющие входы первого ключа и переключателя соответственно соединены со вторым и третьим входами блока управления, выход которого подсоединен к выходу третьего

ключа.

Источники информации, принятые во внимание при экспертизе 1. Патент США № 4047053, кл. 307-238, опубл. 1977.

2. Авторское свидетельство СССР № 529487, кл. G ПС 27/02, 09.09.74 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| Преобразователь тока в частоту | 1989 |

|

SU1695504A1 |

| Устройство для измерения температуры | 1984 |

|

SU1268970A1 |

| Аналого-цифровой преобразователь | 1990 |

|

SU1800616A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| УСТРОЙСТВО ДЛЯ ГЕОЭЛЕКТРИЧЕСКОЙ РАЗВЕДКИ | 1987 |

|

RU2018884C1 |

| Устройство для измерения отклонения сопротивления от заданного значения | 1986 |

|

SU1536322A1 |

| Преобразователь ток-частота с импульсной обратной связью | 1987 |

|

SU1552377A1 |

| ПРЕОБРАЗОВАТЕЛЬ НЕЭЛЕКТРИЧЕСКИХ ВЕЛИЧИН В ЦИФРОВОЙ КОД | 1991 |

|

RU2020745C1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1316089A1 |

Авторы

Даты

1980-10-07—Публикация

1978-12-29—Подача