(54) ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ КООРДИНАТ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой преобразователь координат | 1983 |

|

SU1163322A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1257638A1 |

| Цифровой преобразователь координат | 1979 |

|

SU842801A1 |

| Функциональный преобразователь кода угла и дальности | 1981 |

|

SU1008734A1 |

| Цифровой преобразователь координат | 1979 |

|

SU873239A1 |

| Синусно-косинусный функциональный преобразователь | 1981 |

|

SU970357A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1444958A1 |

| Устройство для симметрирования токов трехфазных четырехпроводных сетей | 1990 |

|

SU1758773A1 |

| Устройство для определения координат траектории скважины | 1980 |

|

SU909145A1 |

| Устройство для умножения | 1979 |

|

SU773622A1 |

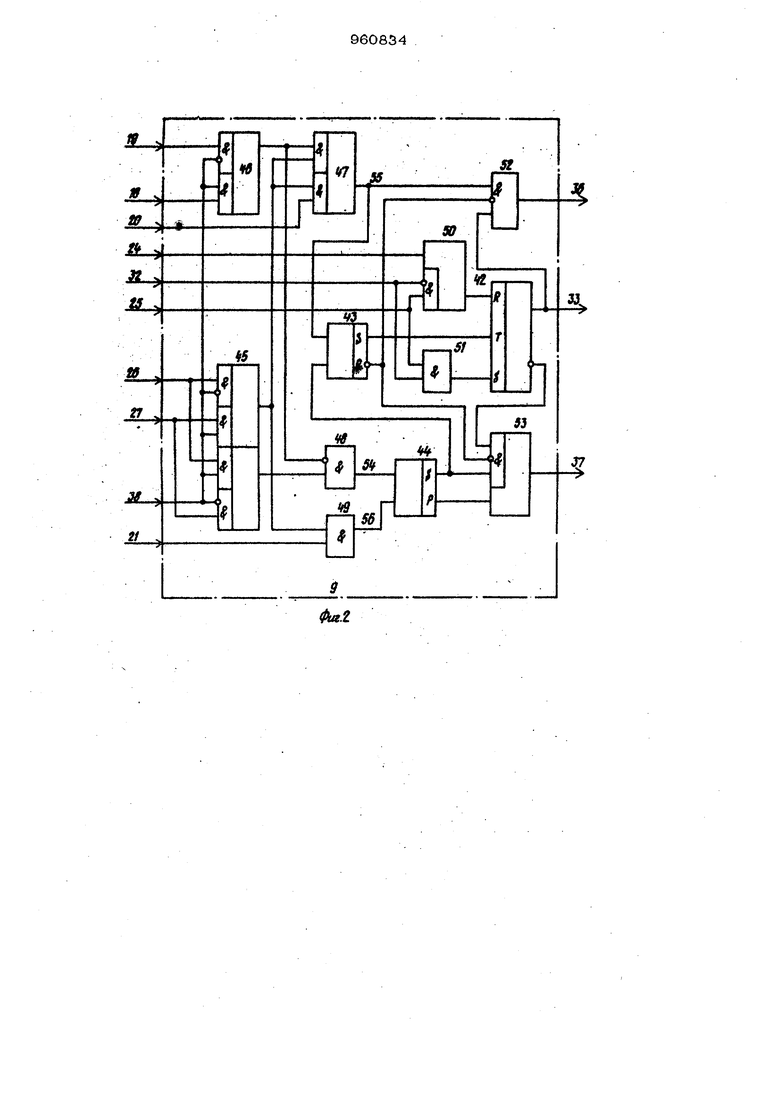

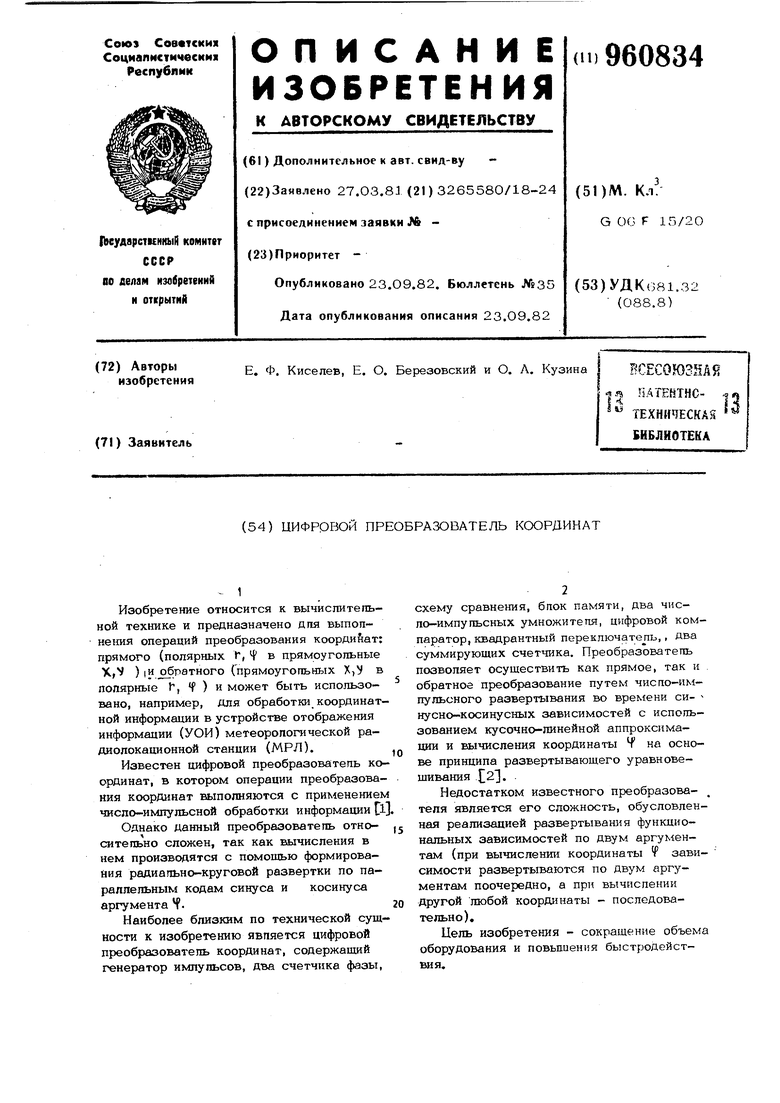

Изобретение относится к вычиспитепьной технике и предназначено дпя выпопне шя операций преобразования коордийат: прямого (полярных , Ч в прямоугольные X,V ) |И jo6paTHoro (прямоугольных X,V в полярные t, f ) и может быть использовано, например, для обработки координатной информации в устройстве отображения информации (УОИ) метеорологической радиолокационной станции (МРЛ). Известен цифровой преобразователь координат, в котором операции преобразования координат выполняются с применением число-импульсной обработки информации DОднако Данный преобразователь относительно сложен, так как вычисления в нем производятся с помощью формирования радиагПзНо-круговой развертки по параллельным кодам синуса и косинуса аргумента Н. Наиболее близким по технической сущности к изобретению является цифровой преобразователь координат, содержащий генератор импульсов, два счетчика фазы. схему сравнения, блок памяти, два число-импульсных умножитепя, цифровой компаратор, квадрантный переключатель,, Два суммирующих счетчика. Преобразователь позволяет осуществить как прямое, так и обратное преобразование путем число-импульсного развертывания во времени синусно-косинусных зависимостей с использованием кусочно-линейной аппроксимации и вычисления координаты f на основе принципа развертывающего уравновещивания . Недостатком известного преобразователя $юляется его сложность, обусловленная реализацией развертывания функциональных зависимостей по двум аргументам (при вычислении координаты Ф зависимости развертываются по двум аргументам поочередно, а при вычислении Другой любой координаты - последовательно). Цель изобретения - сокращение объема оборудования и повышения быстродействия. Поставленная цепь достигается тем, что в преобраэоватегаь, содержащий счетчик углов, коммутатор коДов, блок памяти угловых коэффициентов и два чиcлo импупьсных умножителя, причем счетный вход счетчика углов подключен к числоимпульсному входу преобразователя, установочный вход счетчика углов является первым установочным входом преобразо- ватепя, а информационные входы счетчика углов подключены к первой входной кодовой щине преобразователя, выходы счетчика углов подключены к адресным входам блока памяти угповых коэффициентов j; образуют первую выходную щину преобразователя, выход старшего разряда счетчика углов является первым управляющим выходом преобразователя, первая группа выходов блока памяти угловых ко- эффициентов подключена к кодовым входам первого число-импульсного умножитепя, а вторая - к кодовым входам второ го число-импульсного умножителя, число- импульсные входы которых подключены к число-импульсному входу преобразователя а установочные - к второму установочному входу преобразователя, к первой группе входов коммутатора кодов подключена первая входная кодовая шина, а ко.второй вторая входная кодовая щина, управляющий вход коммутатора является первым управляющим входом преобразователя, дополнительно введены коммутатор импульсов, третий и четвертый число-импупьсные умножители, число-импульсный сумматор, реверсивный счетчик координат и блок анализа знака, причем выход коммутатора кодов подключен к кодовым входам третьего число-импульсного умножителя и реверсивного счетчика координат, кодовые входы четвертого число-импульсного умножителя подключены к второй входной кодовой шине, установочные входы третьего и четвертого число-импульс ного умножителя соединены с вторым установочным входом преобразователя, число-импульсный вход третьего число-импульсного умножителя соединен с первым выходом коммутатора импульсов, числоимпульсный вход четвертого число-импульсного умножителя соединен с вторым выходом коь мутатора импульсов, выходы

третьего и четвертого число-импульсных умножителей соединены с первым и вторым число-импульсными информационными входами число-импульсного суммато- 55блока, первый и второй вход элемента 2ра соответственно, первый управляющий2И-2ИЛИ соединены с выходом эаемента

вход которого соединен с выхо- -ом млад-ИЛИ, третий вход - с четвертым входом

щего разряда коммутатора кодов, второй,бпока, а четвертый - с выходом первого

ИЛИ соединены с первым и вторым входом блока, а входы первого полусумматора - с третьим и четвертым входами третий, четвертый и пятый управляющие входы число-импульсного сумматора являются соответственно вторым, третьим, четвертым и пятым управляющими входами преобразователя, шестой управляющий вход число-импульсного сумматора подключен к первому выходу блока анализа знака, первый и второй входы которого соединены с четвертым и пятым управляющими входами преобразователя соответственно, третий и четвертый входы этого блока являются знаковыми входами преобразователя, второй выход блока анализа знака подключен к управляющему входу коммутатора импульсов, третий и четвертый выходы блока анализа знака являются знаковыми выходами преобразователя, третий и четвертый установочные входы преобразователя соединены с первым и вторым установочными входами число-импульсного сумматора соответственно и реверсивного счетчика координат, первый выход число-импульсного сумматора соединен с суммирующим входом, а вычитающим входом реверсивного счетчика координат, третий выход является выходом мпадшего разряда второй выходной кодовой шины, выходами старших разрядов которой являются выходы реверсивного счетчика координат, выход старшего разряда которого является вторым управл5пощим выходом преобразователя, выходы первого и второго число-импульсных умножителей соединены соответственно с первым и вторыкт входами коммутатора импульсов. Кроме того,коммутатор импульсов состоит из пвух элементов 2-2И-2ИЛИ, причем первые входы этих элементов являк тся, инверсными . и подключены к управляющему входу коммутатора, вторые входы этих элементов подключены к второму входу коммутатора, третьи входы - к управляющему входу коммутатора, четвертые входы - к первому входу коммутатора, выход первого элемента является первым выходом коммутатора, а второго - вторым. При этом блок анализа состоит из двух полусумматоров элемента ИЛИ и элемента 2-2И-2ИЛИ с инверсией по первому входу, причем входы элемента

5960834«

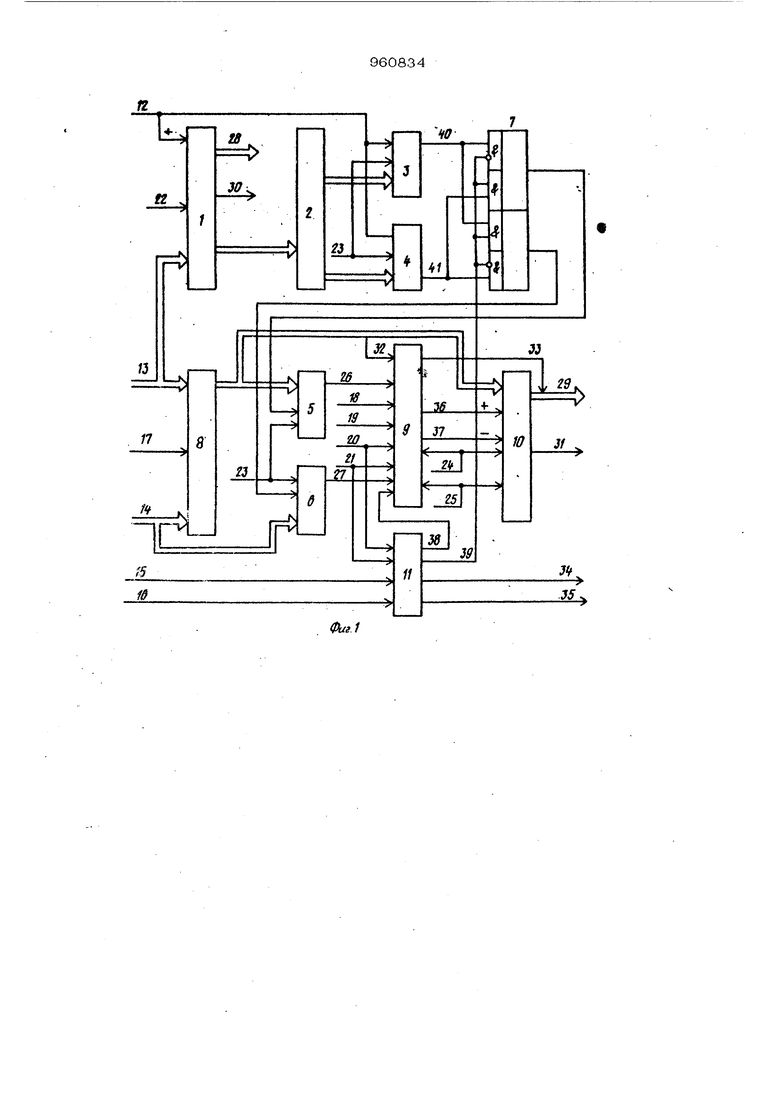

полусумматора, выход этого элементамы которого соединен с тактовым входом

подключен к первому выходу блока и триггера, прямой выход которого подкгаовому входу второго полусумматора, второй вход которого соединен с вторым входом блока, а выход является вторым, выходом блока, третий выход блока соединен с вы ходом первого полусумматора, четвертый выход блока соединен с его четвертым входом. Число-импульсный сумматор содержит два полусумматора, триггер, три эпемента 2-2И-2ИЛИ с инверсией по первому входу, элемент 2-2И-2ИЛИ, три элемента И, элемент ЗИ-2ИЛИ, элемент 2И2ИЛИ с инверсией по первому входу элемента И, элемент И с одним инверсным входом, причем первые и вторые входы первого, второго и третьего элементов 2-2И-2ИЛИ с инверсией по первому входу подключены к шестому управляющему входу сумматора, третий и четвертый вхо ды первого элемента 2-2И-2ИЛИ с инверсией по первому входу подключены к третьему и второму управляющему входу сумматора соответственно, третий и четвертый входы второго и третьего элемента 2-2И-2ИЛИ с инверсией по первому входу соединены с первым и вторым число-импульсными входами сумматора, выход первого элемента 2-2И-2ИЛИ с инверсией по первому входу соединен с первым входом элемента 2-2И-2ИЛИ и инверсным входом элемента И с одним инверсным входом, выход второго элемента 2-2И-2ИЛИ с инверсией по перв.ому входу соединен с вторым и третьим входом элемента 2-2И-2ИЛИ и первым входом первого элемента И, выход третьего элемента 2-2И-2ИЛИ с первым инверсным входом соединен с прямым входом элемента И с одним инверсным входом, выход которого соединен с первым входом первого полусумматора, ЕЫход суммы которого соединен с первым входом второго полусумматора и первым входом первого элемента ЗИ-2ИЛИ, выход этого элемента подключен к второму выходу число-импульсного сумматора, пятый управляющий вход сумматора соединен с вторым входом первого элемента И, выход которого соединен с вторым входом полусумматора, выход переноса которого соединен с вторым входом элемента ЗИ-2ИЛИ, четвертый управляющий вход число-импульсного сумматора соединен с четвертым входом элемента 2-2И- 2ИЛИ, выход которого соединен с первым входом второго элемента И и вторым вхо дом второго полусумматора, выход сумчен к второму входу второго элемента И и третьему выходу сумматора, а инверсный - к третьему входу элемента ЗИ2ИЛИ, выход инверсии переноса второго полусумматора соединен с четвертым входом элемента ЗИ-2ИЛИ и третьим входом второго элемента И; выход которого соединен с первым выходом число-импульсного сумматора, первый, второй и третий входы элемента 2И-2ИЛИ с первым инверсным входом подключены к первому управляющему, первому установочному и .второму установочному входам число-импульсного сумматора соо-кветственно, выход этого элемента соединен с входом установки нуля триггера, перьвый и второй входы третьего элемента И соединены с первым управляющим и вторым установочным входами число-импульсного сумматора соответственно, выход третьего элемента И подключен к входу установки единицы триггера. На фиг. 1 приведена структурная схема цифрового преобразователя координат; на фиг. 2- функциональная схема сумматора; на фиг. 3 - то же, блока анализа знака. Устройство содержит счетчик 1 углов, блок 2 памяти угловых коэффициентов, число-импульсные умножители 3-6, коммутатор 7 импульсов, коммутатор 8 йодов, число-импупьсный сумматор 9, реверсивный счетчик 1О координат, блок 11 анализа знака, число-иМпугшсный вход 12, кодовые щины 13 и 14, информационные входы 15 и 16, управляющие входы 1721, установочные входы 22-25, выходы 26 и 27 число-импульсных умножителей 5 и 6, выходные кодовые шины 28 и 29, импульсные управляющие выходы ЗО и 31, выход 32 младшего разряда кода коммутатора 8, разрядный выход 33 сумматора 9, информационные выходы 34 и 35, импульсные выходы 36 и 37 сумматора 9, управляющие выходы 38 и 39 логического блока 11 и выходы 40 и 41 умножителей 3 и 4 соответственно. Сумматор 9 содержит триггер 42, полусумматоры 43 и 44, коммутатор45 импульсов, комбинационные элементы 4653 и выходы 54-56 элементов 48, 47 и 49 соответственно. Блок 11 анализа знака содержит попусумматоры 57 и 58 и комбинационные iэлементы 59 и 60. 79608 На входы 17-21 поступают управляюише сигналы П17-П21 соответственно, на входы 22-25 - установочные импупьсы И22-И25, на шины 13 и 14 - коды функций Ф13 и Ф14, на информационные 5 15 и 16 - информационные сигналы Ф15 и Ф16, На выходах 26, 27, 36, 37, 40, 41, 54, 55 и 56 формируются чиспо-импупьсные коды функций Ф26, Ф27, Ф36, Ф37,10 Ф40, Ф41, Ф54, Ф55 и Ф56, на выходах 38 и 39 блока 11 - управпяюшие сигнапы П38 и П39. На выходных шинах 28 vi 29 формируются коды Ф28 и Ф29, на выходах 30 ts и 31 - выходные импупьсы ИЗО и И31, на информационных выходах 34 и 35 информационные сигнапы Ф34 и Ф35. В режиме прямого преобразования на шины 13 и 14 преобразователя подают- о ся коды функций -.Тг а на входЬ 15 и 16 - два старших раз- 25 ряда ( И+2)-разрядного кода координаты If ( - приведенный угоп вепичина ко , торого определяется И младшими разря дами кода Ч Вес старшего разряда ко- да Ч равен . В режиме обратного преобразования )х| ( а на входы 15 и 16 поступают знаковые разряды координат X,V соответственно. Работа преобразователя основана на воспроизведении функциональных зависимостей Ф40 и Ф41 некоторого аргумента О о методом кусочно-линей ной аппроксимации, для чего служат блок,2 памяти, содержащий значения угловых коэффициентов функций 51и oL и (1 -CO5of) для каждого участка аппроксимации, выбираемые по старшим разрядам кода аргумента oi, развертывающегося в счетчике 1 углов, и число-импульсные умножители 3 и 4, на выходах 40 и 41 которых вырабатываются функции Ф40 и Ф41 чиспр-импульсными кодами. 48 Обратное преобразование выпогняется на основе соотношений a-clMO-bф4 5.(3) (г-а-а-Ф41 ЪФ4о, (4) а прямое преобразование -; на основе соотношенийc|r:r-rф4 ; Ь-г-0)40, а(х(или}УО (или/xf;. функциональные зависимости Ф40 и Ф41, воспроизводимые за время развертки аргумента в счетчике 1, определяются пределами развертывания аргумента. При развертывании аргумента от О до с :: 1С|2. функции Ф40 и Ф41 определяются выражениями (ф40:- -С05с6 CJl4,S1rto(, а при развертывании аргумента от cL До максимального значения ( 7Г/2. ), отличаемого импульсом ИЗО переполнения счетчика 1, - выражениями вида (Ф4б-Со5с1 tO)4|-f-siK)ot. Соотношение (3), служащее для вычисления приведенного узла fpp реализуется методом последовательного приближения, т.е. поиском такого угла ci(t) Hnpi АЛЯ которого равенство (3) выполняется наиболее точно. ,В табл. 1 приьеДены начальные состояния счетчиков 1 и 10, значения переменных, а, Ь и конечные результаты вычислений (3)-(6) в зависимости от квадранта Ц и от режима работы, т.е. от того, вычисление какой из координат происходит. Логические сигналы П21-1, , , определяют режим вычисления if Г, X|V соответственно, а сигнал {иш ) - четный (If , W ) или нечетный (1 , III ) квадрант координаты ЧВ т.абп, 1 учтено, что при работе преобразоватепя в четном квадранте с выхо дов 40 и 41 снимаются функции аргумен та, дополнительного к исходному (заданному) значению что обуславливает смену значений переменных 011 t) и начат1ьных состояний счетчиков 1 и 1О. Коммутатор 7 импульсов служит для коммутации чиспо-импульсных кодов функ ций Ф40 и Ф41 на выходы умножителей 5 и 6 по управляющему сигналу П39, вырабатываемому блоком 11. Сумматор 9 предназначен дпя формирования по число-импульсным кодам Ф26 и Ф27 положительного чиспо-импульсного кода Ф55 и отрицательных число-импупьс ных кодов Ф54, и Ф56, а на основе их число-импульсных кодов Ф36 и Ф37, по сту пающих на суммирующий и вычитающий входы счетчика 10 соответственно. При этом выходной чиспо-импупьсный код Ф36 вырабатывается в crtyч формирования лишь кода Ф55, а код Ф37 - в случае формирования хотя бы одного из кодов Ф54 и Ф56. При одновременнс формировании кода Ф55 и хотя бы одного из кодов Ф54 и Ф56 выходные коды Ф36 и Ф37 не вырабатываются, Дпя формирования кодов Ф36 и Ф37 служат комбинационные элементы 43, 44, 52 и 53. Триггер 42 формирует на выходе 33 младший разряд выходного кода Ф29. Комбинационные элементы 45-49 служат для формирования кодов Ф54, Ф55 и Ф56 по кодам Ф26 и Ф27 и управляющим сигналам П18-П21 и П38, а комбинационные элементы бО и 51 - для установки начальных условий по импульсам И24 и И25. Блок 11 анализа знака предназначен для выработки информационных сигналов Ф34 и Ф35, логических сигналов П38 и П39 в гаобом режиме работы в соответствии с выражениями ® Ф 16(9) Ф35 Ф16;.(1О) П38(П20 V 021) Ф16 (П20 V П21) Ф35;(11) П39 П38®П21,(12) Цикл вычисления каждой из коораднат начинается с устыноьки счетчиков 1 и 10 в начальное состояние, определяемое табл.1, по импульсам установки И 22 И25. При с приходом тактовых импульсов по входу 12 в счетчике 1 происходит развертывание аргумента of число-импульсные коды функций Ф4О и Ф41 поступают на тактовые входы умножителей 5 и 6, на кодовые входы которых подаются коды О и Ь, причем на умножитель 5 код Q (или Ь) поступает через коммутатор 8, управляемый сигналом П17. Сумматор 9 вырабатывает числоимпульсные коды функций ФЗб и Ф37. Цикл вычисления заканчивается по импульсу И31 обнуления счетчика 1О. При этом Ф28 соответствует коду искомого значения Нпр первый и второй старшие разрядь кода Ч снимаются с выходов

ll96083412

34 и 35 соответственно на основе соот- угольной коордикаты -fc (или d ) выраженошений (9) и (10).кия (5) и (6). Знаковые разряды коорПри П2О-1 с приходом тактовых им- динат X и У вьфабатываются на выхопульсов по входу 12 в счетчике 1,гдв дах 34 и 35 соответственно на основе находится вычисленное значение , про- s выражений (9) и (1О). исходит развертка о до переполненияМакет предлагаемого преобразователя

счетчика 1 (ниработеи сигнала ИЗО),реализован иа ИС серии 133. СопоставПри этом в счетчике 10 находится кодпение затрат оборудования в корпусах

Ф29 искомой координаты Г. ,микросхем, проведенное с учетом разрядПри нулевом (ненулевом) начальном состоянии счетчика 10 и запрещении работы канала формирования Ф41 (Ф40 со счетчика 1О по импульсу ИЗО снимается код Ф29 первой (второй) прямоБлок памяти

Число-импульсный умножитель

6 разрядный

10 разрядныйЦифровой компаратор

Суммирующий счетчик

Коммутатор Коммутатор импульсов

Число-импульсный

сумматорСхема сравнения

Реверсивный счетчикПереключатель

квадрантов

Блок анализа знака

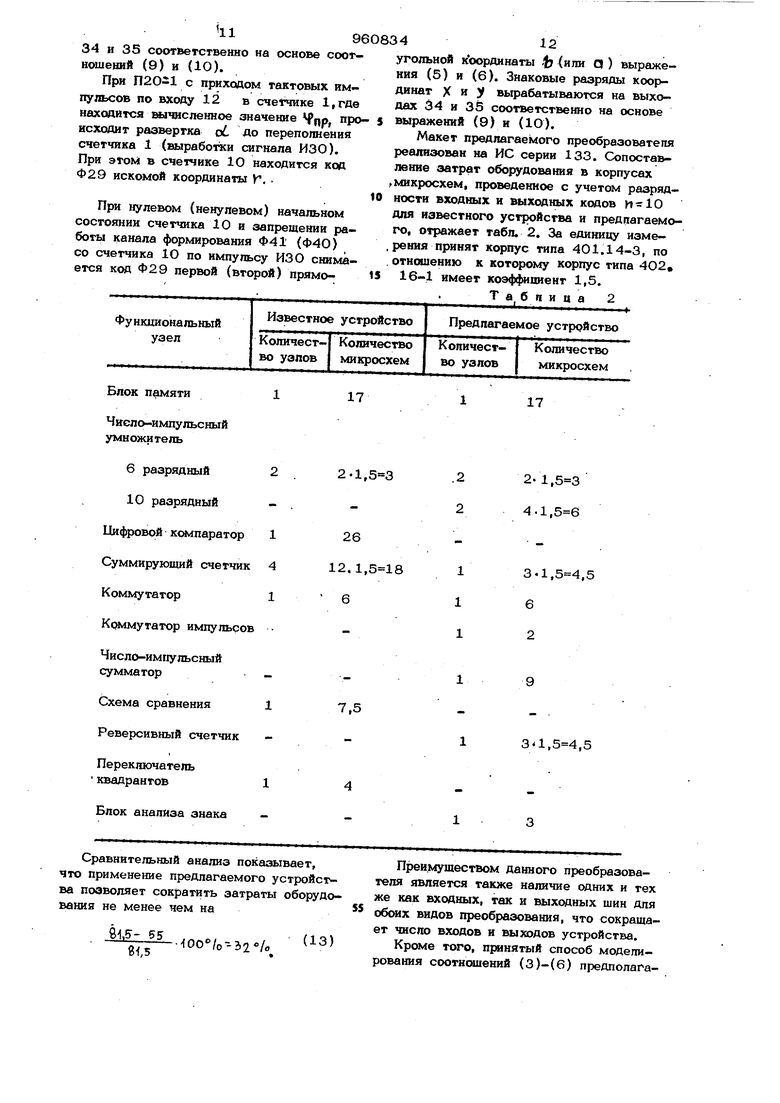

Сравнительный анализ показывает, что применение предлагаемого устройства позволяет сократить затраты оборудования не менее чем на

9ig- 55

(13)

оо 1о-ъг°1о Н

10 кости входных и выходных кодов И10

ДЛЯ известного устройства и предлагаемого, отражает табл. 2. За единицу изме- , рения принят корпус типа 401.14-3, по отношению к которому корпус типа 4О2, 16-1 имеет коэ4) 1,5.

Табпииа 2

17

2-1, 4-1,

3«1,,5

6

2

31,,5

Преи.муществом данного преобразователя является также наличие одних и тех же как входных, так и выходных шин для обсжх видов преобразования, что сокращает число входов и выходов устройства.

Кроме того, принятый способ моделирования соотнощений (З)-(в) предполагает параллельное формирование суммируемых чиспо-импульсных кодов, в то время как в известном устройстве вьгаис ление соотношений, аналогичных {3)-(6), происходит с применением поочередной $ развертки по двум аргументам, что обуславливает длительность преобразования не менее чем в два раза большую, чем в предлагаемом устройстве. Техникр-экономический эффект изобрё- 10 тения заключается в том, что предлагаемое устройство проще известного и име ет примерно в два раза большее быстродействие. . Формула изобретения 1. Цифровой преобразователь координат, содержаишй счетчик углов, коммута- зд тор кодов, блок памяти угловых коэффициентов и два чиспо-импульсных умножителя-, причем счетный вход счетчика yr-i. лов подключен к число-импульсн(.1у входу преобразователя, установочный вход счетчика углов является первым устано вочным входом преобразователя, а информационные входы счетчика углов подключены к первой входной кодовой шине преобразователя, выходы счетчика углов под- jg ключены к адресным входам блока памяти угловых коэффициентов и образуют пер вую выходную шину преобразователя, выход старшего разряда счетчика углов является перылм управляюиШм выходом преобразователя, первая группа выходов блока памяти угловых коэффициентов подключена к кодовым входам первого число импупьсного умножителя, а вторая - к кодовым входам второго число-импульсно го умножителя fчисло-импульсные входы которых подключены к число-импульсному входу преобразователя, а установочные входы - к второму установочному входу преобразователя, к первой группа входов коммутатора кодов подключена первая входная кодовая шина, а ко второй - вто рая входная кодовая шина, управпяющий вход коммутатора является первым управпяюишм входом преобразователя, от личающийся тем, что, с целью сокращения объема оборудования и повышения быстродействия преобразователя, в него введены коммутатор импульсов, третий, четвертый число-импульсные умножитепи, число-импульсный сумматор, реверсивный счетчик координат и блок анализа зиака причем выход коммутатора кодов подклю1чен к кодовым входам тре1$2S тьего числОЯимпульсного умножителя и реверсивного счетчика координат, кодовые входы четвертого чиспо-импупьсного умножителя подключены к второй входной кодовой шине, установочные входы тре i тьего и четвертого число-имг пьсных умножителей соединены с вторым установочным входом преобразователя, числоимпульсный вход третьего чиспо-импупьсного умножителя соединен с первым выходом коммутатора импульсов, число-импульсный вход четвертого число-импульсного умножителя соединен с вторым выходом коммутатора импульсов, выходы третьего и четвертого число-импульсных умножителей соединены с первым-и вторым число-импульсными информационными входами сумматора соответственно, первый управляющий вход которого соединен с выходом младшего разряда коммутатора кедов, второй, третий, четвертый и пятый управляющие входы чиспо-импупьсного сумматора являются соответственно вторым, третьим, четвертым и пятым уп- равлякшими входами преобразователя, шестой управляющий вход сука атора подключен к первому выходу блока анализа знака, первый и второй входы которого соединены с четвертым и пятым уп- равляющими входами преобразователя соответственно, третий и четвертый входы ЭТОГО блока являются знаковыми входами преобразователя, второй выход блока анализа знака подключен к управпяющему входу коммутатора импупьсов, третий и четвертый выходы блока анализа знака являются знаковыми выходами преобрхазо- вателя, третий и четвертый установочные входы преобразователя соединены с первым и вторым установочными входами число-импульсного сумматора соответственно и реверсивного счетчика координатпервый выход число-импупьсного сумматора соединен с суммирующим входом реверсивного счетчика координат, а второй- с вычитающим, третий выход является выходом младшего разряда второй выходной кодовой шины, выходами старших разрядов которой являются выходы реверсивного счетчика координат, выход старшего разряда которого является вторым управляюшим выходом преобразователя, выходы первого и второго число-импульсных умножителей соединены соответственно с первым и вторым входами коммутатора импупьсов. 2, Преобразователь по п. 1, о т л и чающийся тем, что коммутатор импульсов состоит из двух элементов 22И-2ИЛИ, причем первые входы элементов 2-2И-2ИЛИ являются инверсными и подключены к управляющему входу коммутатора, вторые входы элементов 2-2И2 ИЛИ подключены к второму входу коммутатора, третьи входы - к управляющему входу коммутатора, четвертые входык первому входу коммутатора, выход первого элемента 2-2И-2ИЛИ является первым выходом коммутатора, а второго вторым.

этого элемента подключен к первому выходу блока и первому входу второго полусумматора, второй вход которого соединен с вторым входом блока, а выход является вторым выходом блока, третий выход блока соединен с выходом первого по лусумматора, четвертьгй вьрсод блока соединен с его четвертым входом.

4,Преобразователь по п. 1, о т л и чающийся тем, что чис по-импу льеный сумматор содержит два полусуммато ра, триггер, три элемента 2-2И-2ИЛИ с инверсией по первому входу, эпемент 22И-2ИЛИ, три элемента И, элемент ЗИ2ИЛИ, элемент 2И-2ИЛИ с первым инверсным входом элемента И, элемент И с одним инверсным входом, причем первые и вторые входы первого, второго и третьего элементов 2-2И-2ИЛИ с инверсией по nepBcsviy входу подключены к щес то управляющему входу сумматора, третий и четвертый входы первого элемента 2-2И-2ИЛИ с инверсией по первому входу подключены к третьему и второму управляющему входу сумматора соответственно, трнэтйй и четвертый вхсжш второго и третьего элемента 2-2И : 2ИЛИ с инверсией по первому входу : соединены с первым и вторым число-импульсными входами сумматора, выход пер вого элемента 2-2И-2ИЛИ с инверсией по первому входу соединен с первым вхо

дом эпемеЬта 2-2И-2ИЛИ и инверсным входом элемента И с одним инберсным входом, выход второго элемента 2-2И2ИЛИ с инверсией по первому входу соединен с вторым и третьим входом элемен та 2-2И-2ИЛИ и первым входом первого элемента И, выход третьего элемента 2- 2И-2ИЛИ с инверсией по первому входу соединен с прямым входом элемента И с одним инверсным входом выход которого соединен с первьхм входом первого по лусумматора, выход суммы которого соединен с первым входом второго полусумматора и первым входом первого элемента ЗИ-2ИЛИ, выход этого элемента подключен к второму выходу сумматора, пятый управляющий вход сумматора соединен с вторым входом первого элемента И, выход которого соединен с вторым входом полусумматора, выход переноса которого соединен с вторым входом элемента ЗИ-2ИЛИ, четвертый управляющий вход сумматора соединен с четвертым входом элемента 2-2И-2ИЛИ, выход которого соединен с першз1м входом второго элемента И и вторым входом второго полусумматора, та)1ход суммы которого соединен с тактовым выходом триггера, прямой выход которого подключен к второму входу второго элемента И и тре тьему выходу сумматора, а инверсный к третьему входу элемента ЗИ-2ИЛИ, выход инверсии переноса второго полусумматора соединен с четвертым входом элемента ЗИ-2ИЛИ и третьим входом Второго элемента И, выход которого соединен с пераым выходом сумматора, пер- вьтй, второй и третий входы элемента 2И2ИЛИс первым инверсным входом подключены к первому, управляющему, первому установочному и второму установочному входам сумматора соответственно, выход этого элемента соединен с входом установки нуля триггера, первый и второй входы третьего элемента И соединены с первым управляющим и вторым установочным входами сумматора соответственно, выход третьего элемента И подключен к входу установки единицы триггера. Источники информации, принятые во внимание при экспертизе 1; Авторское свидетельство СССР № 742944, кл. G Об F 15/20, 1980. 2. Авторское свидетельство СССР по заявке № 2540О11/18-24, кп. G 06 F 7/38, 1979 (прототип).

Фиг.д

Авторы

Даты

1982-09-23—Публикация

1981-03-27—Подача