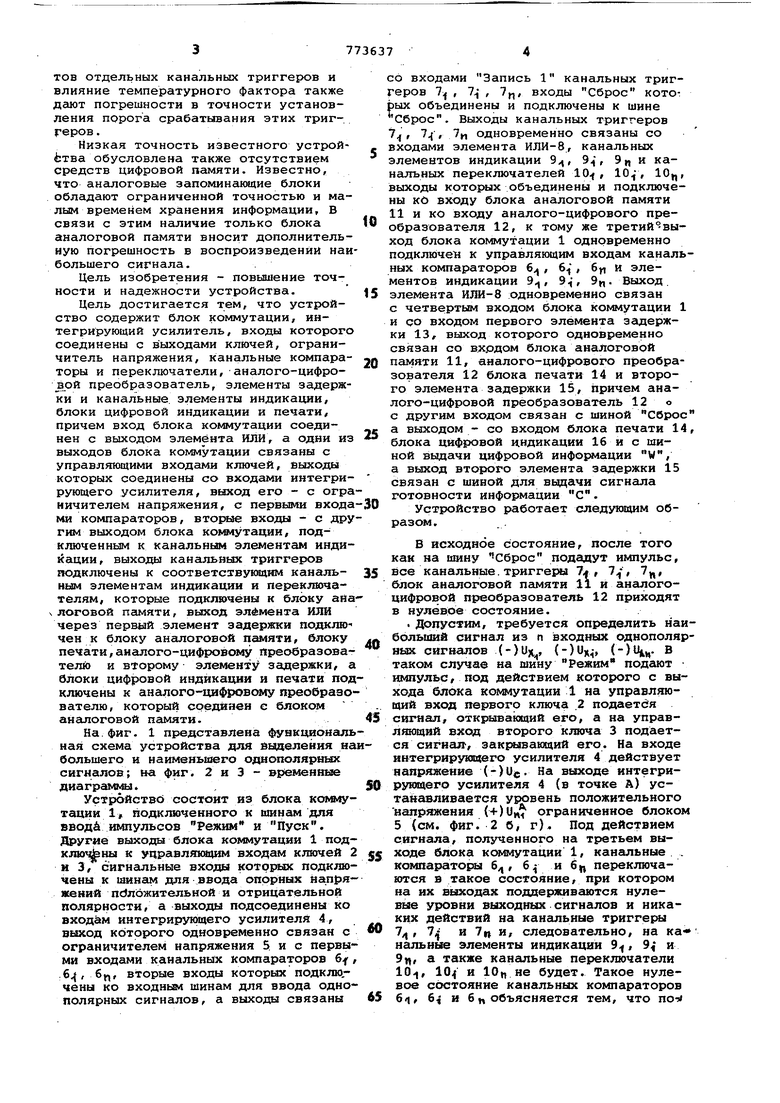

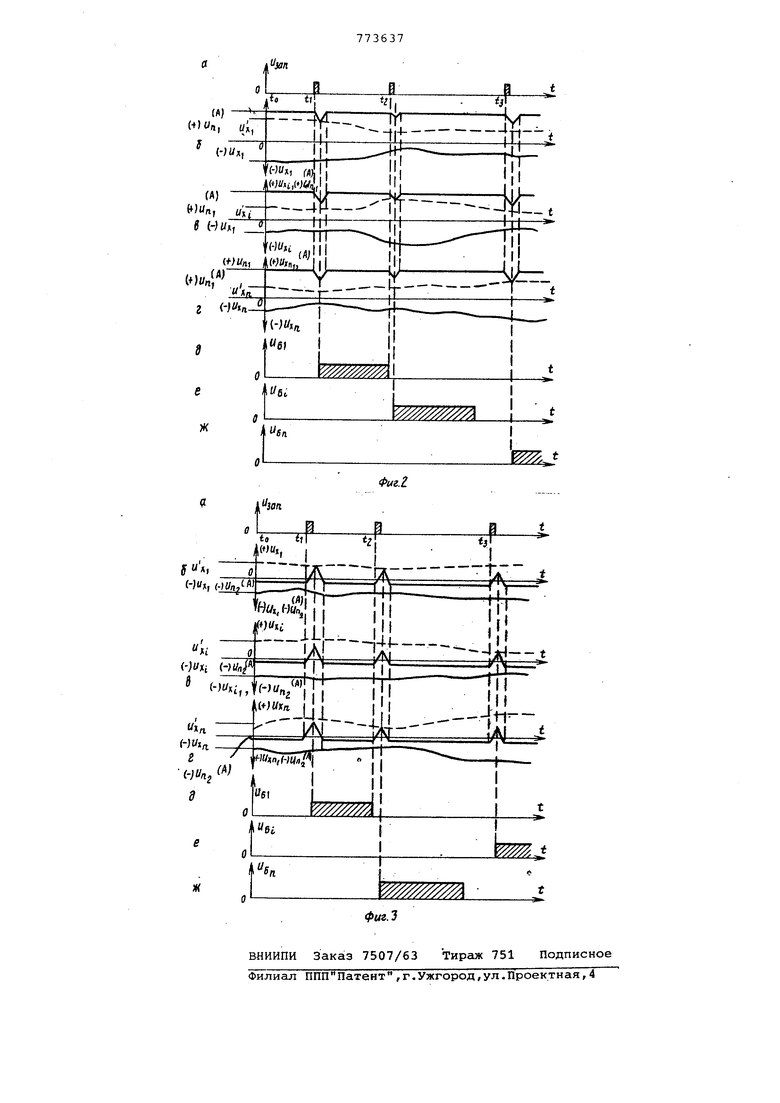

(54) УСТРОЙСТВО ДЛЯ ВЫДЕЛЕНИЯ НАИБОЛЬШЕГО И НАИМЕНЬШЕГО ОДНОПОЛЯРНЫХ СИГНАЛОВ Изобретение относится к вычислите.пьной технике и может быть использовано в различных информационных и вычислительных комплексах, а также в отдельных системах автоматики. Известны устройства для определения максимальных значений D-lОднако известные устройства харак теризуются недостаточной точностью и надежностью работы. Наиболее близким техническим реше нием является устройство для определения и запоминания наибольшего значения, содержащее блок выделения наи большего значения, аналоговой запомийающий блок, ключи, формирователи, триггеры, канальные триггеры, а также логические схемы ИЛИ, причем выходы формирователей в каждом из кана.пов подключены к единичныг. входам канальных триггеров, выход каждого из них соединен с соответствующим входом первой схемы ИЛИ, ее выход подключен к единичному входу первого триггера, нулевой выход которого соединен с управляющим входом первого ключа, выход первой схемы ИЛИ подключен к первому входу второй схемы ИЛИ, выход которой соединен с нулевым входом второго триггера, к единичному входу которого подключена клемма пуска, единичный выход второго триггера соединен с управляющими входами входных ключей всех каналов; ко второму входу второй схемы ИЛИ подключена клемма исходного положения, соединенная с нулевыми входами канальных триггеров и первого триггера, а также с управляющим входом аналогового запоминающего блока Недостатками известного устройства являются низкая точность и надеж-ность его, обусловленные наличием п-формирователей (интеграторов) выходных напряжений, изменяющихся по экспоненциальному закону в зависимости от величины входных сигналов (и , и 2 ... и). В таких случаях разброс параметров элементов отдельных формирователей и влияние изменения температуры окружающей среды на них (особенно при использовании полупроводниковых элементов) дают значительные погрешности в воспроизведении экспоненциальных напряжений на выходах формирователей. В результате можно получить, п-ое количество неточных значений экспоненциальных сигналов на выходах.п-формирователей. Кроме того, разброс параметров элемен тов отдельных канальных триггеров и влияние температурного фактора также дают погрешности в точности установления порога срабатывания этих триггеров . Низкая точность известного устройётва обусловлена также отсутствием средств цифровой памяти. Известно, что ансшоговые запоминающие блоки обладают ограниченной точностью и малым временем хранения информации, В связи с этим наличие только блока аналоговой памяти вносит дополнительную погрешность в воспроизведении наи большего сигнала. Цель изобретения - повышение точности и надежности устройства. Цель достигается тем, что устройство содержит блок коммутации, интегрирующий усилитель, входы которого соединены с выходами ключей, ограничитель напряжения, канальные ксмпараторы и переключатели, аналого-цифродой преобразователь, элементы задержки и канальные элементы индикации, блоки цифровой индикации и печати, причем вход блока коммутации соединен с выходом элемента ИЛИ, а одни из выходов блока колмутации связаны с управляпощими входами ключей, выходы которых соединены со входами интегрирующего усилителя, выход его - с огра ничителем напряжения, с первыми входа ми компараторов, втораае входы - с дру гим выходом блока коммутации, подключенным к канальным элементам индикации, выходы канальных триггеров рюдключены к соответствунмднм канальным элементам индикации и переключателям, которые подключены к блоку ана ч логовой памяти, выход элемента ИЛИ через первый элемент задержки подклю чен к блоку ансшоговой памяти, блоку печати,аналого-цифровому преобразова телю и второму элементу задержки, блоки цифровой индикации и печати под ключены к аналого-цифровому преобразо вателю, который соединен с блоком аналоговой пс1мяти. На.фиг. 1 представлена функционал ная схема устройства для йьаделения н большего и наименьшего однополярыых сигмалоа; на фиг. 2 и 3 - времеишю диаграммы. , Устройство состоит из блока тации 1, подключенного к шинам для вводи импульсов Режим и Пуск. Другие выходы блока коммутации 1 под к уцравлянщим входам ключей и 3, сигнальные входы которьЕК подклю чены к шинам для ввода опорных напря жений пблбжительной и отрицательной полярности, а выходы подсоединены ко входам интегрирующего усилителя 4, выход которого одновременно связан с ограничителем напряжения 5 и с первы ми входами канальных компараторов 6f .6, б, вторые входы которых подклю,чены ко входньвл шинам для ввода одно полярных сигналов, а выходы связаны о входами Запись 1 канальных триггеров 7;| , , 7„, входы Сброс котоых объединены и подключены к шине Сброс. Выходы канальных триггеров 7, 7, 7н одновременно связаны со входами элемента ИЛИ-8, канальных элементов индикации 9, 9, 9 и каНс1льных переключателей Ю , 10, 10„, выходы которых объединены и подключены ко входу блока аналоговой памяти 11 и ко входу аналого-цифрового преобразователя 12, к тому же третий°выход блока коммутации 1 одновременно подключен к управляющим входам канальных компараторов J , , Ь и элементов индикации 9, , 9 Выход, элемента ИЛИ-8 одновременно связан с четвертым входом блока коммутации 1 и со входом первого элемента задержки 13, выход которого одновременно связан со вхрдом блока аналоговой памяти 11, аналого-цифрового преобразователя 12 блока печати 14 и второго элемента задержки 15, причем аналого-цифровой преобразователь 12 о с другим входом связан с шиной Сброс а выходом - со входом блока печати 14, блока цифровой индикации 16 и с шиной вьвдачи цифровой информации W, а выход второго элемента задержки 15 связан с шиной для вьщачи сигнала готовности информации С. Устройство работает следующим образом. . В исходное состояние, после того как на шину Сброс подадут импульс, все канальные, триггер 7, , 7,,, блок аналоговой памяти 11 и аналогоцифровой преобразователь 12 приходят в нулевое состояние. . Допустим, требуется определить наибольший сигнал из п входных однополярныас сигналов (-)Uj, (-)Ux, )Ц1нтаком случае на шину Режим подают импульс, под действием которого с выхода блока коммутации 1 на управляющий вход первого ключа .2 подаетдя сигнал, открывающий его, а на управляющий вхсю второго ключа 3 подается сигнал , закрывающий его. На входе интегрирующего усилителя 4 действует напряжение (-)Ue. На выходе интегрируняцего усилителя 4 (в точке А) устанавливается уровень положительного вапряжения (+) ограниченное блоком 5 (см. фиг. 2 б, г). Под действием сигнала, полученного на третьем выходе блока кс мутации 1, канальные . компараторы 6, 6 и 6 ц переключаются в такое состояние, при котором на их выходах поддерживаются нулевые уровни выходных сигналов и никаких действий на кансшьные триггеры 7у( , 7;j и 7It и, следовательно, на ка нальные элементы индикации 9, 9{ и Э, а также канальные переключатели 10, 101 и lOtf не будет. Такое нулевое состояние канальных компараторов 6ц, 6 и 6 п объясняется тем, что поч

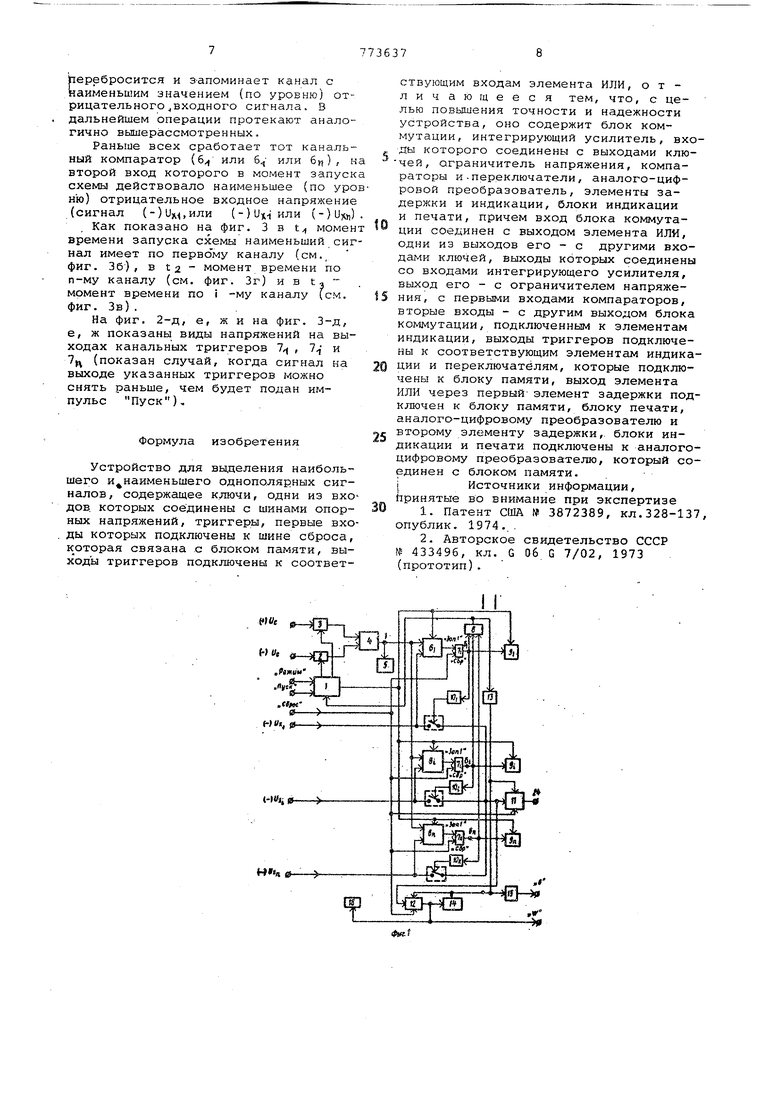

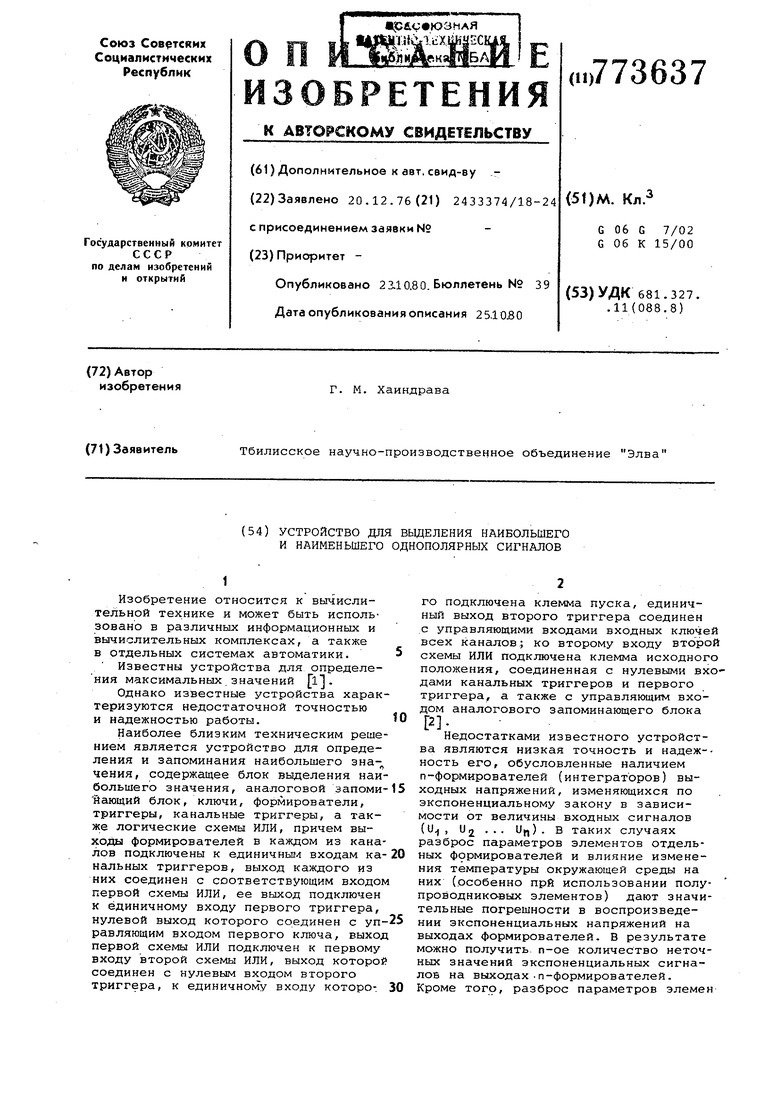

данный ;на их первые входы с выхода интегрирующего усилителя 4 уровень напряжения (+)U превосходит максимально возможное значение входных отрицательных напряжений (-) U, (-) Ux и (-)UXKI, действующих «а вторые входы канальных компараторов б, и бц, поэтому они находятся в закрытом состоянии. Допустим в t(момент времени) (см. фиг. 2а) через шину Пус подали импульс, который, воздействуя на блок коммутации 1 меняет его на .первом и втором выходах уровней напряжений на противоположные, в результате первый ключ 2 закрывается, а второй 3 открывается и на вход интегрирующего усилителя 4 начйет действовать (+)Uc.Ha выходе интегрирующего усилителя 4 положительное напряжение ( + )U||J) начнет линейно уменьшаться (см. ц - момент времени на фиг. 2 б,в,г). В момент равенства на входах канальных компараторов 6, бц и 6 напряжений (+)и (t) полученных на выходе интегрирукядего усилителя 4, с одним из IT входных отрицательный напряжений (-) U, или (-) Uxi или (-)и) на выходе одного из

канальных компараторов (6-f, или 6f или ) образуется импульс, под дей-ствием которого соответствующий канальный триггер перебросится и запоминает канал с наибольшим эначени, ем (по уровню) отрицательного входного сигнала. С выхода сработанного канального триггера сигнгш, соответствующий логической единице с одной стороны через логическую схему ИЛИ-8 подается на третий вход блока коммутации 1. В результате этого снова меняются состояния на его первом и вто ром выходах и интегрирующий усилитель 4 приходит в исходное состояние (см. фиг. 26,в,г). С другой стороны срабатывает соответствующий канёшьный элемент индикации 9, 9«{, 9ц и.канальный-переключатель 10, , 10. Последнее замыкает свой нормально открытый контакт и наибольший по уровню входной отрицательный сигнал одновременно подается на вход блоканалоговой памяти 11 и аналого-цифврвого преобразователя 12.

С выхода элемента ИЛИ-8 импульс через первый элемент задержки 13 (время задержки равно или больше времени переключения канального переключателя) подается на управлякицие входы блока аналоговой памяти 11, аналогоцифрового преобразователя 12 и блока печати 14, а также на вход второго элемента задержки 15 (время згщержки равно или больше времени преобразования аналогового сигнала в цифровой код).

Как следует из вышеизложенного, раньше всех сработает тот канальный компаратор (б илиб | или бу,) , на втором входе которого в момент эапуска схемы действовало наибольшее (по уровню) отрицательное входное напряжение (сигнал) (-)Ux, или (-)Uxi, или (-) и,, .:

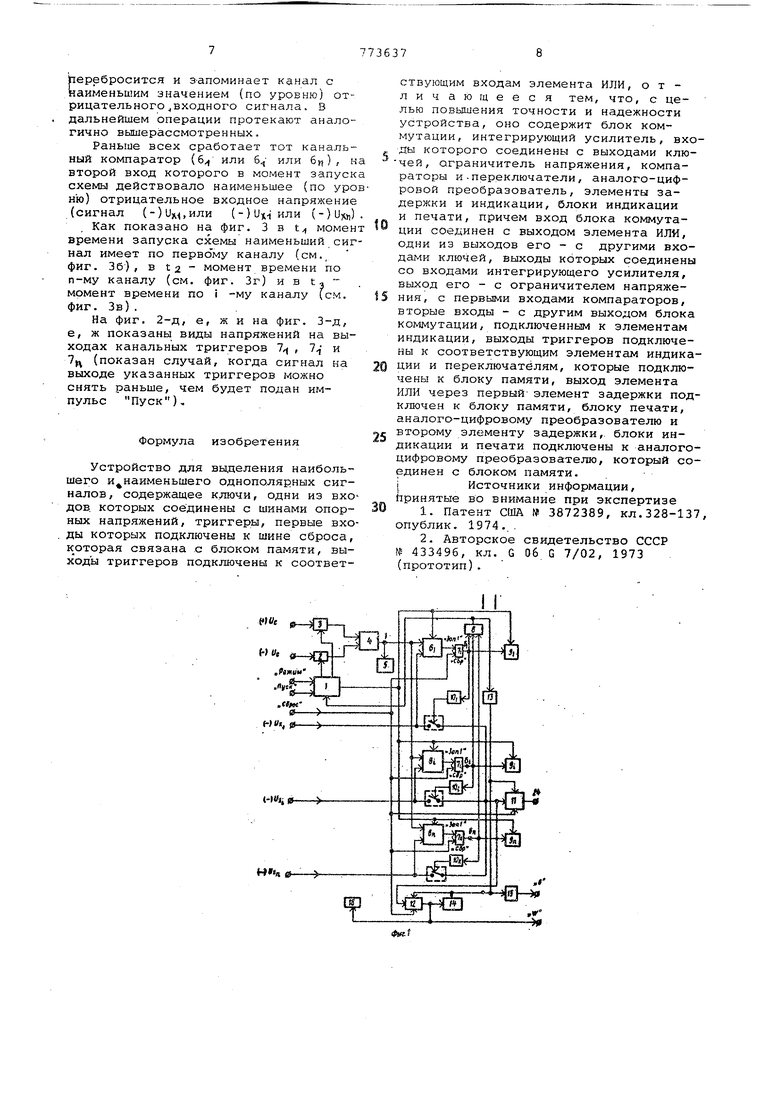

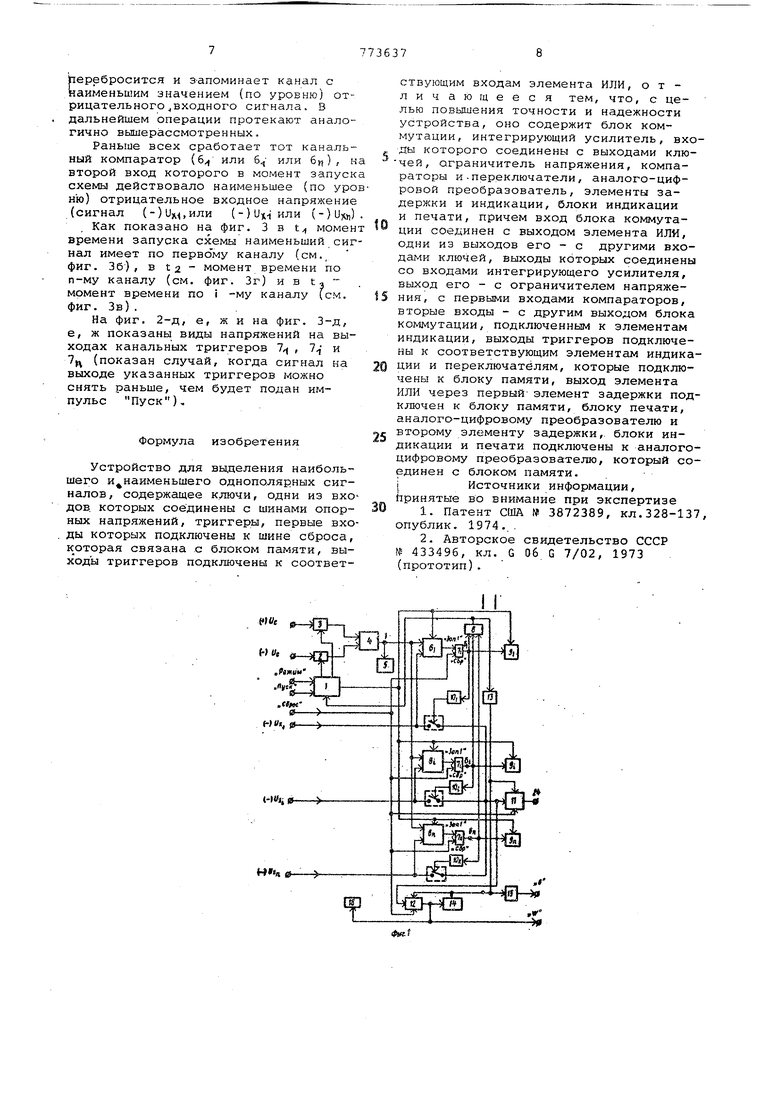

Как показано-на фиг. 2,в t момент времени запуска схемы наиболь- , ший сигнал имеется по первому каналу (см. фиг. 26), в t2 момент времени по 1-му каналу (см. фиг. 2в) и в момент времени по п-му каналу (см. фиг. 2г). Аналогично протекают проОцессы в случае определения аименьшего однополярного сигнала из п-входных однополярных сигналов. В этом случае в блок коммутации 1 через шину Режим подаётся импульс, под дейст5вием которого на первый выход блока коммутации 1 подается сигнал, закрывающий первый ключ 2, а на второй выход - сигнал, открывгиснций второй ключ 3. В результате на вход интегрирую0щего усилителя 4 подается (+)Uc,a на его выходе устанавливается уровень напряжения (-)и, ограниченный ограничителем напряжения 5 (см. фиг. Зб,в,г). Под действием сигнала, полученного на третьем выходе блока коммутации 1,

5 канальные компараторы б , и б переключаются в такое состояние, при котором на их выходах поддерживаются нулевые уровни выкодньпс сигналов и никаких действий на канальные триг-

D геры 7 , 7 и 7 и, следовательно, на канальные, элементы индикации 9i / и 9и, а также канальные перёключат.ели 10, lO-j и 10« не производится. Такое нулевое состояние канальных ком5параторов б,, б;,- и 6и в данном случае объясняется тем, что поданное на их первые входы яапряЕжение (-)U совпадает по знаку ос входнъаш отрицательными налр1 1сёниями (-)U;H, )x-t ()Ц1и

0 которые действуют на вторые входы канальных компараторов б , б. и 6vi и удерживают их в состоянии.

Допустим в t момент времени (см. фиг. За) через шину Пуск подают импульс, который, воздействуя на блок

5 коммутации 1, меняет на его первом и вторсил BtsKORSoi состояние уройней напряжений на прота&ополохные. В результате этого первый ключ 2 откроется, а второй ключ 3 закроется и на вход

0 интегрирующего усилителя 4 начнет действовать (-)Ue. На выходе интегрирующего усилителя 4 отрицательное напряжение {-)Uj,начнет линейно увеличиваться в сторону нулевой оси и по5ложительной полярности.

В момент равенства на входах ка- , нальных компараторов б , б и б(, напряжение (+)иД i полученное на выходе интегрирующего усилителя 4, с од0ним из л-входных отрицательных напряжений ((-)Ux,i. или ( (-)Uw,)) на выходе одного из канальных компараторов б или б или б образуется импульс, под действием 1 оторого соответствующий канальный триггер

5

перебросится и з-апоминает канал с наименьшим значением (по уровню) отрицательного входного сигнала. В дальнейшем операции протекают аналогично вышерассмотренных.

Раньше всех сработает тот канальный компаратор (6 или или 6)), на второй вход которого в момент запуска схемы действовало наименьшее (по уровню) отрицательное входное напряжение (сигнал (-)ихьили ( - ) или (-)U)Cn).

Как показано на фиг. 3 в t момент времени запуска схемы наименьший сигнал имеет по первому каналу (см., фиг. 36), в t2 - момент времени по

п-му каналу (см. фиг. Зг) и в t

момент времени по i -му каналу (см. фиг. Зв).

На фиг. 2-д, е, ж и на фиг. 3-д, е, ж показаны виды напряжений на выходах канальных триггеров 7 , 7-, и 7j (показан случай, когда сигнал на выходе указанных триггеров можно снять раньше, чем будет подан импульс Пуск),

Формула изобретения

Устройство для вы,целения наибольшего и наименьшего однополярных сигналов, содержащее ключи, одни из вхо дов. которых соединены с шинами опорных напряжений, триггеры, первые входы которых подключены к шине сброса, к оторая связана с блоком памяти, выходы триггеров подключены к соответf)0t

ствующим входам элемента ИЛИ, отличающееся тем, что, с целью повышения точности и надежности устройства, оно содержит блок коммутации, интегрирующий усилитель, входы которого соединены с выходами ключей, ограничитель напряжения, компараторы и-переключатели, аналого-цифровой преобразователь, элементы задержки и индикации, блоки индикации и печати, причем вход блока коммутации соединен с выходом элемента ИЛИ, одни из выходов его - с другими входами ключей, выходы которых соединены со входами интегрирующего усилителя, выход его - с ограничителем напряжения, с первыми входами компараторов, вторые входы - с другим выходом блока коммутации, подключенным к элементам индикации, выходы триггеров подключены к соответствующим элементам индикации и переключателям, которые подключены к блоку памяти, выход элемента ИЛИ через первый элемент задержки подключен к блоку памяти, блоку печати, аналого-цифровому преобразователю и второму элементу задержки,, блоки индикации и печати подключены к аналогоцифровому преобразователю, который соединен с блоком памяти. I Источники информации, принятые во внимание при экспертизе

1.Патент США 1 3872389, кл.328-13 опублик. 1974.. .

2.Авторское свидетельство СССР № 433496, кл. G Об G 7/02, 1973 (прототип).

Те t(

ribr-z-kr:

(Л)

(+)Wn ui

.

Vж -tit

4fi-(ДН III I.I

fI I,

l-Ц--I t

К%%:%%||

(/fi

Ж

tfin

| название | год | авторы | номер документа |

|---|---|---|---|

| Измеритель параметров комплексных сопротивлений | 1989 |

|

SU1751690A1 |

| Устройство считывания для многоэлементных фотоприемников инфракрасного излучения | 2016 |

|

RU2645428C1 |

| Осциллографический измеритель параметров сверхвысокочастотных многополюсников | 1981 |

|

SU1026061A1 |

| Множительно-делительное устройство | 1977 |

|

SU696444A1 |

| Регистратор максимальных перегрузок | 1990 |

|

SU1764154A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU782153A1 |

| ЦИФРОВОЙ ДИНАМОМЕТРИЧЕСКИЙ КЛЮЧ | 2013 |

|

RU2532239C1 |

| ЦИФРОВОЙ МОМЕНТНЫЙ КЛЮЧ | 2016 |

|

RU2632053C1 |

| Устройство для коррекции нелинейности | 1982 |

|

SU1056228A1 |

| ЦИФРОВОЙ ИЗМЕРИТЕЛЬ КРИТЕРИЯ ВОСПЛАМЕНЯЮЩЕЙ СПОСОБНОСТИ ИСКРОВЫХ РАЗРЯДОВ В СВЕЧАХ ЗАЖИГАНИЯ | 2000 |

|

RU2182336C2 |

Авторы

Даты

1980-10-23—Публикация

1976-12-20—Подача