Изобретение относится к импульсной технике и может быть использовано для передачи аналоговых сообщений цифровым способом.

Известно устройство связи с дельта-5 модуляцией, состоящее из кодирующего блока, содержащего вентили и блок вычитания, соединенный через двоичный модулятор с выходом кодирующего блока и входом интегратора, и 10 из декодирующего блока, содержащего интегратор и фильтр нижних частот, соединенные последовательно С11.

Недостатком этого устройства является низкая достоверность пере;}ачи И5 аналогового сигнала.

Наиболее близким к предлагаемому по техническому решению является устройство связи с дельта-модуляцией, содержащее кодирующий узел, состоящий20 из последовательно соединенных первого вентиля, вход которого соединен с входом устройства, блока вычитания, двоичного модулятора, выход которого соединен с выходом кодирующего узла, 25 и интегратора, выход которого соединен с входами блока вычитания и второго вентиля, выход которрго соединен с другим входом интегратора, к выходу первого вентиля подключен третий вен-зо тиль, выход которого, соединен с вторыми входами первого и второго вентилей, синхронизатора, выход которого соединен с другим входом двоичного модулятора, и декодирующий узел, , состоящий из синхронизатора и интегратора, входы которых соединены с входом декодирующего узла, один выход интегратора соединен с входом фильтра нижних частот и первым входом 0 вентиля, выход которого соединен с другим входом интегратора, а выход фильтра нижних частот соединен с выходом .устройства t23.

Недостаток этого устройства - кая достоверность преобразования аналогового сигнала, обусловленная осуществлением коррекции аналоговым способом.

Цель изобретения - повьшение досто-г,. верности аналогового сигнала.

Поставленная цель достигается тем, что в устройстве связи с дельта-модуляцией, содержащем кодирующий узел, состоящем из последовательно соединенных первого вентиля, вход которого; соединен с входом устройства, блока вычитания, двоичного модулятора, выход которого соединен с выходами кодирующего узла, и интегратора, один выход которого соединен с входами блока вычитания и второго вентиля, выход которого соединен с другим входом интегратора, к выходу первого венТШ1Я подключен третий вентиль, вьЬсод которого соединен с вторыми входами первого и второго вентилей, синхронизатора, .выход которого соединен с другим входом двоичного модулятора, и декодирующий узел, состоящий из синхронизатора и интегратора, входы которых соединены с входом декодирующего узла, один выход интегратора соединен с входом фильтра нижних частот и первым входрм вентиля, выход которого соединен с другим входом интегратора, а выход фильтра нижних частот соединен с выходом устройства, в кодирующий узел введен дешифратор меандра, первый вход которого соединен с выходом синхронизатора, второй с входом интегратора, а выход - с вторьм входом второго вентиля, а в декодирующий узел введен другой дешифратор меандра, первый вход которог соединен с входом декодирующего узла, второй вход - с выходом синхронизатора, а выход - с вторым входом вентиля.

Дешифратор меандра состоит из сдвигового регистра, входы которого соединены с соответствующими входами дешифратора меандра, а выходы - через соответствующие сумматоры по модулю два подключены к входам элемента И, выход которого через формирователь соединен с выходом дешифратора меандра.

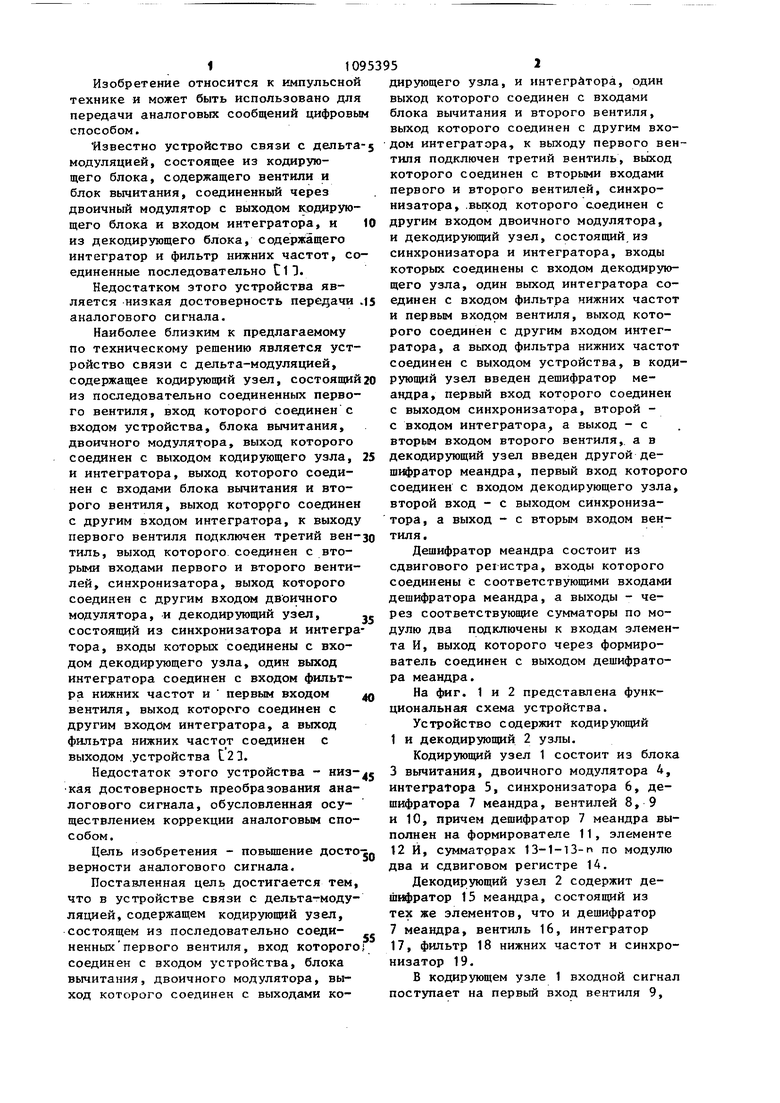

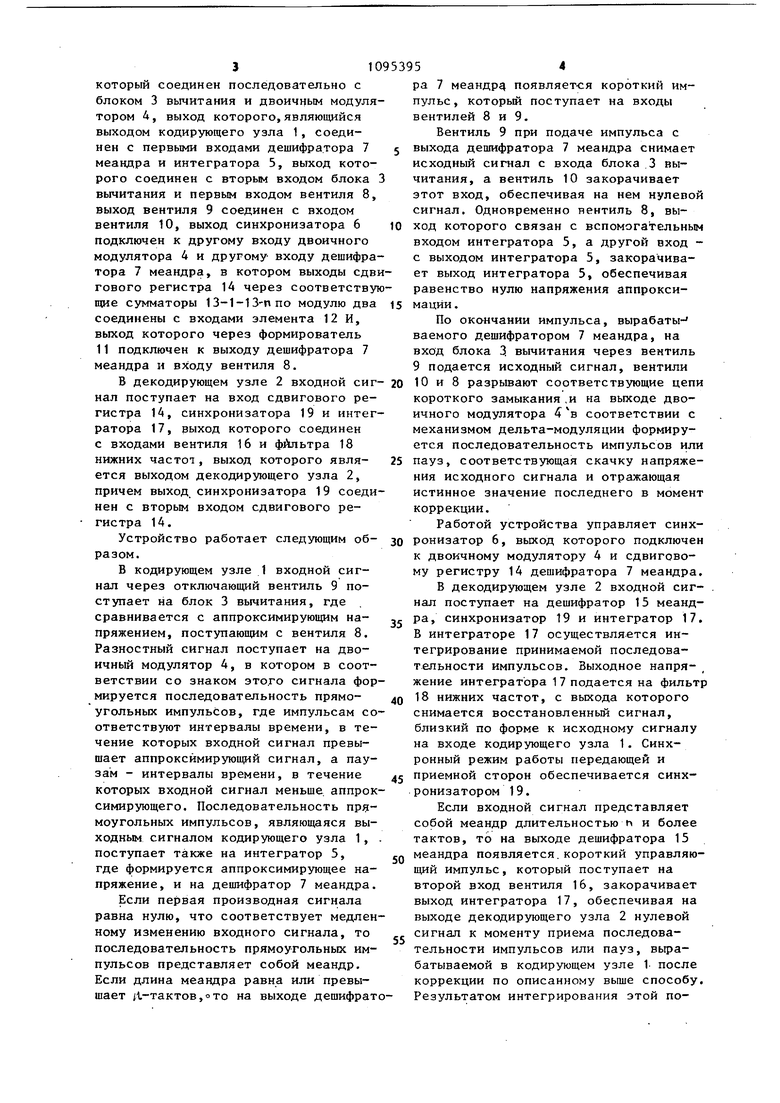

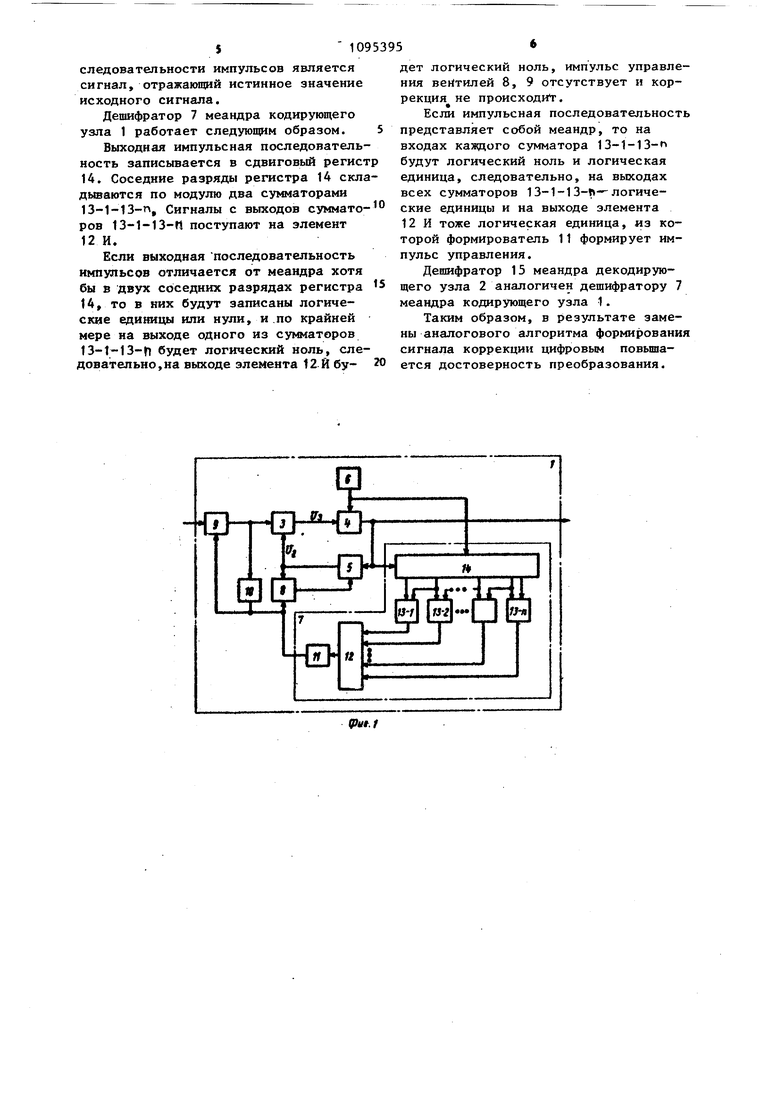

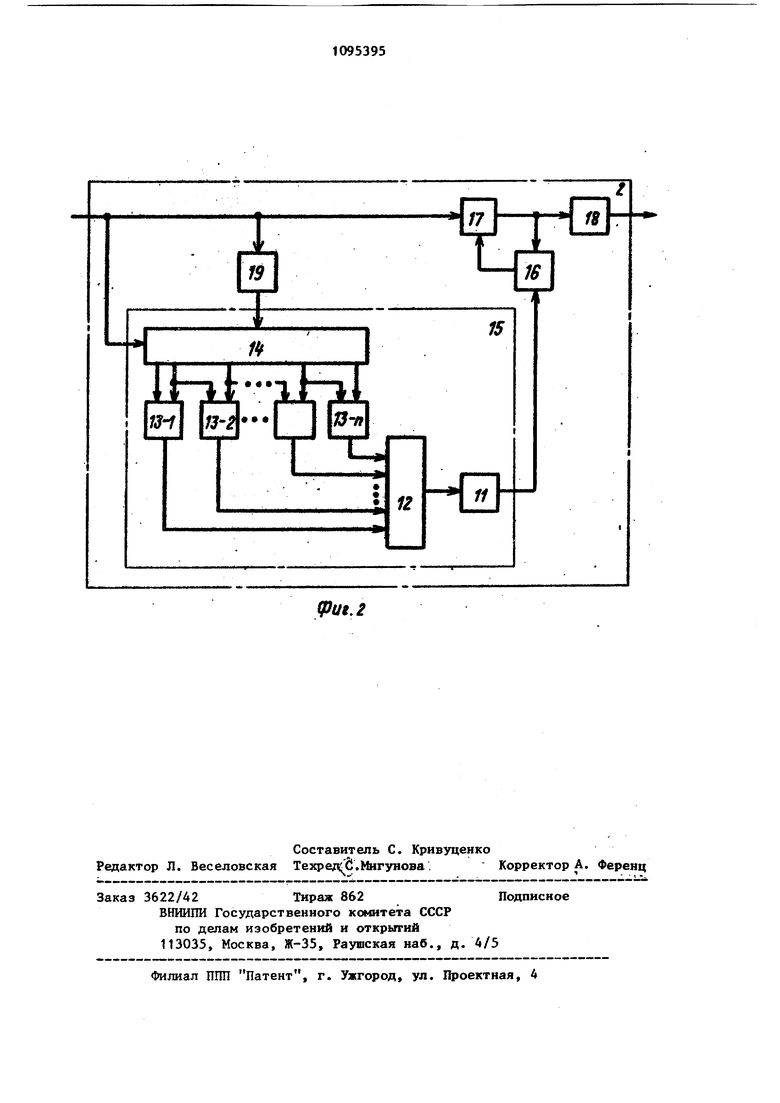

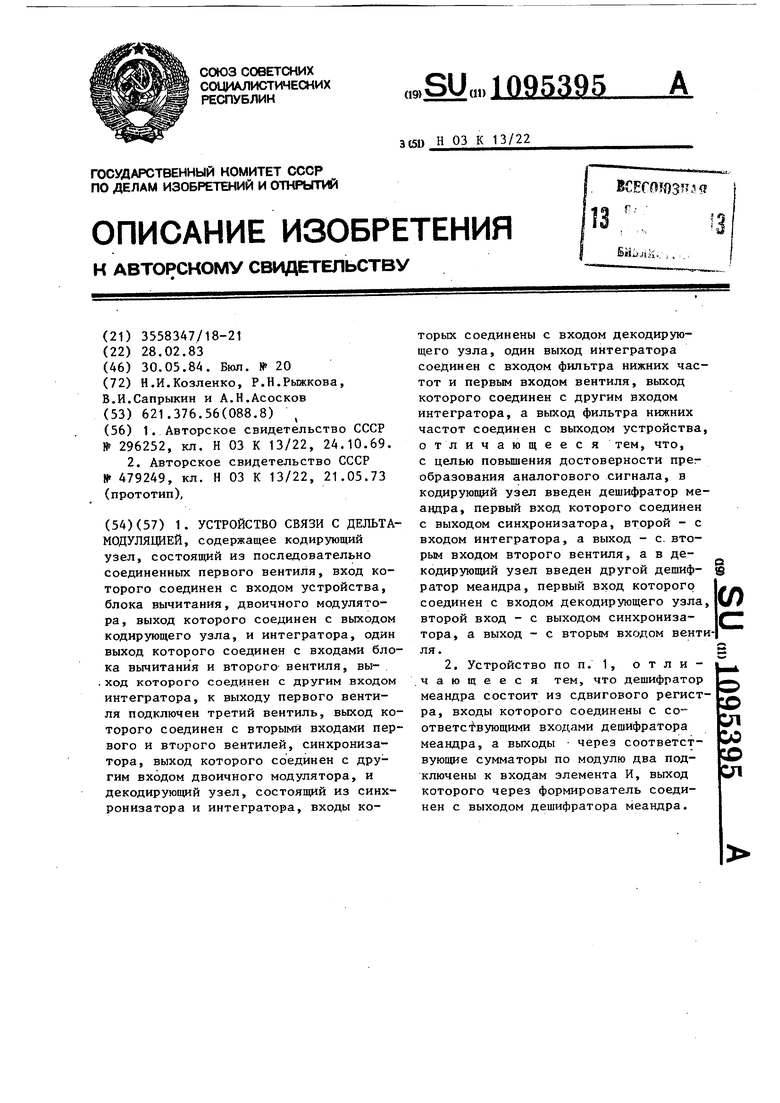

На фиг. 1 и 2 представлена функциональная схема устройства.

Устройство содержит кодирующий 1 и декодирующий 2 узлы.

Кодирующий узел 1 состоит из блока 3 вычитания, двоичного модулятора 4, интегратора 5, синхронизатора 6, дешифратора 7 меандра, вентилей 8, 9 и 10, причем дешифратор 7 меандра выполнен на формирователе 11, элементе 12 И, сумматорах 13-1-13-г по модулю два и сдвиговом регистре 14.

Декодирующий узел 2 содержит дешифратор 15 меандра, состоящий из тех же элементов, что и дешифратор 7 меандра, вентиль 16, интегратор 17, фильтр 18 нижних частот и синхронизатор 19.

В кодирующем узле 1 входной сигнал поступает на первый вход вентиля 9, который соединен последовательно с блоком 3 вычитания и двоичным модуля тором 4, выход которого,являющийся выходом кодирующего узла 1, соединен с первыми входами дешифратора 7 меандра и интегратора 5, выход которого соединен с вторым входом блока вычитания и первым входом вентиля 8, выход вентиля 9 соединен с входом вентиля 10, выход синхронизатора 6 подключен к другому входу двоичного модулятора 4 и другому входу дешифра тора 7 меандра, в котором выходы сдв гового регистра 14 через соответству щие сумматоры 13-1-13Ппо модулю два соединены с входами элемента 12 И, выход которого через формирователь 11 подключен к выходу дешифратора 7 меандра и входу вентиля 8. В декодирующем узле 2 входной сиг нал поступает на вход сдвигового регистра 14, синхронизатора 19 и интег ратора 17, выход которого соединен с входами вентиля 16 и фильтра 18 нижних частот, выход которого является выходом декодирующего узла 2, причем выход синхронизатора 19 соеди нен с вторым входом сдвигового регистра 14. Устройство работает следующим образом. В кодирующем узле 1 входной сигнал через отключающий вентиль 9 поступает на блок 3 вычитания, где сравнивается с аппроксимирующим напряжением, поступающим с вентиля 8. Разностный сигнал поступает на двоичный модулятор 4, в котором в соответствии со знаком этого сигнала фор мируется последовательность прямоугольных импульсов, где импульсам со ответствуют интервалы времени, в течение которых входной сигнал превышает аппроксимирующий сигнал, а паузам - интервалы времени, в течение которых входной сигнал меньше аппрок симирующего. Последовательность прямоугольных импульсов, являющаяся выходным сигналом кодирующего узла 1, поступает также на интегратор 5, где формируется аппроксимирующее напряжение, и на дешифратор 7 меандра. Если первая производная сигнала равна нулю, что соответствует медлен ному изменению входного сигнала, то последовательность прямоугольных импульсов представляет собой меандр. Если длина меандра равна или превышает 1-тактов,ото на выходе дешифрат ра 7 меандру появляется короткий импульс, который поступает на входы вентилей 8 и 9, Вентиль 9 при подаче импульса с выхода дешифратора 7 меандра снимает исходный сигнал с входа блока .3 вычитания, а вентиль 10 закорачивает этот вход, обеспечивая на нем нулевой сигнал. Одновременно вентиль 8, выход которого связан с вспомогательным входом интегратора 5, а другой вход с выходом интегратора 5, закорачивает выход интегратора 5, обеспечивая равенство нулю напряжения аппроксимации . По окончании импульса, вырабатываемого дешифратором 7 меандра, на вход блока 3 вычитания через вентиль 9подается исходный сигнал, вентили 10и 8 разрьшают соответствующие цепи короткого замыкания ,и на выходе двоичного модулятора 4 в соответствии с механизмом дельта-модуляции формируется последовательность импульсов или пауз, соответствующая скачку напряжения исходного сигнала и отражающая истинное значение последнего в момент коррекции. Работой устройства управляет синхронизатор 6, выход которого подключен к двоичному модулятору 4 и сдвиговому регистру 14 дешифратора 7 меандра, В декодирующем узле 2 входной сигнал поступает на дешифратор 15 меандра, синхронизатор 19 и интегратор 17. В интеграторе 17 осуществляется интегрирование принимаемой последовательности импульсов. Выходное напряжение интегратора 17 подается на фильтр 18 нижних частот, с выхода которого снимается восстановленный сигнал, близкий по форме к исходному сигналу на входе кодирующего узла 1, Синхронный режим работы передающей и приемной сторон обеспечивается синхронизатором 19. Если входной сигнал представляет собой меандр длительностьюи и более тактов, то на выходе дешифратора 15 меандра появляется.короткий управляющий импульс, который поступает на второй вход вентиля 16, закорачивает выход интегратора 17, обеспечивая на выходе декодирующего узла 2 нулевой сигнал к моменту приема последовательности импульсов или пауз, вырабатываемой в кодирующем узле 1 после коррекции по описанному выше способу. Результатом интегрирования этой последовательности импульсов является сигнал, отражающий истинное значение исходного сигнала.

Дешифратор 7 меандра кодирующего узла 1 работает следующим образом.

Выходная импульсная последовательность записьюается в сдвиговый регист 14. Соседние разряды регистра 14 складываются по модулю два сумматорами 13-1-13-г, Сигналы с выходов сумматоров 13-1-13-ft поступают на элемент 12 И.

Если выходная последовательность импульсов отличается от меандра хотя бы в двух сЬседних разрядах регистра 14, то в них будут записаны логические единицы или нули, и.по крайней мере на выходе одного из сумматоров 13-1-13-fi будет логический ноль, следовательно, на выходе элемента 12 И будет логический ноль, импульс управления вентилей 8, 9 отсутствует и коррекция не происходи.

Если импульсная последовательность представляет собой меандр, то на входах каядого сумматора 13-1-13-f будут логический ноль и логическая единица, следовательно, на выходах всех сумматоров 13-1-13- - логические единицы и на выходе элемента 12 И тоже логическая единица, из которой формирователь 11 формирует импульс управления.

Дешифратор 15 меандра декодирующего узла 2 аналогичен дешифратору 7 меандра кодирующего узла 1.

Таким образом, в результате замены аналогового алгоритма формирования сигнала коррекции цифровым повьш1ается достоверность преобразования.

| название | год | авторы | номер документа |

|---|---|---|---|

| Система связи с дельта-модуляцией | 1983 |

|

SU1163476A1 |

| Устройство связи с дельта-модуляцией | 1973 |

|

SU479249A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СООБЩЕНИЙ С ДЕЛЬТА-МОДУЛЯЦИЕЙ | 1972 |

|

SU340083A1 |

| Дельта-декодер | 1986 |

|

SU1432779A1 |

| Устройство для передачи сообщений с адаптивной дельта-модуляцией | 1981 |

|

SU1025011A1 |

| Способ озвучивания кинофильмов и устройство для его осуществления | 1989 |

|

SU1705793A1 |

| СИСТЕМА СВЯЗИ С ДЕЛЬТА-МОДУЛЯЦИЕЙ | 1971 |

|

SU296252A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1996 |

|

RU2099739C1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

| Анализатор спектра | 1979 |

|

SU815664A1 |

1. УСТРОЙСТВО СВЯЗИ С ДЕЛЬТАМОДУЛЯЦИЕЙ, содержащее кодирующий узел, состоящий из последовательно соединенных первого вентиля, вход которого соединен с входом устройства, блока вычитания, двоичного модулятора , выход которого соединен с выходом кодирующего узла, и интегратора, один выход которого соединен с входами блока вычитания и второго вентиля, вы.ход которого соединен с другим входом интегратора, к выходу первого вентиля подключен третий вентиль, выход которого соединен с вторыми входами первого и второго вентилей, синхронизатора, выход которого соединен с другим входом двоичного модулятора, и декодирующий узел, состоящий из синхронизатора и интегратора, входы которых соединены с входом декодирующего узла, один выход интегратора соединен с входом фильтра нижних частот и первым входом вентиля, выход которого соединен с другим входом интегратора, а выход фильтра нижних частот соединен с выходом устройства, отличающееся тем, что, с целью повышения достоверности прегобразования аналогового сигнала, в кодирующий узел введен дешифратор меандра, первый вход которого соединен с выходом синхронизатора, второй - с входом интегратора, а выход - с. вторым входом второго вентиля, а в де§ кодирующий узел введен другой дешифратор меандра, первый вход которого (Л соединен с входом декодирующего узла, второй вход - с выходом синхронизатора, а выход - с вторым входом вентиля. 2, Устройство по П.1, отли.чающееся тем, что дешифратор меандра состоит из сдвигового регист ра, входы которого соединены с со:л ответс вующими входами дешифратора :о х меандра, а выходы - через соответствующие сумматоры по модулю два подел ключены к входам элемента И, выход которого через формирователь соединен с выходом дешифратора меандра.

(put. 2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| СИСТЕМА СВЯЗИ С ДЕЛЬТА-МОДУЛЯЦИЕЙ | 0 |

|

SU296252A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство связи с дельта-модуляцией | 1973 |

|

SU479249A1 |

Авторы

Даты

1984-05-30—Публикация

1983-02-28—Подача