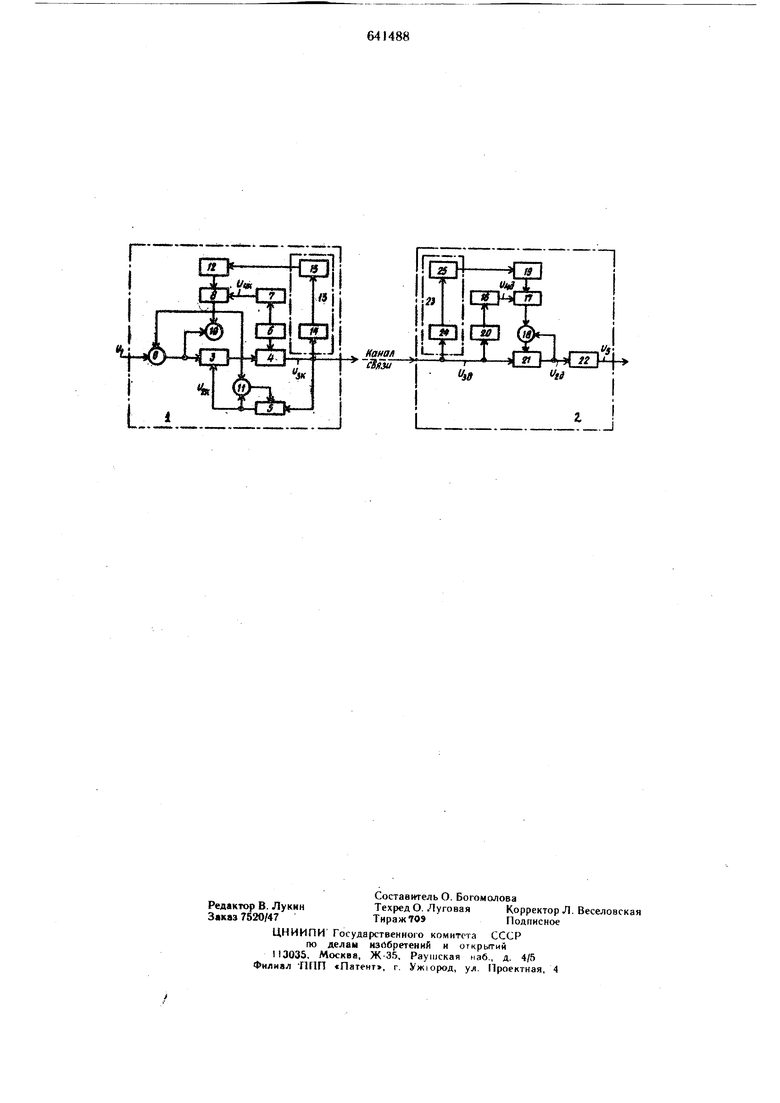

рым входом нгиегратора, выход фильтра подключен к выходу устройства. Недостатком устройства . является его сложность и невозможность обеспечепнг высокой точности коррекции, т.к. в устройстве в, качестве опорных сигналов для рекции используются аналоговые снгаа-яы, и, следовательно, аналоговая техника. Это приводит к необходимости пщатеньного подбора к согласования элемейтов уст| оЙ€ТБа. Другим недостатком яв яетсй то, что в устройстве не учитываетсй времй дередачя т преобразования информации, что 8 рмвод зт к несовиаденню интервалов времени коррекции в кодирующем и дек0дафук щем узлах. Целью изобретений йвляется уорощеняе устройства и повышений его то« коетй. Достигается это введением на приемной и пе| едающей стороне устройства детеяторов крутизны, каждый йэ которьря CQCFOBT из последовательно соедннеиныя блока ssa(йяти и решающего блока, на нередаю-щей сторойб вход детектора крутизны соединен с выходом квантователя, а вь4ход детектора крутизны соединен со входок блока заярета, на приемной стороне вход детеатора к утизны соединен е кавзлом связи, з выход - со входом блока эзйрета. На чертеже представлена структуриая схема устройства. Уст|к йство содер-жйт на передающей стороне кодирующий узел I и на приемной стороне декодирующий узел 2. В еостаа код||рующего узла вкодит блок вачитания 3, кзантователь 4, интегратор 5, синхронизатор 6, делитель частоты 7, блок стробир-эвания 8, логические элементы 9, Ш, 11, блок ззарета 12, детектор крутизны 13, блок памяти 14 и решак щ{ й блок 15, на приемной стороне декодирующий yseri 2 содержит де йтель частоты 16, блок С рОбйрОВ8Н|- й 17., Л€ ГНЧ8Ский элемент 18, блок запрета 19, сттропкзатор 20, интегратор 21, 22, де1-ектор крутизны 23, состоящий из блока ашйятй 24 н решающего блока 25. Устройство работает следующим образом. В кодирующем узле I исходный сигнал Ui через логический элемент 9 подается на блок вычитания 3,соедннейньгй с квантователем.4. В блоке вычитания Сформируется СНГнал разноста между исходным сигналом Ui и сигналом аппроксимации USK , вырабатываемым интегратором 5, первый вход которого связан с выходом квантовдтеля 4, а выход - со входом блока вычитания 3. Разностный сигнал поступает в квантователь 4, где в соответствии со знаком этого сигнала формируется последовательность импульсов дельта-потока USK .«-fl н « -i, несущнх информацию о скорости изменения исходного сигнала. Импульсы дельта-потока постунают в канал связи, в интегратор 5 и на вход блока памяти 14, детектора крутизны 13, блок памяти И запоминает неско./1ь ко последних имнульсов дельта-потока. Его выход связан со входом решающего блока, который реагирует только на такие состоянпя блока памяти 4, которые соответствуют медленным изменениям исходного сигнала. Если блок памяти окажется в одном из такмх состояний, то решающий блок 15 выдаст сигнал на блок запрета 12, выходной сигнал которого открывает блок стробироваьня 8, При этом выход делителя частоты оказывается соединенным с выходом блока стробяроващщ 8 и тем самым обеспечивается возможность функционирования коррекдаи S кодирующем узле 1. Если же блок яамятя 14 окажется в состоянии, соответствукмдем быстрым изменениям сигнала, то решающий блок 15 не выдает сигнал на блок запрета 12 и блок стробирования 8 остаетсй закрытым. В этом случае выход делителя частоты 7 оказывается отсоединенвыт от выхода блока стробирования 8 и прекращается возможность функционирования коррекции в кодирующем узле 1. Работой всего кодирующего узла I управляет синхронизатор 6, с одного из выходов которого жиггунают импульсы на кван™ Дяя формирования дельта-потока USK , Другай выход синхронизатора 6 связая со входом делителя частоты 7, с выхода которого сннглаются кратковременные импульсные сигналы U4K . период следования которых соответствует пернодичностн процесса коррекции, При обеспечений возможности функционирозання механизма коррекции с выхода делителя частоты 7 через блок стробировання 8 подаются управляющие сигналы на входы логических элементов 9, 10, П. При поступлений управляющего сигнала на логический элемент 9 осуществляется снятие сигнала со входа блока вычитания 3, а логический элемент 10 закорачивает этот вход, обеспечивая на нем нулевой сигнал. Одновременно, логический элемент ii, выход которого связан со вторым входом интегратора 5,, а второй вход - с выходом интегратора 5, закорачивает его выход, обеспечивая равенство нулю напряжения аппроксимации, При снятии управляющего сигнала логический элемент 9 пропускает исходный сигнал на вход блока вычитания 3, логические элементы 10 и II разрывают соответствующие цепи короткого.замыкання и на выходе квантователя 4 в соответствии с механизмом дельта-модуляции формируется последовательность импульсов «-fl или « -1, соответствующая скачку напряжения исходного сигнала Ui и оггражающая его истинное значение в момент коррекции. В интеграторе 21 декодирующего узла 2 осуществляется интегрирование прннимаемых импульсов дельта-потока Usg . Выходное напряжение IJzg интегратора 21 поступает на фильтр 22 и с его выхода снимается восстановленный сигнал Us, по форме близкий к исходному сигналу Ui. Сигналы UjB поступают также на вход блока памяти 24, детектора крутизны 23. Блок памяти 24 запоминает несколько последних импульсов дельта-потока. Выход блока памяти 24 связан со входом решающего блока 25, который реагирует только на такие состояния блока памяти 24, которые соответствуют медленным изменениям сигнала аппроксимации Usy, а, следовательйо, и восстановлениого сигнала Us. Если блок памяти 24 окажется в одном из таких состояний, то решающий блок 25 выдаст сигнал на блок запрета i9, выходной сигнал с которого открывает блок стробирования 17. При этом выход делителя частоты 16 оказыва ется соединенным с выходом блока стробирования 17, и тем самым обеспечивается ф; нкциоиирование коррекции в декодирующем узле 2. Если же блок памяти 24 окажется в состоянии, соответствующем быстрым изменениям сигнала аппроксимации ,U2|, то решающий блок 25 не выдает сигнал иа вход блока запрета 19, который своим выходным сигналом закрывает блок стробирования 17. В таком случае выход делителя частоты 16 оказывается отсоединенным от выхода блока стробирования 17 и коррекция в декодирующем узле 2 не функционирует. Работой всего декодирующего узла 2 управляет синхронизатор 20, работающий синхронно с синхронизатором 6 кодирующего узла . Вход синхронизатора 20 соединен со входом интегратора 21 и детектора крутизны 23, а выход - со входом делителя частоты 16. Последний вырабатывает кратковременные импульсы и,, период следования которых соответствует периодичности процесса коррекции. При обеспечении возможности функционирования механизма коррекции сигнала V через блок стробнрования 17. подаются на первый вход логического элемента 18, второй вход которого соединен с выходом интегратора 21, а выход логического элемента 18 связан со вторым входом этого интегратора. При подаче импульса .на логический элемент 18, последний закорачивает выход интегратора 21, обеспечивая равенство нулю сигнала аппроксимации Uzf к мо.менту приема последовательности импульсов, вырабатываемых в кодирующем узле I в результате коррекции по описанному выше способу. Результатом интегрирования этой последовательности импульсов является сигнал, отражающий истинное значение исходного сигнала Ui. Формула изобретения Устройство для передачи н приема сообщений, содержащее на передающей стороне кодирующий и на приемной стороне декодирующий узлы, в состав кодирующего узла входит первый логический элемент, выход которого соединен с первым входом второго логического элемента и первым входом блока вычитания, выход которого связан с одним входом квантователя, другой вход которого соединен с первым выходом синхронизатора, выход квантователя соединен с каналом связи н с первым входом интегратора, выход которого соединен со вторым входом блока вычитания и с первым входом третьего логического элемента, выход которого связан со вторым входом интегратора, а второй вход - с выходом блока стробирования который так же соединен со вторыми входами первого и второго логических элементов, второй выход синхронизатора через делитель соединен с первым входом блока стробированйя, вто{юй вход которого связан с выходом блока запрета, на приемной стороне к каналу связи подключены первый вход интегратора и вход синхронизатора, выход которого через делитель частоты соединен с первым входом блока стробирования, второ 5 вход которого связан с выходом блока запрета, выход блока стробирования соедйнен с первым входом логического элемента, второй вход которого связан с выходом интегратора, который так же соединен со входом фильтра, выход логического элемента соединен со вторым входом интегратора, выход фильтра подключен к выходу устройства, отличающееся тем, что, с целью упрощения устройства н повышения его точности на приемной и передающей стороне введены детекторы крутизны, каждый из которых состоит из последовательно соединенных блока памяти н решающего блока, на передающей стороне вход детектора крутизны соединен с выходом квантователя, а выход - со входом блока запрета, на приемной стороне вход детектора крутизны сое динен с каналом связи, а выход - со входом блока запрета. Источники информации, принятые во внимание при экспертизе: 1,Авторское свидетельство СССР № 416862, кл. Н 03 К 13/22,04.01.72. 2.Авторское свидетельство СССР № 479249, кл. Н 03 К 13/22, 21.05.73. L.i. .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство связи с дельта-модуляцией | 1973 |

|

SU479249A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СООБЩЕНИЙ С ДЕЛЬТА-МОДУЛЯЦИЕЙ | 1972 |

|

SU340083A1 |

| Устройство связи с дельта-модуляцией | 1983 |

|

SU1095395A1 |

| СИСТЕМА СВЯЗИ С ДЕЛЬТА-МОДУЛЯЦИЕЙ | 1971 |

|

SU296252A1 |

| Дискретный адаптивный дельта-модулятор | 1976 |

|

SU641647A1 |

| Устройство для передачи сигналов с дельта-модуляцией | 1987 |

|

SU1420672A2 |

| Система связи с дельта-модуляцией | 1976 |

|

SU649135A2 |

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ СИГНАЛОВ С ДЕЛЬТА-МОДУЛЯЦИЕЙ | 1991 |

|

RU2025045C1 |

| Система связи с дельта-модуляцией | 1983 |

|

SU1163476A1 |

| Устройство для магнитной записи-воспроизведения звуковых сигналов | 1989 |

|

SU1712957A1 |

Авторы

Даты

1979-01-05—Публикация

1977-01-10—Подача