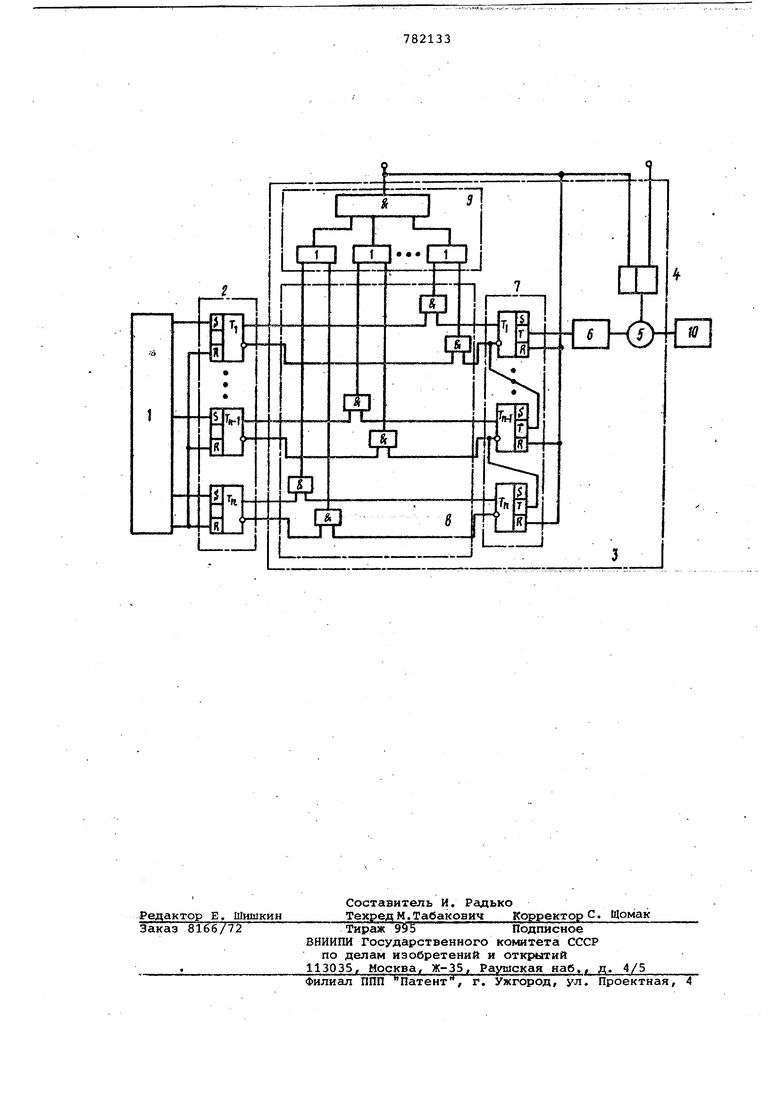

(54) УСТРОЙСТВО ДЛЯ УПРАВЛЯЕМОЙ ЗАДЕРЖКИ СИГНАЛОВ Изобретение относится к автоматике и.вычислительной технике. Известны устройства для управ- ляемой задержки сигналов, содержйицие датчики кода и устройство задержки 1. Уртройства имеют недостаточную точность. Известно устройство для управляемой задержки импульсов, содержащее программный блок, соединенный с празрядным триггерным регистром, элемент И и линию задержки на LC звень дх. 2. Недостатки известного устройства заключаются в том, что в нем погрешность временной задержки с уменьшени ем числа звеньев возрастает и данное устройство малоуниверссшьно минималь ное и максимальное время задержки ве личины постоянные , а его расчет и и готовление сравнительно трудны. Цель изобретения - уменьшение погрешности временной задержки и расши рение функциональных возможностей устройства. Поставленная цель достигается тем что в устройство для управляемой задержки сигналов, содержащее програм.мный блок, соединенный с п- разрядным триггерньм регистром и элементы И, введены триггер управления, задаю- щий генератор, вентиль, делитель, счетчик и элемент совпадения, причем один из входов триггера управления подключен к входной клемме устройства, выход триггер а управления соединен с одним из входов вентиля, другой вход которого соединен с выходом задающего генератора, выход вентиля соединен с входом делителя, выход которого соединен с входом п-разрядного триггерного счетчика, выходы которого подсоединены к одному из входов каждого элемента И, к другому входу каждого из которых подсоединены соответственно выходы п-разрядного триггерного регистра, выходы элементов И соединены с входами элемента совпгщения, выход которого соединен с вторым входом триггера управления, К-входами триггеров счетчика и выходной клеммой устройства. На чертеже приведена функциональная схема устройства. Устройство содержит программный блок 1, п-разрядный триггерныП регистр 2, линию 3 задержки, состоящую из триггера 4 управления, вентиль 5, делитель 6, счетчик 7, элементы 8 И элемент 9 совпадения и задающий генератор 10.

Код, соответствующий опре делённому времени задержки, подается из nporpaNiMHoro блока 1 на триггеры празрядного регистра 2 и устанавливает их в соответствующее состояние. Входной дигнал устройства подаёмся на вход триггера 4 управления и устанавливает его в единичное состояние. Триггер 4 управления вьадает высокий разрешающий потенциал на один из входов вентиля 5, к другому входу которого подсоединен задакяций генератор 10. Частота задающего генератора 10 выбрана в К раз большей, чем минимальное необходимое время задержки для точного совпадения во времени момента прихода входного импульса и появления частоты на выходе вентиля 5. С выхода вентиля 5 частота поступает на вход делителя 6. С выхода делителя 6 частота, поделенная на К, поступает на вход п-разрядного триггерного счетчика 7. Счетчик 7 начинает счет и при достижении в нем код равного коду, записанному в п-разрядном триггерном регистре, на выходе элемента 9 совпадения появ ;1яется импульс, который устанавливает триггер 4 управления в нулевое состояние, обнуляет п-разрядный триггерный счетчик и является также выходным сигналом устройства. Таким образом, погрешность временной задержки зависит только от числа к-кратности делителя 6. А дискретность и максимальную величину задержки можно варьировать, изменяя частоту задающего генератора, что значительно расширяет функциональные возможности устройства. Использование новых элёментбвтриггер.а управления, вентиля, задающего генератора, делителя, счетчика и элемента совпадения выгодно отличает данное устройство для управляемой задержки сигнала от известного

устройства, так как уменьшается погрешность временной задержки и появляется возможность изменять минимальное и максимальное время задержки, что расширит сферу применения устройства.

Формула изобретения

Устройство для управляемой задержки сигналов, содержащее программный блок,соединенный с п-разрядным триг- герным регистром,и Элементы И,о тличающееся тем,что,с целью уменьшения погрешности временной задержки и расширения функциональных возможностей устройства, в него введены триггер управления, задакадий генератор, вентиль, делитель, счетчик и элемент совпадения, причем один из

0 входов триггера управления подключен к входной клемме устройства выход триггера управления соединен с одним из входов вентиля, другой вход которого соединен с выходом задающе -

c го генератора, выход вентиля соединен с входом делителя, выход которого соединен с входом п-разрядного триггерного счетчика, .выходы которого подсоединены к одному из входов соответствующего элемента И, к другому входу

0 каждого из которых подсоединены соответственно выходы п-разрядного триггерного регистра, выходы элементов И соединены с входами элемента совпадения, выход которого соединен с вторым входом триггера управления, Квходами триггеров счетчика и выходной клемме устройства.

Источники информации, дл принятые во внимание при экспертизе

1.Авторское свидетельство СССР 441642, кл. Н 03 Н 7/30, 1972.

2.Авторское свидетельство СССР 498712, кл. Н 03 Н 7/32, 28.06.74 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство задержки сигналов | 1982 |

|

SU1015491A1 |

| Устройство задержки сигналов | 1982 |

|

SU1104655A2 |

| Устройство задержки сигналов | 1984 |

|

SU1215166A1 |

| ПРЕОБРАЗОВАТЕЛЬ ФАЗОВОГО СДВИГА ПЕРЕМЕННЫХ НАПРЯЖЕНИЙ В ЦИФРОВОЙ КОД | 1972 |

|

SU359756A1 |

| Цифровой регулятор | 1978 |

|

SU911458A1 |

| ИМИТАТОР ПРОВАЛОВ НАПРЯЖЕНИЯ СЕТИ | 1991 |

|

RU2028642C1 |

| Устройство для управления вентильным преобразователем | 1984 |

|

SU1205243A2 |

| СЛЕДЯЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1989 |

|

RU2028731C1 |

| УНИВЕРСАЛЬНАЯ ЦИФРОВАЯ УПРАВЛЯЮЩАЯ МАШИНА | 1965 |

|

SU170218A1 |

| Устройство для поверки цифровых измерителей девиации фазы | 1990 |

|

SU1781651A1 |

Авторы

Даты

1980-11-23—Публикация

1979-01-04—Подача