(54) ДИСКРЕТНЫЙ УМНОЖИТЕЛЬ ЧАСТОТЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой умножитель частоты | 1983 |

|

SU1164857A1 |

| Цифровой интерполятор | 1984 |

|

SU1238033A1 |

| Множительно-делительное устройство | 1976 |

|

SU590760A1 |

| Устройство для вычисления уровня жидких сред | 1984 |

|

SU1251101A1 |

| Генератор функций | 1984 |

|

SU1241219A1 |

| Устройство для цифрового функционального преобразования | 1981 |

|

SU985792A1 |

| Устройство для контроля работы транспортного средства | 1986 |

|

SU1345222A1 |

| Цифро-аналоговый генератор | 1978 |

|

SU698116A1 |

| Цифровая система для программного управления двигателем | 1986 |

|

SU1320793A1 |

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 2002 |

|

RU2210102C1 |

t

.Изобретение относится к электроизмерительной технике и предназначено для использования в радиоэлектронных установках различного назначения.

Известен умножитель частоты, со- 5 держащий регистр, схему переноса, схему ИЛИ, схему И, два делителя частоты, блок управления, формирующее устройство, два вентиля и генератор эталонной частоты, который соединен 10 с первыми входами первого и второго делителей частоты соответственно через первый и второй вентили, подключенные вторыми входами к первому и второму выходам блока управления, на |5 вход которого через формирующее устройство подается умножаемая частота, а третий выход связан через элемент ИЛИ со схемой переноса, включенной между регистром, вход которого сое- 20 динен с выходом первого делителя частоты который через элемент И связан со вторым входом элемента ИЛИ 1 .

Однако длительность переходного процесса в этом умножителе при изме- 25 нении коэффициента умножения или частоты входного сигнала составляет около двух периодов последнего, что приводит к низкому быстродействию устройства..30

Цель изобретения - повышение быстродействия устройства.

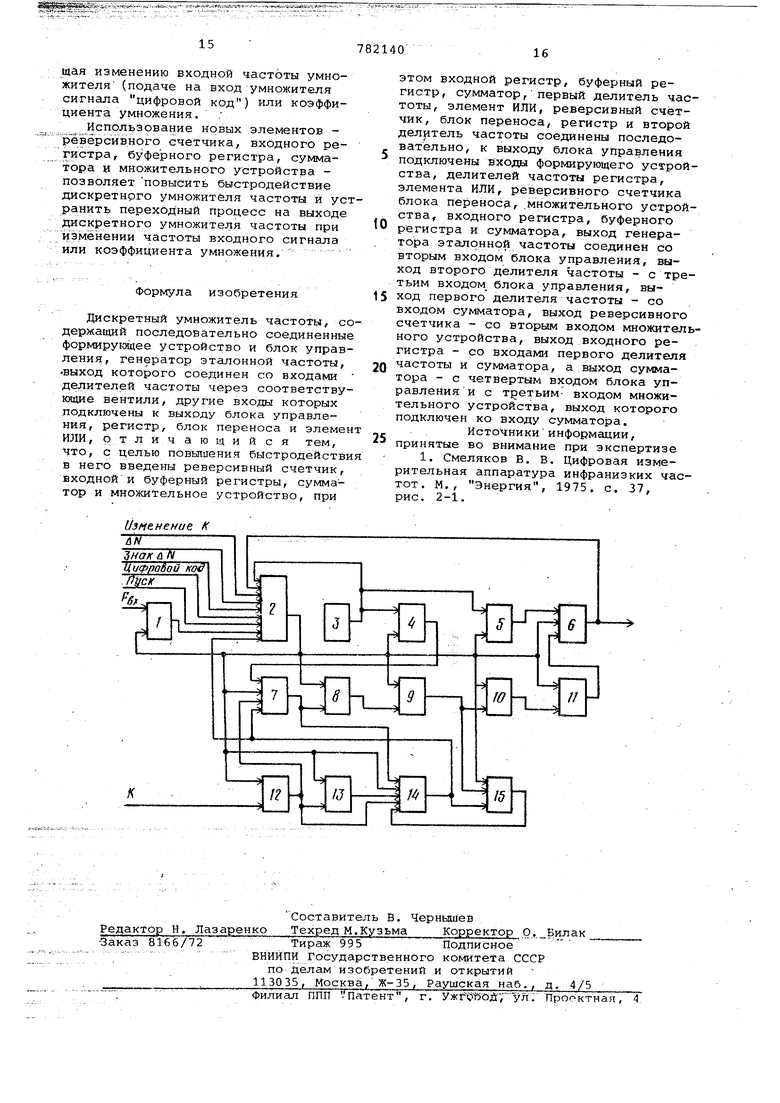

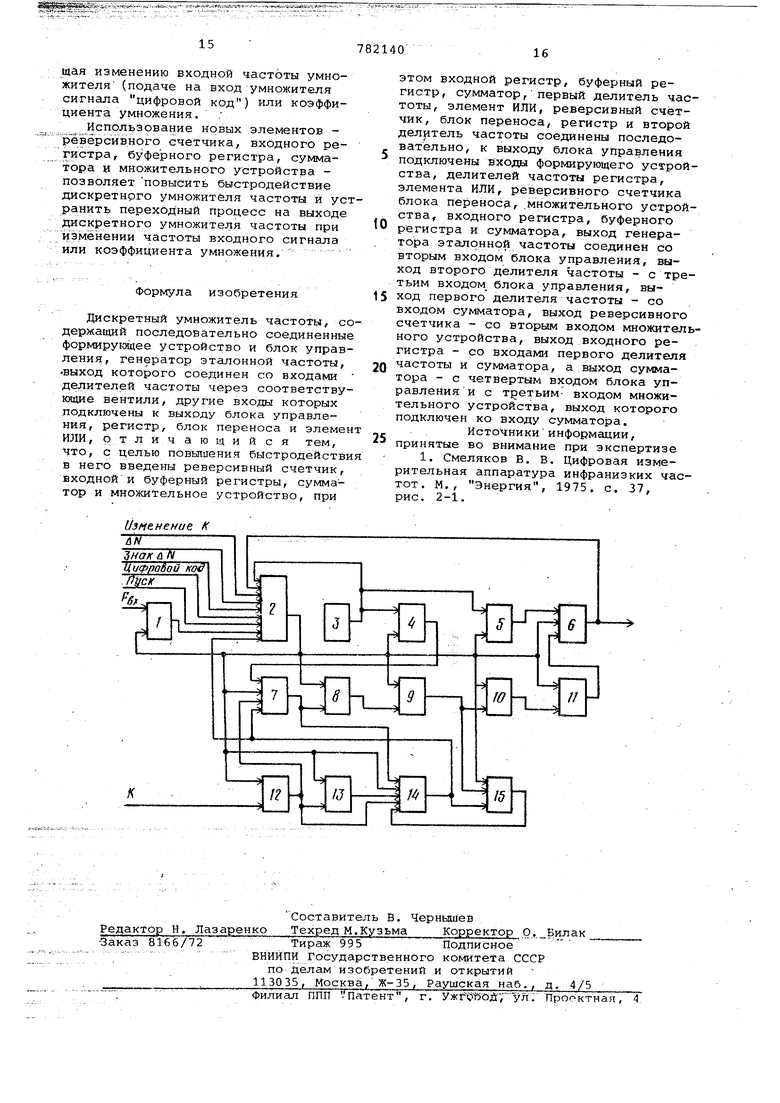

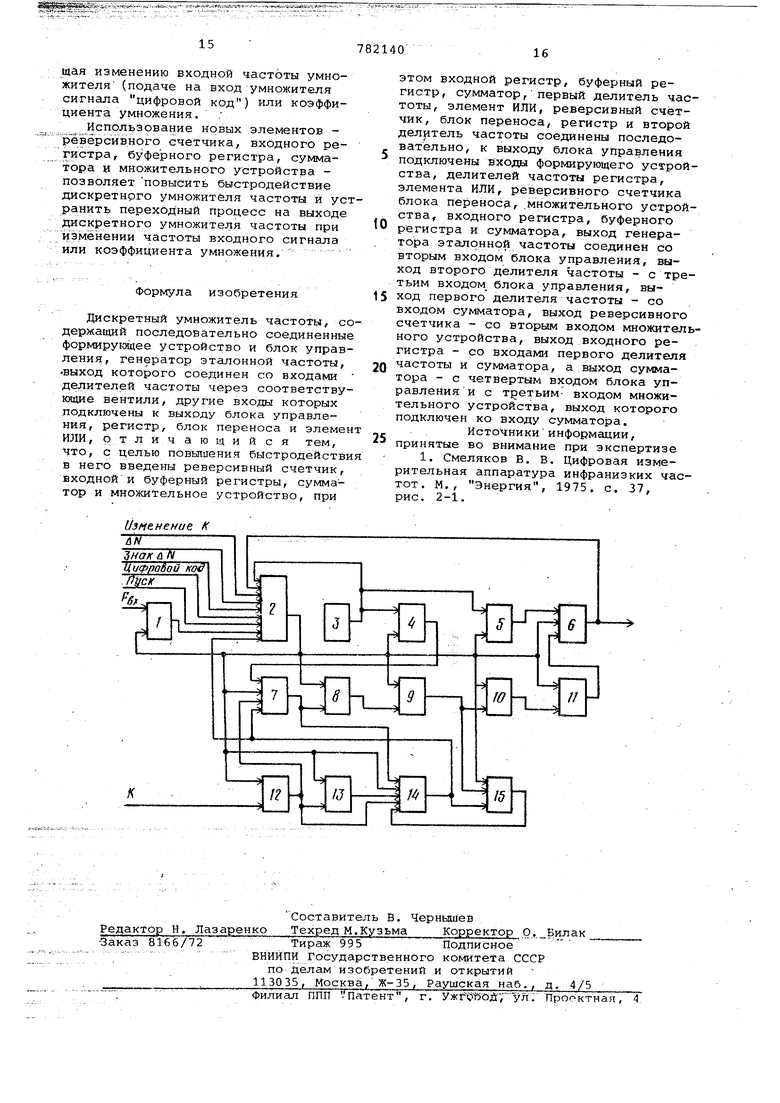

Для этого в дискретный умножитель частоты, содержащий последовательно соединенные формирующее устройство и ёлок управления, генератор эталонной частоты, выход которого соединен со входами делителей частоты через соответствующие вентили, другие входы которых подключены к выходу блока управления, регистр, блок переноса и элемент ИЛИ, введены реверсивный счетчик, входной и буферный регистры сумматор и множительное устройство, при этом входной регистр, буферный регистр, сумматор, первый делитель частоты, элемент ИЛИ, реверсивный счетчик,блок переноса,регистр и второй Делитель частоты соединены последовательно, к выходу блока управления подключены входы формирующего устройства, делителей частоты, регистра, элемента ИЛИ, реверсивного счетчика, блока переноса, множительного устройства, входного регистра, буферного регистра и сумматора, выход генератора эталойной частоты соединен СО вторым вхбдом блока управления, выход второго делителя частоты - с третьим входом блока управле-. ния, выход первого делителя частотысо входом сумматора, выход реверсивного счетчика - со вторым входом множительного устройства, выход входного регистра - со входами первого делителя частоты и сумматора, а выход сумматора - с четвертым входом блока управления и с третьим входом множительного устройства, выход которого подключен ко входу сумматора, На чертеже представлена структурная электрическая схема дискретного умножителя частоты. Дискретный умножитель частоты содержит формирующее устройство 1, бло 2 управления, генератор 3 эталонной частоты f(y , вентили 4 и 5, делители 6 и 7 частоты, элемент ИЛИ 8, реверсивный счетчик 9, блок 10 переноса, регистр 11, входной регистр 12, буферный регистр 13, сумматор 14, множительное устройство 15. Работает устройство следующим образом. В исходном состоянии вентили 4 и закрыты формирующим устройством 1 импульсы не вырабатываются, реверсив ный счетчик 9 установлен в режим сум мирования. Входному регистру 12 зада ется код коэффициента умножения К, (т самым коэффициент деления делителя 2 частоты устанавливается равным коэфф циенту умножения К,). По сигналу Пуск блоком 2 управления запускает ся формирующее устройство 1,которое осуществляет выделение периодов, вход ного сигнала, вырабатывая импульсы С периодом следования ьх / 6х где Fd - частота вход ноге сигнала. По первому выходному импульсу формирующего устройства 1 блоком 2 у равления открывается вентиль 4, через который в течение периода времени Т в реверсивный счетчик 9. вводят число импульсов д, равное целой части числа ,uh/K,, где ТЬУ - число импульсов генератора 3 этсшонной Частоты за период Tj,y , п - остаток импульсов накопленный в делителе 7 частоты к моменту йыработки формирующим устройством 1 второго выходного импульса. По второму выходному импульсу фор мирующего устройства 1 блоком 2 управления закрывается вентиль 4, осуществляется перепись содержимого реверсивного счетчика 9 через блок 10 переноса в регистр 11 (тем самым ко эффициент деления делителя 6 частоты устанавливается равным д ) и откры-.вается вентиль 5. Через открытый ве тиль 5 импульсы генератора 3 эталон ной частоты поступают на вход делителя б частоты,на выходе которого ф мируётся последовательность импульс частоты ,ых оН о/ / х- бх782140локом 2 управления постоянно осущетвляется сравнение текущего и предествующего ему периодов входного сигала. Если в течение m периодов входого сигнала частота последнего осается постоянной, то на выходе умноителя формируется последовательность мпульсов частоты Ъых , -i бх сли, начиная с ()-го периода ходного сигнала, частота последнего зменилась и стала равна F. ем F(,)(C ьх(бх, бх то через время с момента окончания т-го периода ходного сигнала блоком 2 управления ткоывается на время ДТ ентиль 4,через который в реверсивый счетчик 9 вводят число импульсов д cf , равное целой части числа Дс(дм/лп),п,/к где ukN ДТ 0) остаток импульсов накопленный в делителе 7 частоты к моменту окончания (т+1)-го периода входного сигнала. В реверсивном счетчике 9 зафиксирован код числа По очередному выходному импульсу делителя 6 частоты блоком 2 управления вырабатывается сигнал, осуществляющий через блок 10 переноса перепись содержимого реверсивного счетчика 9 в регистр 11 (тем салим коэффициент деления делителя б частоты устанавливается равным д ). На выходе умножителя формируется последовательность импульсов частоты ) V 1/lr 1/(f4-un)(u N,)/K,,/(N i . /(NVNro)S/()VSbX,Обозначим f, - интервалы времени с момента изменения частоты входного сигнала до момента изменения частоты выходной импульсной последовательности умножителя. Очевидно, что 0- ьх ьо( « .ь..(. Тогда (N.AN,)T.,r,--MT(1t1/K «T. - быстродействие Обозначим М, (быстродействие - величина, обратная длительности переходного процесса или интервалу времени с момента изменения частоты входного сигнала или коэффициента умножения до момента изменения частоты выходной импульсной последовательности умножителя) известного дискретного умножителя частоты,M.ijf -быстродействие предлагаемого дискретного умножителя частоты, где Т„ - длительность переходного процесса в известном дискретном умножителе частоты. - .х/ 1и« 2 х/%ма;с 2Vo/E40 /4 Vo 2HJ N((i yAN;3 «2N,/()tN/14.2l(N,N/k,). H/ii.N, откуда unt2. Пусть в течение k периодов вхо ного сигнала частота последнего не изменялась и была равна Tj, , а нач ная с ( + l)-ro, периода входного сигнала частота последнего изменила и стала равна . причем , ( TfcXt , , Тогда по окончанию (m k -IJ-ro пе риода входного сигнеша код меньшего из чисел ,. .o4V;X/ o. или блока 2 управления заноситс:я в с матор 14.. Если дМ Nq то по сигналам бл ка 2 управления устанавливается в р жим вычитания реверсивный счетчик 9 и код числа (-К) пиз входного реги ра 12 заносится в сумматор 14, где числяется выражение AN,j - iK, После каждого занесения кода чис ла (-К) в сумматор 14 блоком 2 управления анализируется содержимое сумматора 14. AN - iK,7/0, то блоком 2 управления вырабатывает импульс, который через элемент ИЛИ поступает в реверсивный счетчик 9, уменьшая его содержимое на единицу. Так продолжается до тех пор, пок содержимое сумматора 14 не становит ся отрицательным, .т.е. при некотором г Дд AN,j-(Au2 1) где Дд,,- целая часть числа V 7/V V 2/li сигналам блока 2 управления к ды числа К, и (- Дп ) соответственно из входного регистра 12 и делителя 7 частоты поступают в сумматор 14, где вычисляется выражение C(An2- i V 2- Блоком 2 управления анализируется содержимое сумматора 14. Если - Дп Q, то по сигналам блока 2 управления код числа Д п - ( - Д п., ) из сумматора. 14 заносится в делитель 7 частоты, реверсивный счетчик 9, в котором зафиксирован код числа д 5 -дд .устанавливается в режим сумь«1рования и сумматор 14 устанавливается в исходное состояние. Если Aoj - un.j 7 О то по сигналам блока 2 управления код числа {-К.) из входного регистра 12 заносится в сумматор 14, где вычисляется выражение ( А П2 - Д Hj ) - K-I затем очищается делитель 7 частоты, код числа - С( лп - лп -К., иэ сумматора 14 переписывается в делитель 7 частоты и сумматор 14 устанавливается в исходное состояние.. Блоком 2 управления вырабатывается импульс, поступающий через элемент ИЛИ 8 в реверсивный счетчик 9, который после этого устанавливается в режим суммирования. В реверсивном счетчике 9 зафиксирован код числа дГ - 1, Если ДМ, 7 Nrj 9 то по сигналам блока 2 управления делитель 7 частоты и реверсивный счетчик 9 устанавливаются в исходное состояние/ код числа {-К-( ) из входного регистра 12 заносится в сумматор ,14, где вычисляется выражениеNZ - к; После каждого занесения Кода числа (-К) в сумматор 14 блоком 2 управления анализируется содержимое сумматора 14. Если Nj -lK.,;yOf то блоком 2 управления вырабатывается импульс, который через элемент ИЛИ 8 поступает в реверсивный счетчик 9, увеличивая его содержимое на единицу. . Так продолжается до тех пор,.пока содержимое сумматора не станет отрицательным, то есть при некотором i . N.- (дГ и) к, о g-sT целая часть целая часть числа /i ,- д-«.дп. По сигналам блока 2 управления код числа К из входного регистра 12 поступает в сумматор 14, где вычисляется выражение дп.V(чr)ti,-N,, и код числа дп заносится в делитель 7 частоты. В реверсивном счетчике 9 зафиксирован код числа д . После того, как в делитель 7 частоты Занесут код числа Дп, или код W--WX у у If числа , или код числа дпц и в реверсивном счет.чике 9 сформируется код числа д- , или код числа д , по очередному выходному импульсу делителя 6 частоты блоком 2 управления вырабатывается сигнал, осуществляющий переписьсодержимого рейерсивного счетчика 9 через блок 10 переноса в егистр 11 (тем самым коэффициент еления делителя 6 частоты устаяав- ивае.тся равным д .

На выходе умножителя формируется .последовательность импульсов частоты

а) .Г1.,-О

vv-v(v4,)vv(v l2)VV(ls-лv)v./(,)--.i,/(

5) 70

(v))

ьхг Tg., е заносятся в сумматор 14 где выисляется выражение ( ANjt Ang) - IK После каждого занесения кода чиса (-К) в сумматор 14 блоком 2 упавления анализируется содержимое сумматора 14. (ЛН,ч-ЛП), то блоком 2 уп)авления вырабатывается мпульс, который через элемент ИЛИ 8 поступает в реверсивный счетчик 9, величивая его содержимое на единицу. Так продолжается до тех пор, пока содержимое сумматора 14 не станет отрицательным, т.е. при некотором i (лдГа-И) ( t.N2,f-un) - () где ig - целая часть числа ь() в этом случае по сигналам блока 2 управления код числа К. из входного регистра 12 заносится в сумматор 14, где вычисляется выражение (AM.,&n)(i.,ti)K,tl,Ah,,, код числа из сумматора 14 заносится в делитель 7 частоты, и сумматор 14 устанавливается в исходное состояние. . В делителе 7 частоты и реверсивном счетчике 9 зафиксированы коды чисел . . ли,(йМ,лп)-&я,,1с, Ъ Ч2 ЬЕсли знак приращения отрицательный, то код Числа из блока 2 управления заносится в сумматор 14, по сигналам блока 2 управления устанавливается в режим вычитания реверсивный счетчик 9 и код числа (-К,) из входного регистра 12 заносится в сумматор 14, где вычисляется выражение - i К.у После каждого занесения кода числа (-К.) в сумматор 14 блоком 2 управления анализируется содержимое сумматора 14. Если ANj - , то блоком 2 управления вырабатывается импульс, который черач элемент ИЛИ 8 поступает в реверсивный счетчик 9, уменьшая е содержимое на единицу. Так продолжается до тех пор, пок содержимое сумматора 14 не станет о рицательным, т.е. при некотором i ,- (лд +1) AN. 3 целая часть числа где д ( .,/К,Д,,,. По сигналам блока 2 управления коды чисел KI и(- дп) соответственно из входного регистра 12 и делителя 7 частоты поступают в сумМатор 14, где вычисляется выражение е()К,3-дП . . Блоком 2 управления анализируетс содержимое сумматора 14. Если , то по сигналам блоки 2 управления код числа Л.п .-(Дп - Лп) из сумматора 14 заносится в делитель 7 частоты, реверсивный счетчик 9, в котором зафиксирован код числа д §2 - Ag,j , ус танавливается в режим суммирования и сумматор 14 устанавливается в исходное состояние. Если Лп - , то по сигнсша блока 2 управления код числа (-К) из входного регистра 12 заносится в

1&Nj,-70

/4ьV /(,/()v,/

2& N,iO

toitj а)

()())Kj(T,-AT,)ic,/r

S) u., ;/4Г- а 1/(Х - ь ь Обозначим j, - интервал времени с момента подачи на вход дискретного умножителя частоты сигнала цифровой код до момента изменения частоты вы ходной импульсной последовательности Очевидно, что ,4Т, « rubix Vo/. .(4Vl,)/K,; () ° iЯ:V V 1. .,jMax -Vo/ n /М Т 1 2.Т yt- пм. .,,,1 -iwm пмак Ьмпх , Ьмдх ,. Рассмотрим работу предлагаемого дискретного умножителя частоты П1зй изменении коэффициента умножения. Пусть дискретный умножитель частоты формирует импульсную последоваь.

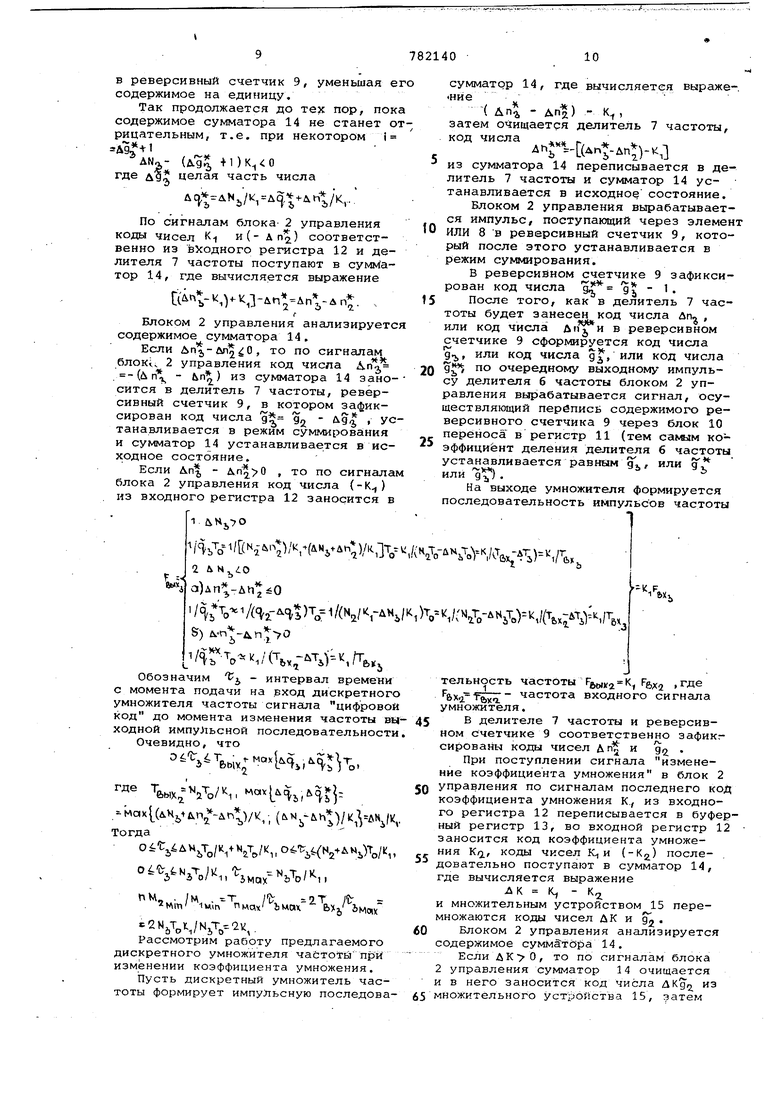

. сумматор 14, где вычисляется выраже-. ние 1 Лп - лп) - К , затем очищается делитель 7 частоты, „о„ ™сл, „..,.(,„..,„,., из сумматора 14 переписывается в делитель 7 частоты и сумматор 14 устанавливается в исходно состояние. Блоком 2 управления вырабатывается импульс/ поступающий через элемент ИЛИ 8 в реверсивный счетчик 9, который после этого устанавливается в режим суммирования. В реверсивном счетчике 9 зафиксирован код числа Ux Эь После того, как в делитель 7 частоты будет занесен код числа Дп, , .yt. или код числа дпХ и в реверсивном счетчике 9 сформируется код числа gn,, или код числа gJ, или код числа ° очередному выходному импульсу делителя 6 частоты блоком 2 управления вырабатывается сигнал, осуществляющий перйпись содержимого реверсивного счетчика 9 через блок 10 переноса в регистр 11 (тем коэффициент деления делителя 6 частоты устанавливается равным gj,, или д или д . На выходе умножителя формируется последовательность импульсов частоты «1 Fi6X2 тельность частоты ьхз ...- - частота входного сигнала . умножителя. В делителе 7 частоты и реверсивном счетчике 9 соответственно зафикг сированы коды чисел Д ris и При поступлении сигнала изменение коэффициента умножения в блок 2 управления по сигналам последнего код коэффициента умножения К., из входного регистра 12 переписывается в буферный регистр 13, во входной регистр 12 заносится код коэффициента умножения K/i, коды чисел К, и (-К) после- . довательно поступают в сумматор 14, где вычисляется выражение ЛК 1C, - К, и множительным устройством 15 перемножаются коды чисел ДК и д. Блоком 2 управления анализируется содержимое суммйтбра 14. Если , то по сигналам блока 2 управления сумматор 14 очищается и в него заносится код числа ДКд из множительного Устройства 15, атем

11

78214012 код числа Лп из делителя 7 частоты и код числа (Кп) из входного регистра 12 последовательно поступают в сумматор 14, где вычисляется выражение . ... . , , - - :- -- - (лкglг - n) - к Блоком 2 управления анализируется содержимое сумматора 14. . . Если (AKg- H-Anf) - KjiiO, т.е. (Mg-jifAn) 4 Kg , то по сигналам блока 2 управления код числа К из входного регистра 12 пос тупает в сумматор 14, где вычисляется выражение . Делитель 7 частоты очищается и в нег заносится содержимое сумматора 14. В реверсивном счетчике 9 эафиксиррван код числа д. ЕСЛИ (АКд; ) - К,, О , т.е. Z блоком 2 управления вырабатывается импульс, пос тупающий через элемент ИЛИ 8 в ревер сивный счетчик 9 и увеличивающий его содержимое на единицу. Затем по сигналам блока 2 управления код числа (-К),из входного регистра 12 заноситсяв сумматор 14 где вычисляется выражение (,)-1к,,. После каждого занесения кода числ (-Kj) в сумматор 14 блокбм 2 управления анализируется содержимое сумма тора 14 и, если ()-йk;2 o, , то блоком 2 управления вырабатывает ся импульс, который через элемент ИЛИ 8 в реверсивный счетчик 9, увеличивая его содержимое На единицу. Так продолжается до тех пор, пок при некотором i () содержимое . сумматора 14 не станет отрицательны т.е. при I ( Да + 1) {АКд,--AnJ)-(Ag;|- -l)K2 0. В этом случае по сигналам блока управления код числа Kg из входного регистра 12 поступает в сумматор 14 где вычисляется (дЦа- а)-. делитель 7 частоты очищается, И в н го переписывается содержимое сумматора 14, который затем также очищается. В реверсивном счетчике 9 зафикси рован код числа gJ gn-t-Р: 4 Если ДК О, то по сигналам блока 2управления сумматор 14 очищается и в него заносится код числа (-ДКд из множительного устройства 15, затем код числа д ri из делителя 7 Ча тоты поступает в сумматор 14, где вычисляется выражение Лп - Блоком 2 управления анализируется содержимое сумматора 14. Если Дп -АК§2 0 то по сигнала лока 2 управления делитель 7 частоы очищается, в него заносится из умматора 14 код числа An;JtAh -Ali,j,, затем сумматор 14 очищается. В реверсивном счетчике 9 зафиксиован код числа . Если.&п -MgJji O, то по сигналам лока 2 управления реверсивный счетик 9 переводится в режим вычитания код чидла входного регистра 12 оступает в сумматор 14, где вычисяется выражение ()После каждого занесения кода числа j в сулвиатор 14 блоком 2 управления нализируется содержимое сумматора 4, и если то блоком 2 управления вырабатывается импульс, который через элемент ИЛИ 8 поступает на вход реверсивного счетчика 9, уменьшая его содержимоё на единицу. Так продолжается до тех пор, пока при некотором i()содержимое сумматора 14 не станет положительным (л 4-1) Vd,j,4-(д fci J,) 70. в этом случае по сигналам блока 2 управления реверсивный счетчик 9 устанавливается: в режим cy Ф иpoвaния, код числа {-Kg.) из входного регистра 12 заносится в сумматор 14, где вычисляется выражение дп;.,.(,), Делитель 7 частоты очищается и в него переписывается код числа сумматора 14, который затем также очищается. В реверсивном счетчике 9 зафиксирован код числа IVM. А- Если при изА нении коэффициента умножения АК о, то по сигналам блока 2 управления код числа (-«л) из входного регистра 12 поступает в сумматор 14, где вычисляется овыражение (ДК-Кд). Содержимое сулматора 14 анализируется блоком 2 управления. Если (ДК - Ki)iO, то код числа К из входного регистра 12 поступает в сумматор 14, где вычисляется (ДК,-К + . Дальнейшая работа дискретного умножителя частоты для случая , (причем ) описана выше. Если (ДК - Kj) О, то по сигналам блока 2 управления очищается сумматор 14 и множительное устройство 15, код числа К из буферного регистра 13 поступает в сумматор 14, множительным устройством 15 перемножаются коды К и cfg, сумматор 14 очищается и в него переписывается содержимое множиТельного уатройства 15, код числа дп из делителя 7 частоты поступает в су |матор 14, где вычисляется Njt К, д ,-лп делитель 7 частоты и реверсивный делитель 7 частоты и реверсивный сче чик 9 очищаются, и затем код числа (-Kj) их входного регистра 12 заносится в сумматор 14, где вычисляется выражение i Kij. После каждого занесения кода числа (-Kj) в сумматор 14 блрком 2 управления анализируется содержимсЗе сумматора 14 и если N2- К,0, То блоком 2 управления вырабатывается импульс, который через элемент ИЛИ 8 поступает в реверсивный счетчик 9, увеличивая erci содержимое на единицу. Так продолжается до теХ пор, пока при некотором i -gJTVl Nj.-() . где g - целая часть числа д. В этом случае по сигналам блока 2 управления код числа Kj, из входного л. .iv.5 ,,., 6)sK3j,.n, ,(( 1/t v( ri i a/ K/4Fo -V(V)V 2/«2V C2. AUtO a) i n -6tc,,7/o Vfe-V e,v

e),

V4: V vcV) V ))

. Обозначим j - интервал времен с момента подачи на вход дискретно умножителя частоты сигнала Измене коэффициента умножения до момента менения частоты выходной импульсно последовательности, Очевидно, что О4% :махHvi . , MW .4, Ц i , bwx.: b4.J .ых/ Ьхгг 1.1 J1IJJ L Тогда (. ()/( ..««/.,(f 2)(,-ii,,/(k;,4k2). .регистра 12 поступает в сумматор 14, где вычисляется Г . Ч- и код числа сумматора 14 заносится в делитель 7 частоты. В реверсивном счётчике 9 зафиксирован код числа 9. После того, как в реверсивном счетчике 9 и делителе 7 частоты будут сформированы коды, соответствующие заданному изменению коэффициента умножения, по очередному выходному импульсу делителя б частоты блоком 2 управления вырабатывается сигнал, осуществляющий перепись содержимого реверсивного счетчика 9 через блок 10 переноса в регистр 11. На выходах умножителя формируется последовательность импульсов частоты1 i., i/(ii,-eK,)i/2.id2, oтl:y a h7/v: 2.., V(tii tl) 6 /2 kL,, от1суд.а . в отличии от известных-дискретных умножителей частоты на выходе предлагаемого дискретного умножителя частоты отсутствует переходный процесс при смене установившегося режима генерации одной выходной частоты установившимся режимом генератора другой выходной частоты. Существует время задержки (,i -) с момента изменения входной частоты умножителя (подачи на вход умножителя сигнала цифровой код) или коэффициента умножения до момента изменения выходной частоты умножителя, в течение которого последним генсрируется выходная частота, предшествующая изменению входной частоты умножителя (подаче на вход умножителя сигнала цифровой код) или коэффициента умножения.

Использование новых элементов реверсивного счетчика, входного регистра, буферного регистра, сумматора и множительного устройства позволяет повысить быстродействие дискретного умножителя частоты и устранить переходный процесс на выходе дискретного умножителя частоты при изменении частоты входного сигнала или коэффициента умножения. -.

формула изобретения

Дискретный умножитель частоты, содержащий последовательно соединенные формирующее устройство и блок управления, генератор эталонной частоты, выход которого соединен со входами делителей частоты через соответствующие вентили, другие входы которых подключены к выходу блока управления, регистр, блок переноса и элемент ИЛИ, отличающийся тем, что, с целью повышения быстродействия в него введены реверсивный счетчик, входнойи буферный регистры, сумматор и множительное устройство, при

изменение К

Ънок d /V ЦиФробагО

этом входной регистр, буферный регистр, сумматор,первый делитель частоты, элемент ИЛИ, реверсивный счётчик, блок переноса, регистр и второй делитель частоты соединены последовательно, к выходу блока управления подключены входы формирующего устройства, делителей частоты регистра, элемента ИЛИ, реверсивного счетчика блока переноса,.множительного устройства, входного регистра, буферного регистра и сумматора, выход генератора эталонной частоты соединен со вторым входом блока управления, выход второго Делителя частоты - с третьим входом блока управления, выход первого делителя частоты - со входом сумматора, выход реверсивного счетчика - со вторым входом множительного устройства, выход входного регистра - со входами первого делителя частоты и сумматора, а выход сумматора - с четвертым входом блока управления и с третьим- входом множительного устройства, выход которого подключен ко входу сумматора.

Источникиинформации, принятые во внимание при экспертизе 1. Смеляков В. В. Цифровая измерительная аппаратура инфранизких частот. М., Энергия, 1975. с. 37, рис. 2-1.

Авторы

Даты

1980-11-23—Публикация

1978-01-06—Подача