(54) УСТРОЙСТВО ДЛЯ ВЮДА ИНФОРМАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации | 1979 |

|

SU911500A2 |

| Буферное запоминающее устройство | 1980 |

|

SU932566A1 |

| Буферное запоминающее устройство | 1979 |

|

SU822287A1 |

| Программируемый генератор импульсов | 1985 |

|

SU1575295A1 |

| Устройство для ранжирования чисел | 2022 |

|

RU2792182C1 |

| Устройство тестового контроля | 1982 |

|

SU1075265A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство для ввода информации | 1981 |

|

SU989555A1 |

| Устройство для сопряжения вычислительной машины с устройством ввода изображения | 1985 |

|

SU1260967A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

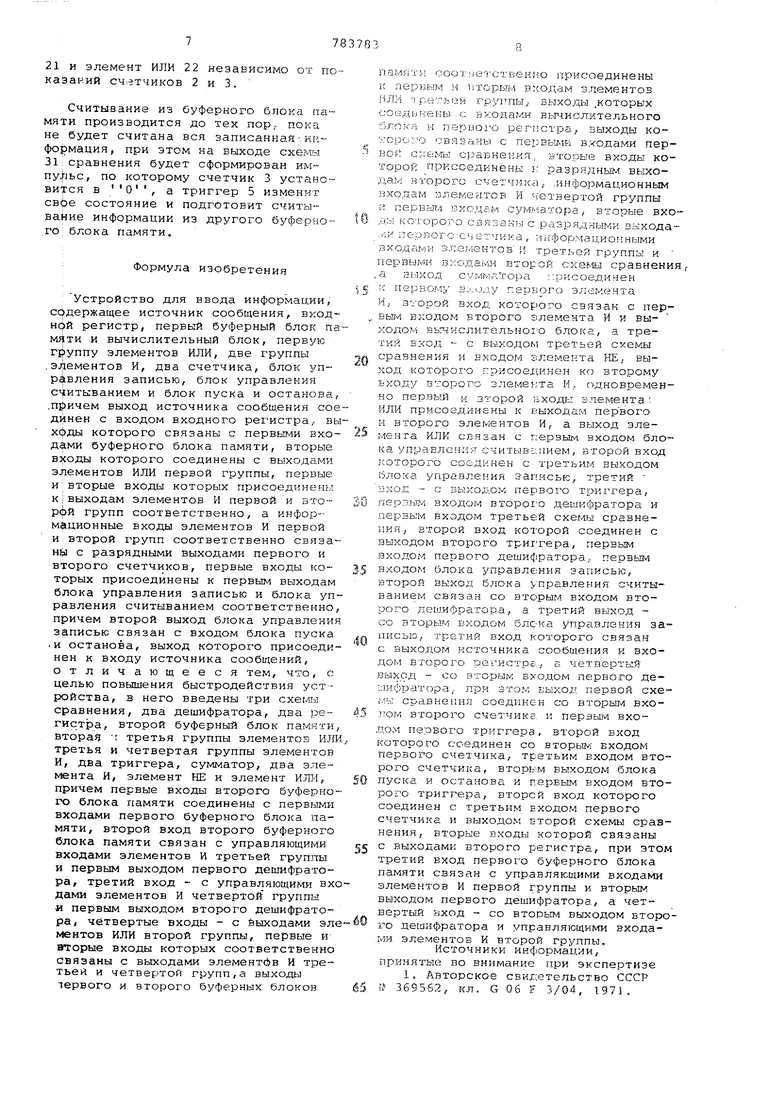

Изобретение относится к области вычислительной техники и может быть использовано для обработки цифровой информации, записанной н§ магнитной ленте и других носителях информации Известно устройство для ввода информации, содержащее блок совпадения блок формирования тактовых импульсов регистр строки, дешифратор четности блок контроля, блок перезаписи информации и блок связи il- В данном устройстве информация считывается с магнитной ленты и вводится в ЭВМ построчно. Основным недостатком этого устройства является недостаточное эффективное использование процессора ЭВМ из-за загрузки его в течение всего времени считывания информации Известно также устройство, в состав которого входят буферный блок па мяти, четыре регистра, триггер, прео разователь кодов, блок управления и блок считывания 2. В данном устройстве информация сначала вводится в буферный блок памяти. После заполнения буферного бло ка памяти производятся прерывание работы вычислителя (ЭВМ), ввод массива 43 буферного блока памяти и обработка введенной информации. Обработка должна быть закончена до момента ввода в вычислитель очередного массива информации. К недостаткам устройства следует отнести ограничения, накладываемые на обработку информации, так как время обработки должно быть меньше времени ввода информации. Наиболее близким по техническому решению к изобретению является устройство для ввода информации, содержашее входной регистр, буферный блок памяти, состоящий из накопительного блока, регистра адреса и блока управления, вычислительный блок, два счетчика, элементы И и ИЛИ, два дешифратора и блок местного управления, состоящий из блоков местного управления записи и считывания и схемы пуска и останова |3J. Однако в этом устройстве ввод информации из буферного блока памяти начинается лишь после того, как заполнена его половина, что очень неэффективно при работе в реальном времени, так как при этом сокращается время обработки и затрудняется реализация программ реального времени. Цель изобретения - повышение быстродействия устройства. Это достигается тем, что в устрой ство для ввода информации, содержаще источник сообщения, входной регистр, первый буферный блок памяти, вычисли тельный блок, первую группу элементо ИЛИ, две группы элементов И, два сЧетчика, блок управления записью, блок управления считыванием и блок пуска и останова, причем выход источ ника сообщения соединенс входом входного регистра, выходы которого связаны с первыми входами буферного блока памяти, вторые входы которого соединены с выходами элементов ИЛИ первой группы, первые и вторые входы которых присоединены к выходам элементов И первой и второй групп соот ветственно, а информационные входы элементов И первой и второй групп соответственно связаны с разрядными выходами первого и второго счетчико первые входы которых присоединены к первым выходам блока управления записью и блока управления считыванием соответственно, причем второй выход блока управления записью связан с входом блока пуска и останова Е|ЫХОД которого присоединен к входу Источника сообщений, введены три Схемы сравнения, два дешифратора, два регистра, второй буферный блок Памяти, вторая и третья группы элементов ИЛИ, третья и четвертая группа элементов И, два триггера, сумматор, два элемента И, элемент Н и элемент ИЛИ. При этом первые вход второго буферного блока памяти соединены с первыми входами первого бу ферного блока памяти, второй вход второго буферного блока памяти связан с управляющими входами элементо И третьей группы и первым выходом Первого дешифратора, третий вход с управляющими входами элементов И Четвертой группы и первым выходом второго дешифратора, четвертые входы - с выходами элементов ИЛИ второй ГРУ „ты, первые и вторые входы которых соответственно связаны с вы ходами элементов И третьей и четвертой групп. Выходы первого и втор го буферных блоков памяти соответственно присоединены к первым и вто рым входам элементов ИЛИ третьей группы, выходы которых соединены с входами вычислительного блока и пер вого регистра, выходы которого связ ны с первыми входами первой схемы сравнения, вторые входы которой под ключены к разрядным выходам второго счетчика, информационным входам эле ментов И четвертой группы и первым входам сумматора, вторые входы кото рого связаны с разрядными выходами первого счетчика, информационными входами элементов И третьей группы и первыми входами второй схемы сра нения. Выход сумматора присоединен к первому входу первого элемента И, второй вход которого связан с первым входом второго элемента И и выходом вычислительного блока, а третий вход с выходом третьей схемы сравнения и входом элемента НЕ, выход которого присоединен ко второму входу второго элемента И. Одновременно первый и второй входы элемента ИЛИ присоединены к выходам первого и второго элементов И, а выход элемента ИЛИ связан с первым входом блока управления считыванием, второй вход которого соединен с третьим выходом блока управления записью, третий вход - с выходом первого триггера, первым входом второго дешифратора и первым входом третьей схемы сравнения, второй вход которой соединен с выходом второго триггера, первым входом первого дешифратора, первым входом блока управления записью. Второй .выход блока управления считыванием связан со вторым входом второго дешифратора,а третий выход - со вторым входом блока управления записью, третий вход которого связан с выходом источника сообщения и входом второго регистра, а четвертый выход - со вторым входом первого дешифратора. При этом выход первой схемы сравнения соединен со. вторым входом второго счетчика и первым входом первого триггера, второй вход которого соединен со вторым входом первого счетчика, третьим, входом второго счетчика, вторым выходом блока пуска и останова и первым входом второго триггера, второй, вход которого соединен с третьим входом первого счетчика и выходом второй схемы сравнения, вторые входы которой связаны с выходами второго регистра. При этом третий вход первого буферного блока памяти связан с управляющими входами элементов И первой группы и вторым выходом первого дешифратора, а четвертый вход со вторым выходом второго дешифратора и управляющими входами элементов И второй группы. На чертеже представлена блок-схема устройства. Устройство содержит блок 1 пуска и останова, счетчики 2 и 3, триггеры 4 и 5, источник 6 сообщения, входной регистр 7, регистр 8, буферные блоки 9 и 10 памяти, блок 11 управления записью, дешифратор 12, первые группы элементов И 13 и элементов ИЛИ 14, вторые группы элементов И 15 и элементов ИЛИ 16, вторую схему 17 сравнения, вычислительный блок 18, третью схему 19 сравнения, элементы И 20, НЕ 21, И 22 и ИЛИ 23, блок 24 управления считыванием, дешифратор 25, вторую и четвертую группы элементов И 26 и 27, первую группу элементов ИЛИ 28, регистр 29, сумматор 30 и третью схему 31 сравнения. Работает устройство следующим образом. Перед началом ввода информации по сигналу из блока 1 пуска и остано ва счетчики 2,3 и триггеры 4,5 устанавливаются в исходное состояние (О). Счетчик 2 используется для формирования адреса, по которому производится запись информации, а счетчик 3 - для формирования адреса, цо которому осуществляется считывани Объем БЗУ выбирается таким, чтобы в него можно было бы полностью записать информацию одного буферного бло ка памяти. По сигналу, поступающему от блока 1пуска и останова на.источник б сообщения, производится запуск источника (например, при вводе информации с накопителя на магнитной ленте производится пуск лентопротяжного механизма) . Информация из источника сообщения поступает на информационные входы входного регистра 7 и регистра 8, Во входном регистре 7 каждое информационное слово запоминается на время записи его в одном из буферных блоков 9 и 10памяти, а в регистр 8 Заносится информация о количестве информационных слоев в одном кадре. После записи во входном регистре 7 информационного слова в блоке 11 управления записью по сигналу из источ ника б сообщения формируется импульс разрешения записи, поступающий на управляющий вход дешифратора 12, на разрядный вход которого подается сиг нал с выхода триггера 4, при этом на одном из выходов дешифратора 12 формируется импульс. При записи в буферный блок 9 памя ти этим импульсом открываются элементы И группы 13 и выходы счетчика 2через элементы И группы 13 и элементы ИЛИ группы 14 подключаются к входам адреса буферного блока 9 памяти, в него производится запись информации. Аналогично при записи блок 10 открываются элементы И группы 15 и адрес с разрядных выходов счетчика 2проходит через элементы И группы 1 и элементы ИЛИ группы 16 на вход бло ка 10. После записи информационного слова к показаниям счетчика 2 прибав ляется 1 и в счетчике устанавливается адрес, по которому будет запи сываться следующее информационное сл во. Запись в какой-либо буферный блок памяти производится до тех пор, пока не будет записано последнее информационное слово кадра, при этом показания счетчика 2 регистра 8 будут одинаковые и импульсом с выхода схемы 17 сравнения триггер 4 перейдет 3другое положение, что соответствуе записи в другой блок памяти, а счет:чик 2 устанавливается в соответствует начальному адресу. Считывание информации с буферного блока памяти производится по импульсам запрета, поступающим из вычислительного блока 18. При этом считывание возможно только при наличии в блоке записанной и еще несчитанной информации. Возможны два случая В первом случае считывание ведется из того буферного блока памяти, в котором в данный такт записывается информация, во втором случае считывание и запись ведутся в разных блоках. Если считывание производится из того же блока, в который произведена запись, то на выходах схемы 19 сравнения формируется сигнал, разре11:ающий прохо5гсдение через элементы И 20 (первый случай). Если считывание ведется из другого блока, то разрешающий сигнал с выхода элемента НЕ 21 поступает на элемент И 22. В первом случае импульсы запроса проходят Через элементы И 20, ИЛИ 23 на вход блока 24 управления считыванием, в котором формируется импульс разрешения считывания, поступающий на управляющий вход дешифратора 25. В зависимости от того, из какого блока памяти должно производиться счи- . тывание, на одном из выходов дешифратора 25 формируется импульс. Выход считывания счетчика 3-либо через элементы И группы 26 и элементы ИЛИ группы 14 подключается к адресным входам блока 9 и информация считывается из него, либо через элементы И группы 27 и элементы ИЛИ группы 16, подключенные к адресным входам блока 10. После считывания информационного слова к показаниям счетчика 3 прибавляется 1 и в счетчике устанавливается адрес для считывания следующего информационного слова. Считанная информация проходит через элементы ИЛИ 28 на вход вычислительного блока 18- и на вход регистра 29, в котором запоминается количество слов в информационном кадре. Считывание из -блока памяти может производиться только в том случае, если показания счетчика 2 будут больше показаний счетчика 3, т.е. если в блоке записано информации не меньше, чем считано. Сравнение показаний счетчика производится при помощи сумматора 30, на вход которого подается код счетчика 3 в прямом коде, а код счетчика 2 - в дополнительном, при этом, если показания счетчика 3 меньше, то перенос на выходе сумматора отсутствует и на вход элемента 20 поступает сигнал, разрешающий прохождение импульсов запроса информации. Во втором случае импульсы запроса информации проходят череу эпрмент И

1 и элемент ИЛИ 22 независимо от поазаний счетчиков 2 и 3.

Считывание из буферного блока паяти производится до тех пор. пока е будет считана вся записанная-ИЕ о1;)мация, при этом на выходе схемы 1:сравнения будет сформирован имyjibc, по которому счетчик 3 устаноится в О, а триггер 5 изменит вое состояние и подготовит считыание информации из другого буферноо: блока памяти.

- Формула изобретения

Устройство для ввода информации, содержащее источник сообщения, входной регистр, первый буферный блок памяти и вычислительный блок, первую группу элементов ИЛИ, две группы элементов И, два счетчика, блок упрфвления записью, блок управления считыванием и блок пуска и останова, .п)ичем выход источника сообщения соединен с входом входного регистра,, выхфды которого связаны с первы /1И вход ми буферного блока памяти, вторые входы которого соединены с выходами элементов ИЛИ первой группы, первые и вторые входы которых присоединены к I выходам элементов И первой и второй групп соответственно, а инфор-мационные входы элементов И первой и второй групп соответственно связаны с разрядными выходами первого и второго счетчиков, первые входы которых присоединены к первым выходам блока управления записью и блока управления считыванием соответственно, причем второй выход блока управления записью связан с входом блока пуска и останова, выход которого присоединен к входу источника сообщений, отличающееся тем, что, с Ц|елью повышения быстродействия устройства, в него введены три схеглы сравнения, два дешифратора, два ре-гист эа, второй буферный блок , вторая : третья группы элементов ИЛИ,, третья и четвертая группы элементов И, два триггера, сумматор, два элеNKHTa И, элемент НЕ и элемент ИЛИ, причем первые входы второго буферного блока памяти соединены с первглми входами первого буферного блока памяти, второй вход второго буферного блока памяти связан с управляющими входами элементов И третьей группы и nepBfcjM выходом первого дешифратора, третий вход - с управляющими входами элементов И четвертой группы и первым выходом второго дешифратора, четвертые входы - с йыходами элементов ИЛИ второй группы, первые и Вторые входы которых соответственно связаны с выходами элементов И третьей и четвертой групп,а выходы тервого и второго буферных блокозз

памяти cooi-jiaTCTEeHHo присоединены V. пер}зьм и пторим в; :одам злементов ИЛИ -грвльей группы,, выходы .которых соедькекы с входами вы -гислительного блока н nepBoiO репгстра, выходы ко:срог-о связаны с первыми входами первой c:.;:evb сравкеккя, вторые входы которой /зрисосдинены к разря,цным выходам второго счетчика- .информационным входам злекентов И ieтвepтoй группы и первым входам сумматора вторые вх дь; которого связакг с разрядными выходалк первого-счетчика, информационными )эходами злемектоБ И третьей группы и перв.ими в ::одами второй схемы сравнен а выход суммг.гора г.рисоединен к первом Е,-.о.ау первого элемента И, второй вход KOiOf oro связан с первьам входом второго элемента И и выходом вьгчислительнохо блока, а третий Бкод - с выходом третьей сравнения и ЕХОДОМ зглемента НЕ,, выход которого присоединен ко второму входу второго элемента И. одновременно первый к второй входы злемента . ИЛИ присоединены к выходам первого и второго элементов И, а выход злемента ИЛИ связан с первым входом блока управлен;1я считыв тлием, второй вход которого соедигтвн с третьим выходом блока угфавления записью, третий вход - с выходом первого трихтера. nep3hi.i входом BTopoiO дешифратора и первым входом третьей схеглы сравнения, второй вход которой соединен с выходом второго тригтера, первым входом первого дешифратора, nepBHii Бходом блока управления записью, второй выход блока управле гия считыванием связан со вторым входом второго дешифратора, а третий выход со вторым входом блока управления записью, третий вход которого связан с выходом источника сообш,екия и входом второго регистра; а четвертый выход - со втсрым входом первого де лиФратораJ. при этом выхо;; первой схемы сравнения соедннен со вторыти входом второго счетчика, и перзы У1 вхо,пом первого триггера, второй вход которого соединен со вторым входом первого счетчика, третьим входом второго счетчика, вторь м выходом блока пуска и останова и первььм входом второго триггера, втореи вход которого с,оединен с третьим входом первого счетчика и выходом Еторой схемы сравнения, вторые входы которой связаны с выходами второго регистра, при это третий вход первого буферного блока памяти связан с управляющими входами элементов И первой группы и вторым выходом первого дешифратора, а четвертый вход - со вторым выходом вторго дешифратора и управляющими входами элементов И второй группы.

Источники информации, принятые но внимание при экспертизе

1, Авторское свидетельство СССР 369562, кл, G Об F 3/04, 1971. 2. Майоров С.А.,Николаев Г.И,, Структура цифровых вычислительных машин.Л. .Машиностроен1 е ,1970,с. 357-360, 3. Авторское свидетельство СССР № 378832, кл. G Об F 3/04, 1970 (прототип) .

Авторы

Даты

1980-11-30—Публикация

1979-01-04—Подача