I

I Изобретение относится к вычислиI тельной технике, а именно к устройствам для обработки и хранения цифровой информации, и можетбыть использовано при необходимости согласования устройств, работающих с различным темпом обработки информации.

Известно устройство для сопряжения блоков памяти, которое содержит блок памяти, группы вентилей, формирователи адреса записи и считывания, элемент задержки и формирователи импульсов l.

Недостатком известного устройства является его низкое быстродействие, т.е. чтение информации из БЗУ и обработка ее начинается только после того, как в БЗУ введен обрабатываемый информационный массив.

Известно устройство ввода информации , которое содержит буферное запоминающее устройство, состоящее из накопительного блока, регистра адреса и блока угфавления, входного регистра.

источника сообщения, вычислительного блока, двух счетчиков, двух схем И, группы схем ИЛИ, двух дешифраторов и блока местного управления, состоящего из блоков местного управления-записи считывания 2J.

Недостатком данного устройства является то, что вывод информации из БЗУ производится лишь после того, как заполнена его половина, что увеличив вает время обработки информации.

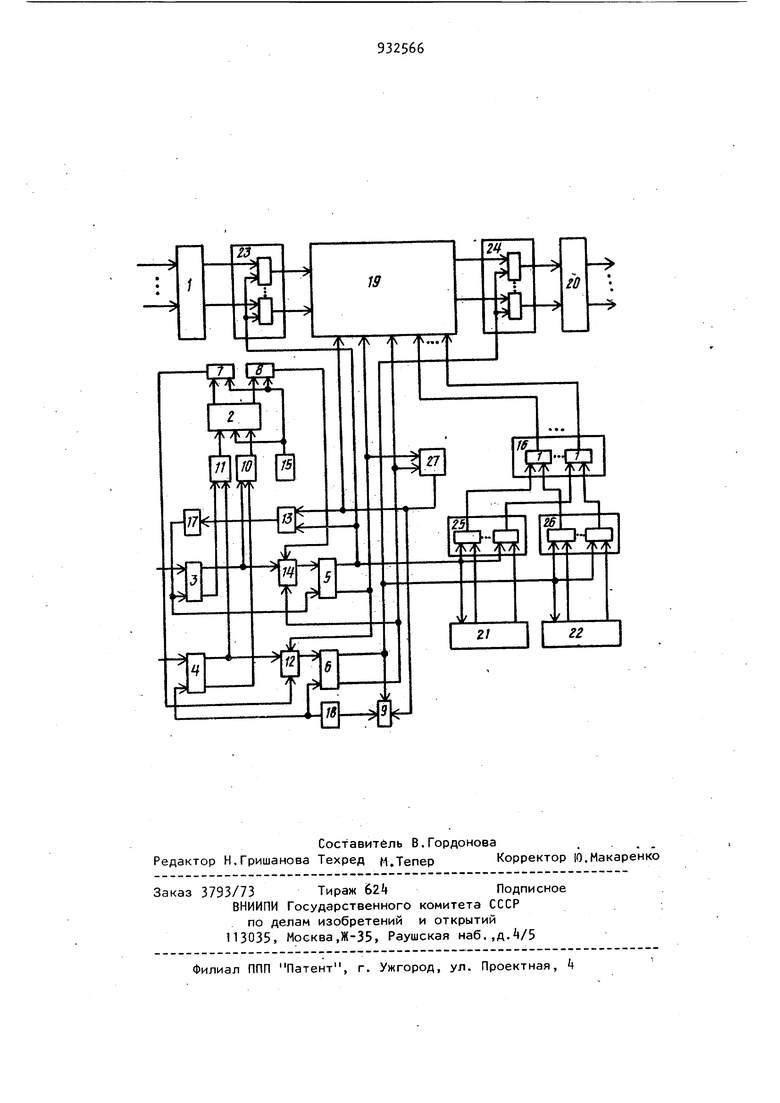

Наиболее близким по технической сущности к предлагаемому является буферное запоминающее устройстве, в состав которого входят блок управления, генератор импульсов, входной регистр, две группы элементов И, группа элементов ИЛИ, матрица оперативной памяти, выходной регистр, счетчики адресов записи и считывания и дешифратор адреса. Генератор импульсов непрерывно вырабатывает последовательность импульсов записи и считывания, сдвинутые на полпериода. Oneрация записи и считывания осуществляется синхронно по сигналам ЗАПИСЬ и СЧИТЫВАНИЕ, поступающим от источника и приемника сообщений соответственно, при этом при поступлении указанных сигналов в блоке управления формируются стробирующие сигналы, синхронные импульсам записи и считывания. При поступлении одного из стробирующих сигналов код с выхода соответствующего счетчика поступает на дешифратор адреса, выходы которого соединены с адресными входами матрицы оперативной памяти. При возбуждении соответствующих адресных шин матрицы обеспечивается обращение к матрице по выбранному адресу. Одновременно из стробирующих импульсов формируются стробы записи и считывания и тактовые импульсы счетчиков Недостатком данного устройства является то, что как скорость записи, так и скорость считывания в два раза ниже максимально возможной ля выбран ного типа оперативной памяти, что зна чительно увеличивает время ввода и вывода из буферного запоминающего уст ройства при асинхронном режиме записи и считывания, а, следовательно и времени обработки. Цель изобретения - повышение быстродействия буферного запоминающего устройства. Поставленная цель достигается тем что буферное запоминающее устройство содержащее накопитель, информационные входы которого подключены к выходам элементов И первой группы, а i выходы накопителя подключены к одним входам элементов И второй группы, вы ходы которых подключены к входам выходного регистра, одни входы элементов И первой группы подключены к выхо дам входного регистра, группу элемен тов ИЛИ, выходы которых подключены к адресным входам накопителя, одни вхо ды элементов ИЛИ группы подключены к выходам элементов И третьей группы, одни входы которых подключены к информационным выходам счетчика адресов записи, другие входы элементов ИЛИ группы подключены к выходам элементов И четвертой группы, одни входы которых подключены к информационным выходам счетчика адресов считы вания, блок управления, выход которо го подключен к первому управляющему входу накопителя, генератор импульсо содержит триггеры, элементы задержки И.элементы И, первые входы первого и второго элементов И подключены к выходу генератора импульсов, вторые входы первого и второго элементов И подключены к соответствующим выходам первого триггера, первый вход которого подключен к выходу генератора импульсов, а второй и третий входы соответственно к выходам третьего и четвертого элементов И, первые входы которых подключены к первым выходам Соответственно второго и третьего триггеров, первые входы -которых являются соответствующими управляющими входами устройства, вторые входы третьего и четвертого элементов И подключены к вторым выходам соответ ственно второго и третьего триггеров, первые входы пятого и шестого элементов И подключены к выходу блока управления, первый вход которого подключен к первому выходу четвертого триггера, к первому входу седьмого элемента И и к второму управляющему входу накопителя второй вход блока управления подключен к первому выходу пятого триггера, к первому входу восьмого элемента И и к третьему управляющему входу накопителя, второй выхдд четвер того триггера подключен к второму вхо ду шестого элемента И, к другим входам элементов И первой и третьей группы и к счетному входу счетчика ад реса записи, второй выход пятого триггера подключен к второму входу пятого элемента И, к другим входам элементов И второй и четвертой групп и к счетному входу счетчику адреса считывания, выход шестого элемента И подключен к входу первого элемента задержки, выход которого подключен к второму входу второго триггера и к первому входу четвертого триггера, выход пятого элемента И подключен к входу второго элемента задержки, выход которого, подключен к второму входу третьего триггера и к первому входу пятого триггера, вторые входы седьмого и восьмого элементов И подключены к выходам соответственно первого и второго элементов И, третьи входы седьмого и восьмого элементов И подключены к первым выходам соответствен но третьего и второго триггеров, а вь1ходы седьмого и восьмого элементов И подключены к вторым входам соответственно пятого и четвертого триггеров На чертеже приведена структурная схема устройства. В состав устройства входят вход ной регистр 1, триггеры 2-6 элементы И У-, генератор 15 импуг.ьсов, группа элементов ИЛИ 16, элементы за держки 17 и 18, накопитель 19, выход ной регистр 20, счетчик 21 адресов записи, счетчик 22 адресов считывания, группа элементов И 23-26 и блок 27 управления. Устройство работает следующим образом. При подаче на первый вход триггер 3 сигнала ЗАПИСЬ {или импульса сопро вождения входной информации) триг- гер 3 устанавливается в состояние 1. Если сигнал ЧТЕНИЕ (импульс зап /роса информации) на входе триггера k отсутствует, то триггер l находитс в состоянии О, и на выходе элемента И 10 формируется импульс, который устанавливает триггер 2 в состояние 1 и на вход элемента И 8 поступает разрешающий сигнал с выхода 1 триггера 2. Первый импульс с выхода генератора 15 импульсов про--ходит через элемент И 8, через элемент И 1 и устанавливает триггер 5 б состоянии 1. Сигналом с выхода 1 триггер 5 открывает элементы И групп 23 и 25, и входная информация с выхода входного регистра t через элементы И группы 23 проходит на информационные входы накопителя, сигнал с выхода О триггера 5 поступает на. вход накопителя 19 (сигнал разрешения записи) и на вход блока 27 управления, в котором сформируется импульс обращения к накопителю, по которому производится запись информации в накопитель по адресу, который с выхода счетчика 21 адресов записи проходит через элементы И 25 и элементы ИШ 16 на адресные входы накопи теля 19. Одновременно импульс обращения пройдет через элемент И 13, эле мент 17 задержки и устанавливает триг геры 3 и 5 в состояние.О. По заднему фронту импульса, сформированного на выходе 1 триггера 5, к показаниям счетчика 21 прибавится 1 и установится адрес по которому должно записываться очередное слово. При подаче сигнала ЧТЕНИЕ триггер устанавливается в 1, на выходе элемента И 11 формируется импульс, который устанавливает триггер 2 в сое тояние О, первый импульс с выхода генератора 15 импульсов проходит че-. рез элементы И 7 и 12 и устанавливает триггер 6 в состояние , при этокГ разрешающий сигнал с 1 выхода триггера 6 поступает на входы элементов И 2Ц и 26. Сигнал с О выхода триггера 6 поступает на вход накопителя (сигнал разрешения ЧТЕНИЯ) и на вход блока 27 управления. Импульсы обращения с выхода блока управления поступают на вход накопителя, в котором происходит чтение информации по адресу, который с выхода счетчика 22 .проходит через элементы И 26 и элементы ИМ 16 на адресные шины накопителя. Счи-г тайная информация проходит через элементы И 24 и записывается в выходной регистр 20; Импульс обращения проходит через элемент И 9, элемент 18 задержки и . L устанавливает триггеры и 6 в О. Если во время чтения пришел сигнал ЗАПИСЬ, то триггер 5 не установится в 1, так как элемент И 1А закрыт сигналом с выхода О триггера 6. Аналогично во время записи сигналом с вы- хода О триггера 5 закрыт элемент И 12. При поочередной подаче сигналов ЗАПИСЬ, ЧТЕНИЕ триггер 2 работает в счетном режиме и имульсы с выхода элементов И 7 и 8 поочередно постугюют на входы элементов И 12 и 14. Введение элементов позволяет повысить быстродействие при асинхронном обращении к накопителю, что особенно важно при обработке в реальном времени, а также при вводе информации с НМЛ в ЭВМ. Формула изобретения Буферное запоминающее устройство, одержащее накопитель, информационные ходы котЪрого подключены к выходам лементов И первой группы, а выходы акопителя подключены к одним входам лементов И второй группы, выходы ко- орых подключены к входам выходного . егистра, одни входы элементов И перой группы подключены к выходам входого регистра, группу элементов ИЛИ ыходы которых подключены к адресным ходам накопителя, одни входы элеменов ИЛИ группы подключены к выходам. лементов И третьей группы, одни вхоы которых подключены к информационым выходам счетчика адресов аписи, другие входы элементов ЛИ группы подключены к выхо- дам элементов И четвертой группы, одни входы которых подключены к информационным выходам счетчика адре сов считывания, блок управления, вы ход которого подключен к первому управляющему входу накопителя, генератор импульсов, отличающеес я тем, что, с целью повышения . быстродействия устройства, оно содержит триггеры, элементы задержки и элементы И, первые входы первого и v второго элементов И подключены к выхо ду генератора импульсов, вторые входы первого и второго элементов И подключены к соответствующим выходам первого триггера, первый вход которого под ключен к выходу генератора импульсов, а второй и третий входы соответственно к выходам третьего и четвертого элементов И первые входы которых подключены к первым выходам соответственно второго и третьего триггеров, первые входы которых являются соответ ствующими управляющими входами устрой ства, вторые входы третьего и четвертого элемента И подключены к вторым выходам соответственно второго и третьего триггеров, первые входы пятого и шестого элементов И подключены к выходу блока управления, первый вход которого подключен к первому выходу четвертого триггера, к первому входу седьмого элемента И и к второму управляющему входу накопителя, второй вход блока управления подключен K первому выходу пятого триггера, к пер вому входу восьмого элемента И и к третьему управляющему накопителя, второй выход четвертого триггера подключен к второму входу шестого элемента И, к другим входам элементов И первой и третьей группы и к счетному входу счетчика адреса записи, второй выход пятого триггера подключен к второму входу пятого элемента И, к другим входам элементов И второй и четвертой групп и к счетному входу счетчика адреса считывания, выход шестого элемента И подключен к входу первого элемента задержки, выход которого подключен к второму входу второго триггера и к первому входу четвертого триггера, выход пятого элемента И подключен к входу второго элемента задержки,выход которого подключен к второму входу третьего триггера и к первому входу пятого триггера, вторые входы седьмого и восьмого элементов И подключены к выходам соответственно первого и второго элементов И, третьи входы седьмого и восьмого элементов И подключены к пер вым выходам соответственно третьего и второго триггеров, а выходы седьмого и восьмого элементов И подключены к вторым входам соответственно пятого и четвертого триггеров. Источники информации, принятые во внимание при экспертизе 1.Патент ФРГ N , . кл..С 11 В 5/02, опублик. 1971. 2.Авторское свидетельство СССР ff 378832, кл. G Об F З/О, 1970. 3. Авторское свидетельство СССР №51515, кл. СПС 9/00, 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное оперативное запоминающее устройство | 1988 |

|

SU1559379A1 |

| Устройство для управления записью информации в блок памяти | 1980 |

|

SU972588A1 |

| Устройство для ввода-вывода информации из накопителей на магнитных дисках | 1982 |

|

SU1019431A1 |

| Устройство управления накопителями на магнитных дисках | 1982 |

|

SU1053143A1 |

| Устройство управления | 1984 |

|

SU1171790A1 |

| Оперативное запоминающее устройство с самоконтролем | 1982 |

|

SU1042081A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Устройство управления загрузкой микропрограмм | 1983 |

|

SU1119019A1 |

| Устройство для сопряжения | 1982 |

|

SU1043619A1 |

Авторы

Даты

1982-05-30—Публикация

1980-10-17—Подача