1

Изобретение относится к запоминающим устройствам.

Известны буферные запоминакгцие устройства 1 и р .

Одно из известных устройств содержит накопительный блок, регистр адреса и блок управления, входной регистр, источник сообщения, вычислительный блок, два счетчика, две схемы И, группу схем ИЛИ, два дешифратора и блок местного управления, состоящий из блоков местного управления записи и считывания .

Недостатком этого устройства является низкое быстродействие.

Наиболее близким по техническому решению к предлагаемому .является 6У фермое запоминающее устройство, содержащее генератор импульсов, входной регистр, матрицу оперативной памяти, блок управления, две группы злементов И, элементы ИЛИ, счетчики адресов записи и считывания, дешифратор адреса и выходной регистр/pfj.

Недостатком данного устройства явгляется то, что в нем скорость записи и считывания в дв.а раза ниже максимально возможной для оперативной памяти, примененной в этом устройстве.

что значительно снижает его быстродействие.

Цель изобретения - повышение быстродействия устройства.:

Поставленная цель достигается тем, что в буферное запоминающее устройство, содержащее накопитель, входной и выходной регистры, четыре группы элементов И, дешифратор, счетчики адресов записи и считывания, и группу элементов ИЛИ, причем входы входного регистра соединены с входными шинами устройства, а выходы - с первыми входами элементов И первой группы, выходы которых подключены к информационным входам накопителя, информационные выходы которого соединены.с первыми входами элементов И второй группы, выходы которых подключены ко.входам выходного регистра, выходы которого соединены о выходными шинами устройства, первые входы элементов ИЛИ третьей и четвертой групп подключены соответственно к выходам счетчика адресов записи и. счетчика адресов считывания, а выходы - соответственно к первым и ко вторым входам элементов ИЛИ группы, выходы которых соединены со входами д«иифратора, выходы кото0 .рого подключены к адресным входам накопителя, введены три триггера, четыре элемента И, элемент ИЛИ, генератор одиночных импульсов, ждущий генератор импульсов и три элемента задержки, причем вход 1енератора одиночных импульсо подключен к выходу элемента ИЛИ, а выходы - к первому входу первого триггера и tiepBOMy управляющему входу накопителя, первые входы первого и второго элементов И соединены с управляющими входами устройства, а выходы - соответственно с первыми входами второго и третьего триггеров, вторые входы котоЕ ах подключены к выходам первого и второго элементов задержки соответственно, первый выход второго триггера соединен со втopыIvlи входами элементов И первой и третьей групп и первым входом третьего элемента И, выход которого подключен ко входу первого элемента задержки, второй выход второго триггера соединен со вторым управляющим входом нaкoпитeля вторим входом второго элемента И, певым, входом элемента ИДИ и входом счетчика адресов записи, первый выхо третьего триггера подключен ко второму входу элемента ИЛИ, входу счетчика адресов считывания, .второму входу первого элемента И и третьему.управляквдему входу накопителя, второй вход первого триггера соединен с вы - ходом синхронизации накопителя и вторыми входами третьего и четвертого элементов И, выход первого триггера подключен ко входу ждущего генератора импульсов, выход которого соединен с третьим входом первого элемента И и входом третьего элемента задержки, выход которого подключен к третьему входу второго элемента И.

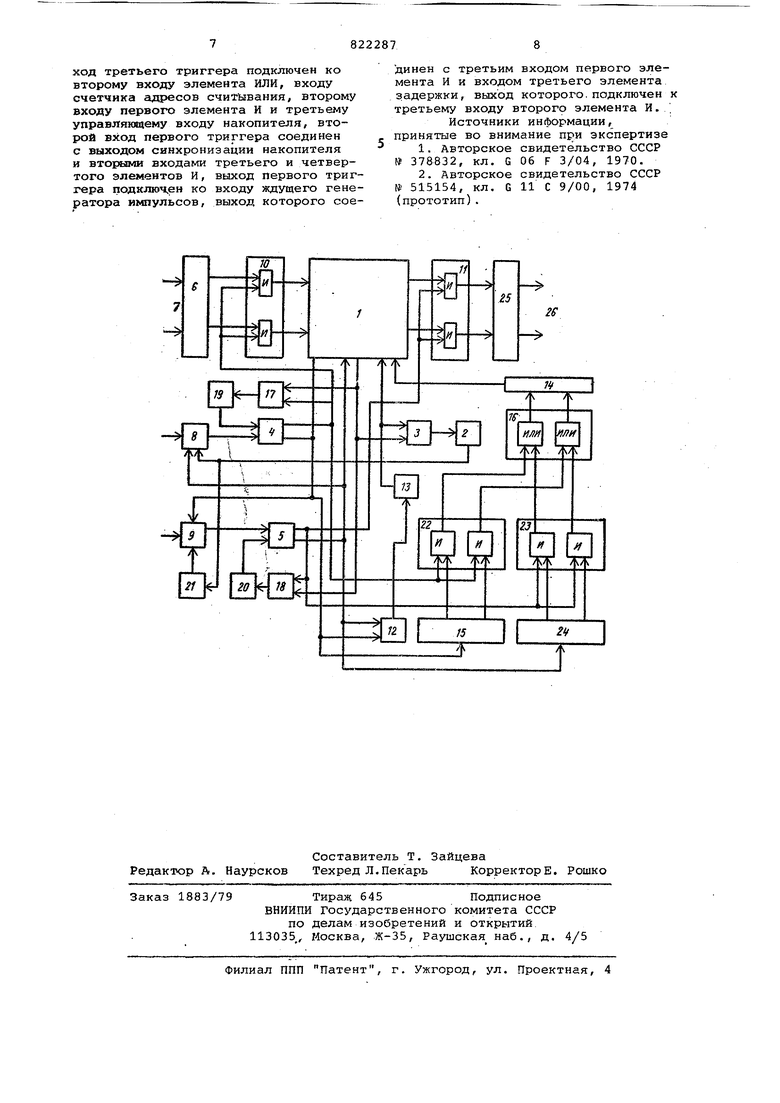

На чертеже приведена функциональная схема предлагаемого устройства.

Устройство содержит накопитель 1, представлягаций собой оперативную память, ждущий генератор 2 импульсов первый 3, второй 4 и третий 5 триггеры, входной регистр 6 с входными шинами 7, первый 8 и второй 9 элементы И, первую 10 и вторую 11 группы элементов И, элемент ИЛИ 12, генератор, 13 одиночных импульсов, дешиЛратор 14, счетчик 15 адресов записи, группу 16 элементов ИЛИ, третий 17 и нетвертЫй 18 элементы И, первый 19, второй 20 и третий 21 элементы задержки, третью 22 и четверт5 10 23 группы элементов И, счетчик 24 адресов считывания, выходной регистр 25, выходные шины 26.

Входы входного регистра 6 соединены с входными шинами 7 устройства, а выходы - с первыми входами элементов И первой группы 10, выходы которых подключены к информационным входам накопителя 1. Информационные выходы накопителя 1 соединены с первыми входами элементов И второй группы 11, выходы которых подключены ко

входам выходного регистра 25, выходы которого соединены с выходными шинами 26 устройства. Первые входы элементов И третьей 22 и четвертой 23 групп подключены соответственно к выходам счетчика 15 адресов записи и счетчика 24 адресов считывания, а выходы - соответственно к первым и ко вторым входам элементов ИЛИ группы 16, выходы которых соединены со входами дешифратора 14. Выходы дешифратора 14 подключены к адресным входам накопителя 1. Вход генератора 13 одиночных импульсов подключен к выхог ду элемента ИЛИ 12, а выход - к первому входу первого триггера 3 и пер:вому управляющему входу накопителя 1. Первые входы первого 8 и второго 9 элементов И соединены с управлякнцими входами устройства, а выходы - соответственно с первыми входами второго 4 и третьего 5 триггеров,-вторые входы КОТОРЫХ подключены к выходам первого 19 и второго 20 элементов задержки соответственно. Первый выход второго триггера 4 соединен со вторыми входами элементов И первой 10 и третьей 22.групп и первым входом третьего элемента И 17, выход которого подключен ко входу первого элемента 19 задержки. Второй выход второго, триггера 4 соединен со вторым управляющим входом накопителя 1, вторым входом второго элемента И 9, первым входом элемента ИЛИ 12. и входом счетчика 15 адресов записи. Первый выход третьего триггера 5 подключен ко вторым входгш элементов И второй 11 и четвертой 23 групп и первому входу четвертого элеменуа И 18, выход которого соединен со входом второго элемента 20 задерж ки. Второй выход третьего триггера 5 подключен ко второму входу элемента ИЛИ 12, входу счетчика 24 адресов считывания, второму входу первого элемента И 8, и третьему управлякяце-. му входу накопителя 1. Второй вход первого триггера 3 соединен с выходом синхронизации накопителя 1 и вторыми входами третьего 17 и четвертого 18 элементов И. Выход первого триггера 3 подключен ко входу ждущего генератора 2 импульсов, выход которого соединен с третьим входом первого элемента И 8 и входом третьего элемента 21 задержки, выход которого подключен к третьему входу второго элемента И 9.

Устройство работает следующим образом

Запись информации в буферное запоминающее устройство и считывание из него выполняются асинхронно по сигналам ЗАПИСЬ и СЧИТЫВАНИЕ, поступающим по управлякмцим входам соответственно на первые входы первого 8 и второго 9 элементов И. При отсутствии сигналов ЗАПИСЬ и СЧИТЬШАНИЕ первый триггер 3 находится в состоянии 1, при этом ждущий генератор 2 импульсов формирует импульсы с частотой следования, превышающей максимальную частоту обращения, обеспечиваемую выбраиньм типом оперативной .памяти, примененной в накопителе 1. Информация, поступающая по входным шинам 7, записывается во входной регистр б. Синхронно с информацией ;поступает сигнал ЗАПИСЬ. Первйй импульс, сформированный ждущим генератором 2 импульсов после поступления сигнала ЗАПИСЬ, проходит через первый элемент И 8 и устанавливает второй триггер 4, в состоянии Сигналом с единичного выхода второго триггера 4 открываются элементы И первой 10 и третьей 22 групп. Одновременно сигнал с нулевого выхода триггера 4 проходит через эле мент ИЛИ 12 иа вход генератора 13 одиночных импульсов, который формиру ет импульс обращения к накопителю 1, по которому осуществляется запись входной информации в накопитель 1. При этом информация записывается по адресу, который формируется в дешифраторе 14 по коду счетчика 15 адресов записи, поступающему на входы дешифратора 14 через третью-группу элементов К 22 к группу элементов ИЛИ 16, На время обращения к накопителю 1, ждущий генератор импульсов 2 прекращает формирование импульсов, т. к на его вход поступает запрещающий потенциал с выхода первого триггера 3 С нулевого выхода второго триггер 4запрещающий потенциал поступает на вход второго элемента И 9, закрывая цепь прохождения через него импульса с выхода ждущего генератора 2 импуль сов, задержанного при помсяци третьей линии задержки 21 и третий триггер 5остается в нулевом состоянии. По окончании записи в накопителе 1 формируется импульс исполнения, который проходит через третий элемент И 17, первую линию задержки 19 и устанавливает второй триггер 4 в О. Одновременно импульсом исполнения первый триггер 3 устанавливается в 1, и ждущий генератор 2 импульсо начинает формировать импульсыi При поступлении сигнала СЧИТЫВАНИЕ на первый вход второго элемента И 9 импульсом с его выхода третий триггер 5 устанавливается в 1, открыпаются элементы И второй 11 и чет вертьй 23 групп, и код с выхода счет чика 24 адресов считывания проходит через четвертую группу элементов И 2 и группу 16 элементов ИЛИ на вход дешифратора 14. Одновременно при по мощи элементов ИЛИ 12 и генератора 1 одиночных импульсов ФОГмируется импульс обращения к накопителю 1, по которому производится считывание ийформации. Считанная информация прохо дит через вторую группу элементов И 1 и записывается в выходной регистр .25 Импульс исполнения проходит через четвертый элемент И 18, третью линию задержки 20 и устанавливает третий триггер 5 в О, подготавливая устройство к выполнению следующей операции . Технико-экономическое преимущество предлагаемого устройства заключает ся в его значительно более высоком, по сравнению с известным быстродействии. . Формула изобретения Буферное запоминающее устройство, содержащее накопитель, входной и выходной регистры, четыре группы элементов И, дешифратор, счетчики адресов записи и считыванияi и группу элементов ИЛИ, причем входы входного регистра соединены с выходными шинами устройства, а выходы - с первыми входами элементов И первой группы, выходы которых подключены к информационным входам накопителя, информационные выходы которого соединены с первыми входами элементов И второй группы, выходы которых подключены ко входам выходного регистра, выходы которого соединены с выходными шинами устройства, первые входы элементов И третьей и четвертой групп подключены соответственно к выходам счетчика; адресов записи и счетчика адресов считывания, а выходы - соответственно к первым и ко BTOjwM входам элементов ИЛИ группы, выходы которых соединены со входами дешифратора, выходы которого подключены к адресным входам накопителя, отличающееся тем, что, с целью повьшения быстродействия устройства, оно содержит три триггера, четыре элемента И, элемент ИЛИ, генератор одиночных импульсов, ждущий генератор импульсов и три элемента задержки, причем вход генератора одиночных импульсов подключен к выходу элемента ИЛИ, а выходы - к первому входу первого триггера и первому управляющему входу накопителя, первые входы первого и второго элементов И соединены с управляющими входами устройства, а выходы - соответственно с первыми входами второго и третьего триггеров, вторые входы которых подключены к -выходам первого и второго элементов задержки соответственно, первый выход второго триггера соединен со вторыми входами элементов И первой и третьей групп и первым входом третьего элемента И, выход которого подключен ко входу первого элемента задержки, второй выход второго триггера соединен со вторым управляющим входом накопителя, вторым входом второго элемента И, первым входом элемента ИЛИ. и входом счетчика .адресов записи, первый выход третьего триггера подключен ко второму входу элемента ИЛИ, входу счетчика адрюсов считывания, второму входу первого элемента И и третьему управляющему входу накопителя, второй вход первого триггера соединен с выходом синхронизации накопителя и вторыми входами третьего и четвертого элементов И, выход первого триггера подключен ко входу ждущего генератора импульсов, выход которого соединен с третьим входом первого элемента И и входом третьего элемента задержки, выход которого.подключен к третьему входу второгр элемента И. .

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 378832, кл. G 06 F 3/04, 1970.

2.Авторское свидетельство СССР № 515154, кл. G 11 С 9/00, 1974 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1980 |

|

SU932566A1 |

| Буферное запоминающее устройство | 1978 |

|

SU942132A1 |

| Измеритель временных интервалов | 1983 |

|

SU1155990A1 |

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1987 |

|

SU1539783A1 |

| Логическое запоминающее устройство | 1981 |

|

SU1014036A1 |

| Оперативное запоминающее устройство с самоконтролем | 1978 |

|

SU771731A1 |

| Запоминающее устройство | 1987 |

|

SU1413674A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Многоканальное устройство тестового контроля логических узлов | 1985 |

|

SU1265778A1 |

| Запоминающее устройство | 1983 |

|

SU1116458A1 |

Авторы

Даты

1981-04-15—Публикация

1979-07-09—Подача