(54) УСТРОЙСТВО КОНТРОЛЯ КОДА «1 ИЗ п

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь правильной двоичной дроби в двоично-десятичную дробь и целых двоично-десятичных чисел в двоичные | 1978 |

|

SU734669A1 |

| Устройство для передачи телеметрической информации | 1980 |

|

SU905845A1 |

| Генератор псевдослучайных чисел | 1980 |

|

SU903872A1 |

| Преобразователь правильной двоично-десятичной дроби в двоичную дробь и целых двоичных чисел в двоично-десятичные | 1978 |

|

SU741260A1 |

| Устройство для определения старшего значащего разряда | 1980 |

|

SU898432A2 |

| Устройство для контроля высокого напряжения на токоведущих элементах трехфазной электроустановки | 1988 |

|

SU1797074A2 |

| Множительное устройство | 1979 |

|

SU817705A1 |

| Устройство для сбора и кодирования информации с годоскопических детекторов и многопроволочных пропорциональных камер | 1990 |

|

SU1835529A1 |

| Устройство для контроля дешифратора | 1982 |

|

SU1024923A1 |

| Устройство для передачи цифровой информации | 1981 |

|

SU980115A1 |

I

Изобретение относится к автоматике и может быть использовано для проверки дешифраторов, распределителей и др.

Известно устройство, содержащее регистр кода операций, дешифратор, триггер четкости, элементы И, ИЛИ 1.

Недостаток устройства - значительные затраты оборудования.

Наиболее близким техническим решением к предлагаемому является устройство, содержаш.ее элементы И, ИЛИ, НЕ, в том числе п/з трехвходовых узлов выделения разрешенных комбинаций, каждая из которых соединена с предыдущей цепью обратной связи, а выходы узлов с выходным элементом ИЛИ, выход цепи обратной связи первого узла выделения через инвертор подключен к выходному элементу ИЛИ, причем в узле выделения разрешенных комбинаций входы первого и второго элемента ИЛИ подключены к входной клемме, второй вход первого элемента ИЛИ и вход третьего элемента ИЛИ ко второй клемме, вход четвертого элемента ИЛИ и второй вход второго элемента ИЛИ к третьей клемме, выходы первого и четвертого элемента ИЛИ соединены параллельно с собирательного элемента ИЛИ

для формирования сигнала обратной связи и со входами выходного элемента И, а выходы второго и третьего элемента ИЛИ соединены с входами второго элемента И, причем вход цепи обратной связи образован соединением свободных входов третьего и четвертого элемента ИЛИ 2.

Недостатки известного устройства - сложность и отсутствие возможности отключения контроля отсутсгвия в коде сигнала «1.

Цель изобретения - упрощение и расширение функциональных возможностей, заключающиеся в контроле отсутствия единичных сигналов.

Поставленная цель достигается тем, что в устройстве, содержащем п-2 элемента ИЛИ

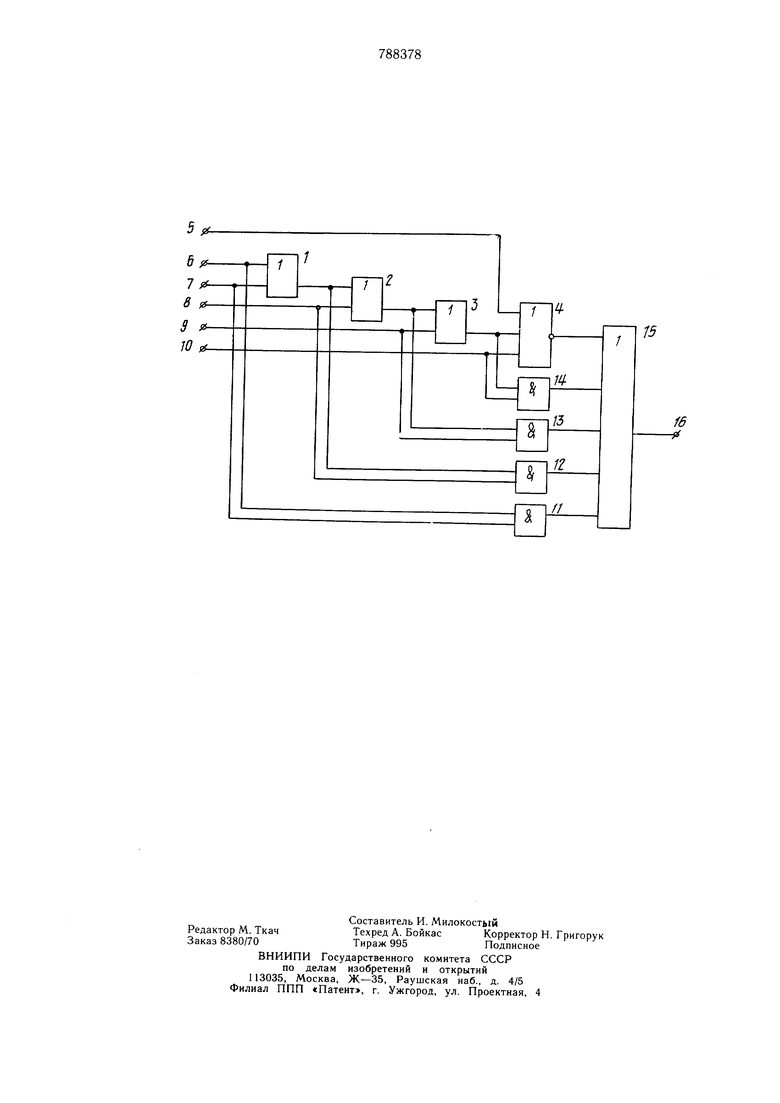

15 п - 1 элементов И, элемент ИЛИ-НЕ, выходной элемент ИЛИ, входы которого соединены с выходами элементов ИЛИ-НЕ и И, а выход является выходом устройства, входы i-oro элемента ИЛИ соединены с выходом i-1 -ого элемента ИЛИ и входом i + 1 -ого разряда кода i 2, п-2; входы первого элемента ИЛИ соединены с входами первого элемента И и с входами первого и второго разрядов кода, а выход п-2-ого с первьш входом элемента ИЛИ-НЕ, второй вход которого подключен к управляющему входу устройства, а третий к входу п-ого разряда кода, входы j-oro элемента И соединены с выходом j - 1-го элемента ИЛИ и входом J-f 1-ого разряда кода j 2, п-1. На чертеже представлена схема предлагаемого устройства контроля кода «1 из п для случая п 5. Схема содержит двухвходовые элементы ИЛИ 1-3, трехвходовой элемент ИЛИ-НЕ 4, вход 5 управления режимом контроля; входы 6-10 контролируемого кода, двухвходовые элементы И 11 -14, многовходовой элемент ИЛИ 15, выход 16 устройства. Предлагаемое устройство контроля кода «1 из п работает следующим образом. Контролируемый код (в данном случае 5 разрядов) параллельно поступает на входы 6-10. Если в этом коде содержится более одной «1, то на входах, по крайней мере, одного из элементов 11 -14 совпадут два сигнала «2, и такой же сигнал появится на выходе элемента И, т.е. на входе элемента 15 и, следовательно, на его выходе 16. При наличии только одного сигнала «1 в контролируемом коде ни на одном из элементов 11 -14 совпадения не будет и на их выходах будут присутствовать сигналы «О. В то же время на одном из входов элемента 4 будет сигнал «1, поэтому на его выходе будет иметь место сигнал «О. Вследствие этого на выходе 16 элемента 4 сигнал «1 будет отсутствовать. В некоторых случаях необходимо контролировать и полное отсутствие сигналов «1 в проверяемом коде. В других случаях, например при контроле стробируемых дещифраторов, такая проверка должна быть исключена. С учетом этих требований в предлагаемом устройстве предусмотрен вход 5 управления режимом контроля. Если на этот вход подан сигнал «1, то на выходе элемента 4 независимо от состава кода присутствует сигнал «О и устройство не обнаруживает отсутствие сигналов «1 в контролируемом коде. При подаче на вход 5 сигнала «О устройство обнаруживает отсутствие сигналов «2 в контролируемом коде, так как в этом случае на входы элемента 4 не поступает ни одного сигнала «1 и с выхода элемента 4 на элемент 15 передается сигнал «2, поступающий затем на выход 16. Включение режима контроля отсутствия «1 в контролируемом коде не меняет работы устройства: при наличии в контролируемом коде только одной «1 и при наличии в нем более одного сигнала «1. Таким образом, использование меньщего числа логических схем и соединений между ними, возможность отключения контроля отсутствия «1 в контролируемом коде обеспечивают упрощение и расщирение функциональных возможностей. Формула изобретения Устройство контроля кода «1 из п, содержащее п-2 элемента ИЛИ, п-1 элементов И, элемент ИЛИ-НЕ, выходной элемент ИЛИ, входы которого соединены с выходами элементов ИЛИ-НЕ и И, а выход является выходом устройства, отличающееся тем, что, с целью упрощения и расщирения функциональных возможностей, заключающихся в контроле отсутствия единичных сигналов, входы i-oro элемента ИЛИ соединены с выходом i-1-ого элемента ИЛИ и входом i +1-ого разряда кода i 2, п-2; входы первого элемента ИЛИ соединены с входами первого элемента И и с входами первого и второго разрядов кода, а выход п-2-ого с первым входом элемента ИЛИ-НЕ, второй вход которого подключен к управляющему входу устройства, а третий к входу п-ого разряда кода, входы j-oro элемента И соединены с выходом j - 1-ого элемента ИЛИ и входом J +1-ого разряда кода , п-1. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 408310, кл. G 06 F 11/00, 1972. 2.Авторское свидетельство СССР № 284040, кл. Н 03 К 13/32, 1968.

6

7ff8

9 s Ю fs15

f6

15

Авторы

Даты

1980-12-15—Публикация

1979-01-29—Подача