I

Изобретение отсносится к автоматике и вычислительной технике и может быть использовано при построении преобразующих устройств.

Известен преобразователь двоичного кода в двоично-десятичный, содержащий блок управления, переключатель эквивалентов, запоминающее устройство, два формирователя двоичных эквивалентов, два регистра сдвига, блок элементов И, щифратор и двоичный вычитатель 1.

Недостатком известного устройства является низкое быстродействие.

Наиболее близким к изобретению по технической сущности и схемному рещению является преобразователь, содержащий двоично-десятичнй сдвигающий регистр, разделенный на п тетрад, где п - число двоично-десятичных разрядов преобразуемого числа, двоичный регистр, элемент И, блок управления коррекцией, блок коррекции, блок управления, одноразрядный суматор, выход которого соединен с входом младщей тетрады сдвигающего регистра, выход которой соединен с первым входом одноразрядного сумматора, выход блока коррекции соединен с первым входом элемента И, второй вход которого соединен с выходом блока управления коррекцией, а выход элемента И соединен со вторым входом одноразрядного сумматора 2.

Кроме того, известное устройство содер5 жит дополнительный регистр, коммутатор кода операции, два-элемента задержки и группу элементов И.

Недостаток этого устройства - относительно низкая скорость преобразования, связанная с тем, что число проводимых коррек10 ций пропорционально числу тетрад преобразуемого числа.

Цель изобретения - увеличение скорости преобразования.

Цель достигается тем, что коррекцию чисел осуществляют одноразрядные сумматоры, включенные в каждую преобразующую тетраду сдвигающего регистра. Предлагаемый преобразователь отличается тем, что дополнительно содержит (п-1) одноразрядных сум20 маторов, (п-1) блоков управления коррекцией, (п-1) элементов И, входной и выходной коммутаторы, первые группы входов которых соединены с группой выходов блока управления, первый и второй выходы блока

управления соответственно соединены со вторыми группами входов входного и выходного коммутаторов, выходы входного коммутатора соединены со входами двоичного регистра, выходы которого соединены с третьей группой входов выходного коммутатора, выход i-oro (1 -чн) одноразрядного сумматора соединен со входом i-ой тетрады сдвигающего регистра, выход которой соединен с первым входом i-oro одноразрядного сумматора, второй вход i-oro одноразрядного сумматора соединен с выходом i-oro элемента И, первый вход которого соединён с выходом (i-1)-ого блока управления коррекцией, вторые входы всех элементов И соединены с выходом блока коррекции, второй выход (i-1)-ой тетрады сдвигающего регистра соединен с первым входом i-oro блока управления коррекцией, вторые входы всех блоков управления коррекцией соединены с третьим выходом блока управления, четвертый выход которого соединен с входом блока коррекции, первый выход первого блока управления коррекцией соединен с выходом выходного коммутатора, выход п-ой тетрады сдвигающего регистра соединен с третьей группой входов входного коммутатора.

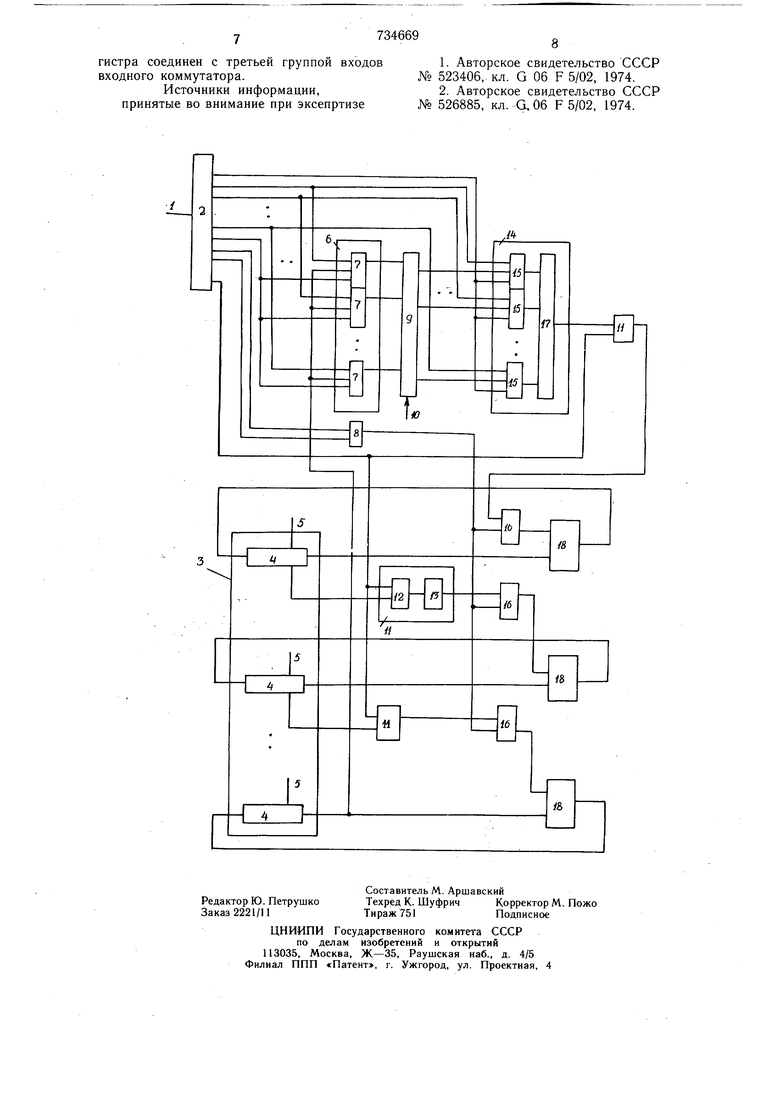

На чертеже представлена функциональная схема предлагаемого устройства.

Устройство включает управляющую щину 1, блок 2 управления, двоично-десятичный сдвигающий регистр 3, разделенный на тетрады 4, щйны 5 десятичной информации, входной коммутатор 6, элементы 7 И, блок 8 коррекции двоичный регистр 9, шины 10 двоичной информации, блоки II управления коррекцией, элемент 2 И, элемент 13 памяти, выходной коммутатор 14, элементы 15 и 16 И, элемент 17 ИЛИ, одноразрядные сумматоры 18.

Управляющая шина 1 предназначена для пуска всего устройства в целом. Блок управления 2 вырабатывает признаки, и сигналы, необходимые для функционирования преобразователя. Двоично-десятичный сдвигающий регистр 3 хранит и сдвигает содержащуюся в нем информацию. Тетрады 4 сдвигающего регистра хранят исходную или промежуточную информацию. На чертеже они расположены в порядке убывания десятичных разрядов сверху вниз. Шины 5 десятичной информации служат для записи информации, подлежащей преобразованию. Входной коммутатор 6 предназначен для записизначения, появляющегося на выходе младшего разряда младшей тетрады в каждом цикле преобразования. Блок 8 коррекции, представляющий собой двухвходовый элемент ИЛИ, вырабатывает код коррекции в каждом цикле преобразования. Двоичный регистр 9 хранит исходную двоичную дробь при прямом преобразовании, либо искомое двоичное число при обратном преобразовании. Шины 10 двоичной информации служат для записи преобразуемой

двоичной дроби в двоичный регистр 9. Блоки 1I управления коррекцией зырабатывают признаки коррекции, если при сдвиге вправо из предшествующих (более старщих) тетрад поступает перенос. Элементы 12 И служат для записи переносов в элементы 13 памяти. Выходной коммутатор 14 передает п-разрядный код двоичного регистра 9 по одному разряду в каждом цикле преобразования. Элементы 16 И передают корректирующий код в зависимости от состояния блоков 11 управления коррекцией. Одноразрядные двоичные сумматоры 18 суммируют содержимое тетрад 4 сдвигающих регистров с корректирующим кодом.

Преобразование как правильной двоичной дроби так и целого двоичного-десятичного числа осуществляется методом сдвига исходного числа (а затем- промежуточных результатов) на один разряд вправо с последующей одновременной коррекцией содержимого всех тетрад сдвигающего регистра, если из младшего разряда двоичного регистра или младшего разряда старшей тетрады поступает в блок управления коррекцией единица, являющаяся признаком коррекции. Кодом коррекции является двоичное число 0101.

При преобразовании правильной двоичной дроби, в двоично-десятичную дробь по сигналу, поступающему с управляющей шины I, запускается блок 2 управления, вырабатывающий потенциал двоичного преобразования и такты,, необходимые для сдвига и коррекции содержимого тетрад 4 двоичнодесятичного регистра 3. Одновременно по шинам 10 двоичной информации записывается в двоичный регистр 9 исходная двоичная дробь. При этом i тетрад 4 и i одноразрядных двоичных сумматоров 18 образуют i последовательных сумматоров для сложения четырехраз;рядных чисел. В первых четырех тактах каждого цикла производится сдвиг содержимого всех тетрад 4 сдвигающего регистра на один разряд вправо и считывается младший разряд двоичного регистра 9. При этом этот разряд и переносы из предшествующих тетрад 4 запоминаются блоками 11 управления коррекцией. В следующих четырех тактах производится одновременное суммирование содержимого всех тетрад 4 сдвигающего регистра с кодом 0101 (если признак коррекции 1) и установка в нулевое состояние всех старших разрядов тетрад 4 в пятом такте. По окончании первого цикла все тетрады 4 сдвигающего регистра хранят промежуточный результат. Двоичный регистр 9 лишь хранит исходную двоичную дробь, а съем его разрядов (по одному в каждом цикле) последовательно осуществляет выходной коммутатор 14, представленный трехвходовыми элементами 15 И и входовым элементом 17 ИЛИ. Вторые входы выходного коммутатора 14 опрашивают последовательно сигналы номера цикла, а на третьи его входы поступает признак ДВО ичного преобразования. Описанный процесс сдвига и коррекции производится п циклов по 8 тактов каждый. После окончания п циклов преобразования искомая двоичная-де сятичная дробь снимается с тетрад 4 сдвигающего регистра 3. При преобразовании целого двоично-десятичного числа метод сдвига и коррекции заключается в том, что исходное двоичнодесятичное число сдвигается в сторону младшах разрядов с запоминанием разрядов пе реноса из младших разрядов каждой предшествующей тетрады в последующую (младшую) тетраду и записью единицы переноса младшей тетрады в двоичный регистр 9. При этом те тетрады, в которых есть перенос, корректируются кодом 0101. Работа в этом режиме производится следующим образом. Сигнал, поступающий по управляющей щине 1, запускает блок 2 управления, вырабатывающий потенциал десятичного преобразования, и необходимое число циклов и тактов в каждом цикле. Одновременно по шиаам 5 десятичная информация записывается в тетрады 4 сдвигающего регистра (двоично-десятичное число). Сдвиг и коррекция содержимого двоично-десятичного сдвигающего регистра 3 осуществляется одновременно . для всех тетрад. При этом коррекции подлежат те тетрады, в схемах управления которых есть единица переноса из предыдущей тетрады. Информационный двоичный разряд, появляющийся на выходе младщей тетрады 4, записывается в младший разряд двоичного регистра 9. Описанный процесс сдвига вправо и коррекции на 0101 производит К циклов, с той лишь разницей, что значение выдвигаемого из младшей тетрады 4 разряда записывается в соответствующий разряд двоичного регистра 9 входным коммутатором 6, состоящим из п элементов 7 И. BTOpbie и третьим входы опрашиваются сигналами номера цикла и потенциалом десятичного преобразования. Для выявления технико-экономических показателей сравним предлагаемое устройство с известным по быстродействию. В обоих устройствах каждый сигнал преобразования обусловлен временем сдвига и коррекции, с той разницей, что время сдвига и коррекции в известном преобразователе прямо пропорционально числу тетрад двоично-десятичного регистра Тп 4-n-k-t + 4-n-k-t 8-n-k-t,. где время преобразования в прототипе; i - число тетрад двоично-десятичного регистра; п - число циклов преобразования; t - длительность тактирующего импульса;4 - число разрядов тетрады. Оценим время преобразования в предлагаемом устройстве T 4-k-t + 4-k-t 8-k-t. Выигрыщ в быстродействии составит в -Ц- п раз Если число разрядов двоично-десятичного регистра равно 10, то скорость преобразования возрастает на порядок. Такое повыщение быстродействия особенно важно, в случаях совмещения операций, когда производится решение одной задачи и готовятся данные для ввода другой задачи, что позволяет в целом повысить производительность специализированной вычислительной мащины. Формула изобретения Преобразователь правильной двоичной дроби в двоично-десятичную дробь и целых двоично-десятичных чисел в двоичные, содержащий двоично-десятичный сдвигающий регистр, размеленный на п тетрад, где п-число двоично-десятичных разрядов преобразуемого числа, двоичный регистр, элемент И, блок управления коррекцией, блок коррекции, блок управления, одноразрядный сумматор, выход которого соединен с входом младшей тетрады сдвигающего регистра, выход которой соединен с первым входом одноразрядного сумматора, выход блока коррекции соединен с первым входом элемента И, второй вход которого соеди-нен с выходом блока управления коррекцией, а выход элемента И соединен со вторым входом одноразрядного сумматора, отличающийся тем, что, с целью увеличения скорости преобразования, он дополнительно содержит (п-1) одноразрядных сумматоров, (п-1)-блоков управления коррекцией, (li-Г) элементов И, входной и выходной коммутаторы, первые группы входов которых соединены с группой выходов блока управления, первый и второй выходы блока управления соответственно соединены со вторыми группами входов входного и выходного коммутаторов, выходы входного коммутатора соединены со входами двоичного регистра, выходы которого соединень с третьей группой в.ходов- выходного коммутатора, выход i-oro (1 2зп) одноразрядного сумматора соединен со входом i-ой тетрады сдвигающего регистра, выход которой соединен с первым входом i-oro одноразрядного сумматора, второй вход i-oro одноразрядного сумматора соединен с выходом i-oro элемента И, первый вход которого соединен с выходом (i-1)-ого блока управления коррекцией, вторые входы всех элементов И соединены с выходом блока коррекции, второй выход (1-1)-ой тетрады сдвигающего регистра соединен с первым входом 1-ого блока управления коррекцией, вторые входы всех блоков управления коррекцией соединены с третьим выходом блока управления, четвертый выход которого соединен с входом блока коррекции, первый выход первого блока управления коррекцией соединен с выходом выходного коммутатора, выход п-ой тетрады сдвигающего ре

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь правильной двоично-десятичной дроби в двоичную дробь и целых двоичных чисел в двоично-десятичные | 1978 |

|

SU741260A1 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1978 |

|

SU752323A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1977 |

|

SU699520A1 |

| Преобразователь двоичной дроби в двоично-десятичную дробь | 1978 |

|

SU723568A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОЙ ДРОБИ В ДВОИЧНУЮ ДРОБЬ | 1979 |

|

SU826335A1 |

| Преобразователь правильной двоичной дроби в двоично-десятичную дробь и целых двоично-десятичных чисел в двоичные | 1974 |

|

SU526885A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1978 |

|

SU723567A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1962 |

|

SU717754A1 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1979 |

|

SU860053A1 |

| Преобразователь дробных двоичныхчиСЕл B дЕСяТичНыЕ | 1979 |

|

SU798798A1 |

Авторы

Даты

1980-05-15—Публикация

1978-01-27—Подача