(54) МНОЖИТЕЛЬНОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричное устройство для вычисления тригонометрических функций | 1984 |

|

SU1226448A1 |

| Параллельный сумматор | 1981 |

|

SU1018114A1 |

| Устройство для умножения | 1989 |

|

SU1688238A1 |

| Матричное вычислительное устройство | 1982 |

|

SU1034032A1 |

| Устройство для умножения | 1989 |

|

SU1714592A1 |

| Вычислительное устройство | 1983 |

|

SU1117635A1 |

| Устройство для умножения | 1981 |

|

SU1032453A1 |

| Устройство для умножения | 1978 |

|

SU888109A1 |

| Устройство для контроля умножения по модулю три | 1986 |

|

SU1361556A1 |

| Матричное множительное устройство | 1984 |

|

SU1170450A1 |

I

Изобретение относится к вычислительной технике и может быть использовано в качестве блока умножения в цифровых вычислительных машинах,а также в цифровых системах контроля и управления.

Известно множительное устройство, содержащее многоранговые пирамидально-соединенные сумматоры, п-разрядные регистры множимого, множителя и произведения, разбитые на n/g групп разрядов (где g - число разрядов в группе), дешифраторы, (n/g ) множительных устройств по n/g в каждой группе.

Выходы разрядов каждой группы регистров множимого и множителя подключены ко входам соответствующего дешифратора, первые входы всех множительных устройств каждой группы,начиная с младшей, подключены к выходам дешифратора своей группы,/ вторые входы каждого множительного устройства каждой группы соединены с выходами соответствующей g-разрядной группы регистра множимого, выходы всех множительных устройств каждой группы подключены ко входам соответствую- щих сумматоров первого ранга, а выходы сумматора последнего ранга - ко входам регистра произведения 1J.. Однако пирамидальная структура построения приводит к значительному усложнению устройства. Кроме того, в устройстве использованы неоднородные элементы, что усложняет его эксплуатацию, выполнение умножения происходит в прямом коде, т.е. уст0ройство применимо для умножения толь.ко положительных чисел.

Известно также множительное устройство, в котором умножение выполняется в дополнительном коде, т.е. 5 применимое для умножения как положи.тельных, так и отрицательных чисел, построено по типу матрицы из рядов цо т полных сумматоров в ряду и т-1 элементов И, выходы которых соедине0ны с входами соответствующих сумматоров. Кроме того, устройство содержит вход1 ую и выходную корректирующие схемы. Выходы входной корректирующей схемы, предназначенной для спе- .

5 циального преобразования входных сигналов в новые двоичные переменные, соединены с соответствующими входами элементов И, а выходы сумматоров п-ого ряда - с входами выходной корректирующей схемы, которая преобра0

ует произведение сомножителей в доолнительный код.

Т-акое устройство в отличие от, опианного ранее построено на однородных элементах pj ,

Недостаток устройства - усложнение конструкции его за счет наличия входйой и выходной корректирующих схем, содержащих набор ячеек. И, ИЛИ, Исключающее ИЛИ.

Наиболее близким к предлагаемому является множительное устройство матричного типа, состоящее из п рядов по m ячеек, каждая из которых содержит узел формирования переноса, сумматор по модулю два и элемент И, при этом первый вход узла формирования переноса каждой k-ой ячейки J-го ряда (j 1,..,;п; k т l,...rm) соединен с первыми входом сумматора по модулю два той же ячейки и выходом сумматора по модулю два (k-l)-oй ячейки (j-l)-ro разряда, второй вход узла формирования переноса каждой k-ой ячейки j-го ряда со вторым входом сумматора по модулю два той же ячейки и с выходом узла формирования переноса ()-oй ячейки j-ro ряда, третий вход узла формирования переноса каждой k-ой ячейки j-Г, порядка - с первым входом элемента И тон же ячейки и с третьими входами узлов формирования переноса всех ячеек j-ro ряда, третий вход.сумматора по модулю два каждой k-ой ячейки, j-ro ряда - с выходом элемента И той же ячейки. Кроме того, каждая k-ая ячейка j-ro ряда известного устройства содержит дополнительный сумматор по модулю два, выход которого соединен со вто-. рым входом элемента И и четвертым входом узла формирования переноса той же ячейки. Первый вход дополнительного сумматора по модулю два каж-дои k-ой ячейки j-ro ряда соединен первыми входами дополнительных сумматоров всех ячеек каждого j-ro ряда, а второй пход дополнительного сумматора по модулю два каждой ячейки первого ряда - со вторыми входами дополнительных сумматоров по модулю два соответствующих последующих рядов до п-го ряда.

Такое устройство построено на однородных ячейках.

Однако каждая из ячеек данного устройства содержит большое количество составляющих ячейку элементов, что усложняет устройство в целом.

Цель изобретения - упрогцение устройства.

Поставленная цель достигается тем, что в множительном устройстве,состоящем из п рядов по m ячеек, каждая из которых содержит узел формирования переноса, сумматор по молупю два и элемент И, при этом первый вход узла формирования каждо

k-ой ячейки j-ro ряда соединен с первым входом сумматора по модулю два и той же ячейки и с выходом сумматора по модулю два (k-l)oй ячейки (j-l)-ro ряда, второй вход узла формирования переноса каждой k-ой ячейки j-ro ряда - со вторым входом сумматора по модулю два и той же ячейки и с выходом узла формирования переноса (k+1)-oй ячейки j-ro ряда,третий вход узла формирования переноса каждой k-ой ячейки j-ro ряда - с первым входом элемента И той же ячейки и с третьими входами узлов формирования переноса всех ячеек j-ro ряда, третий вход сумматора по модулю два каждой k-ой ячейки j-ro ряда соединен с выходом элемента И той же ячейки, в каждую k-ую ячейку п-ого ряда введен элемент НЕ, выход которого соединен со втopы 4 входом элемента И той же ячейки, второй вход элемента И каждой k-ой ячейки первого ряда устройства соединен непосредственно со вторыми входами элементов И k-ых ячеек последующих рядов, кроме п-ого ряда и с выходом элемента НЕ k-ой ячейки п-ого ряда, а выход .элемента -И каждой ячейки j-ro ряда - с четвертым входом узла формирования переноса той же ячейки.

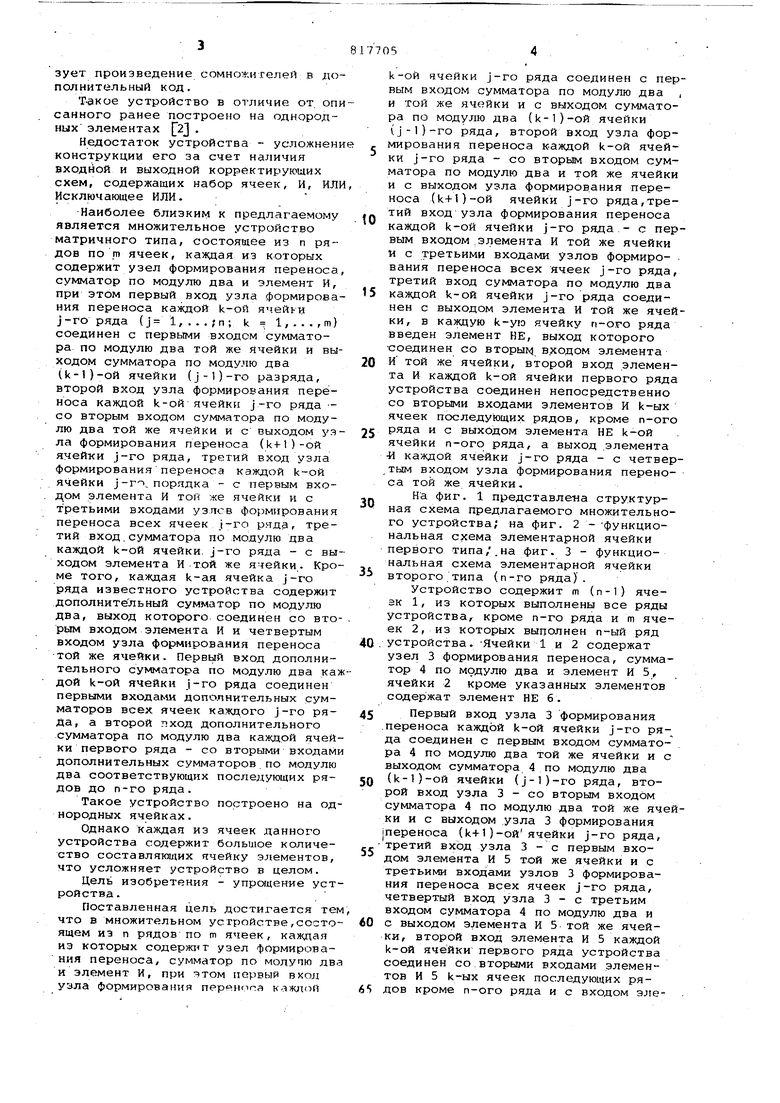

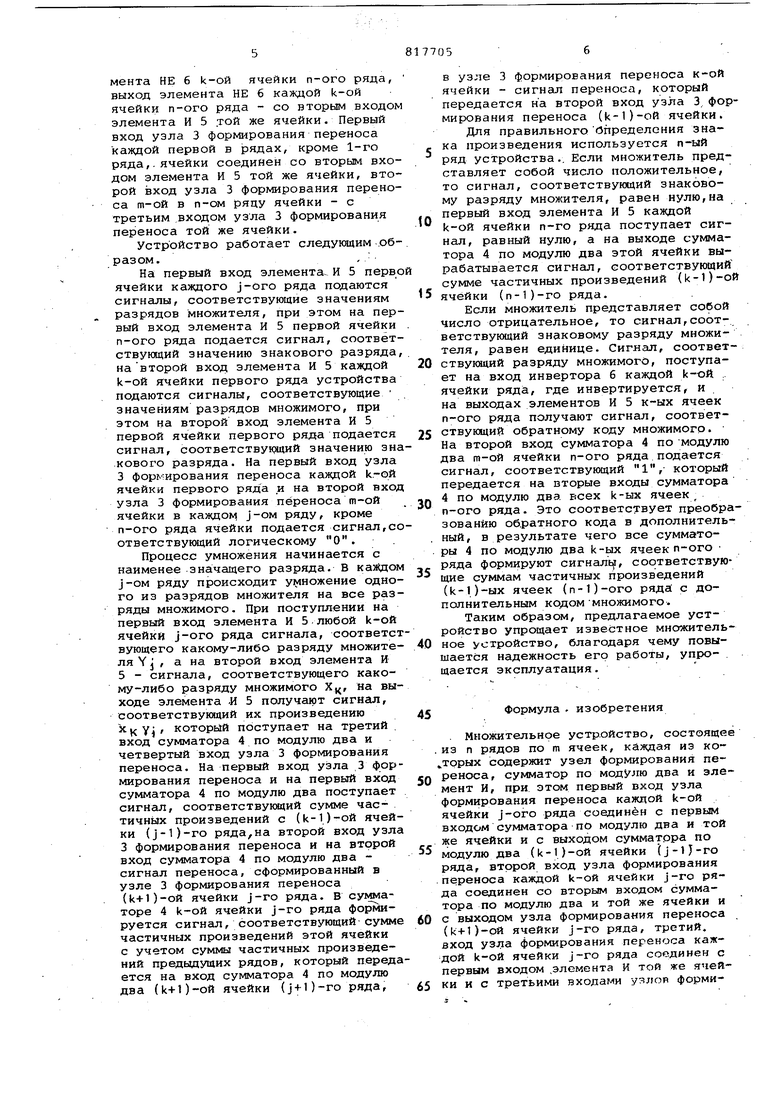

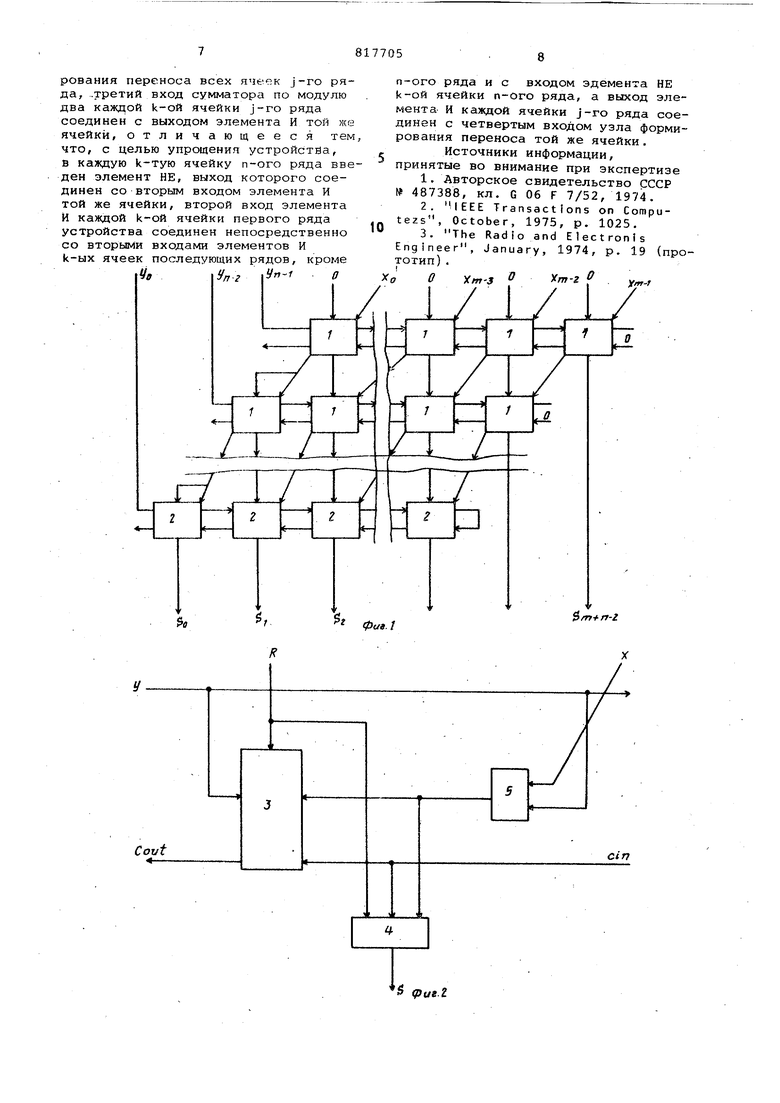

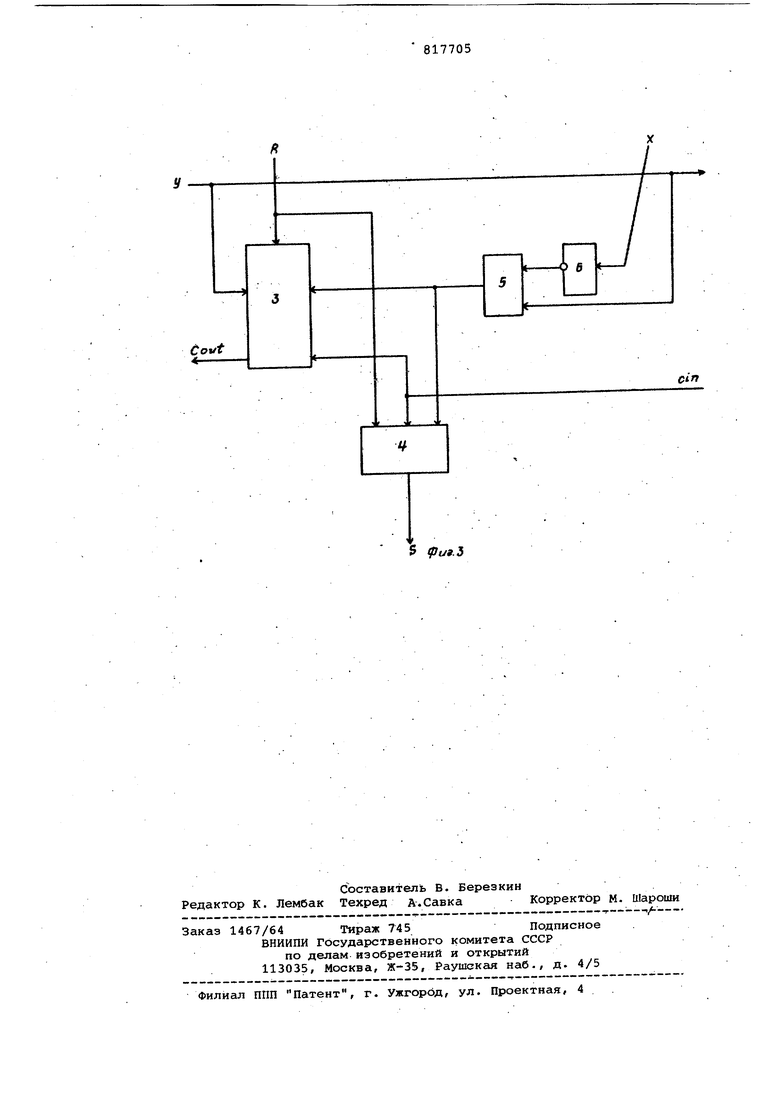

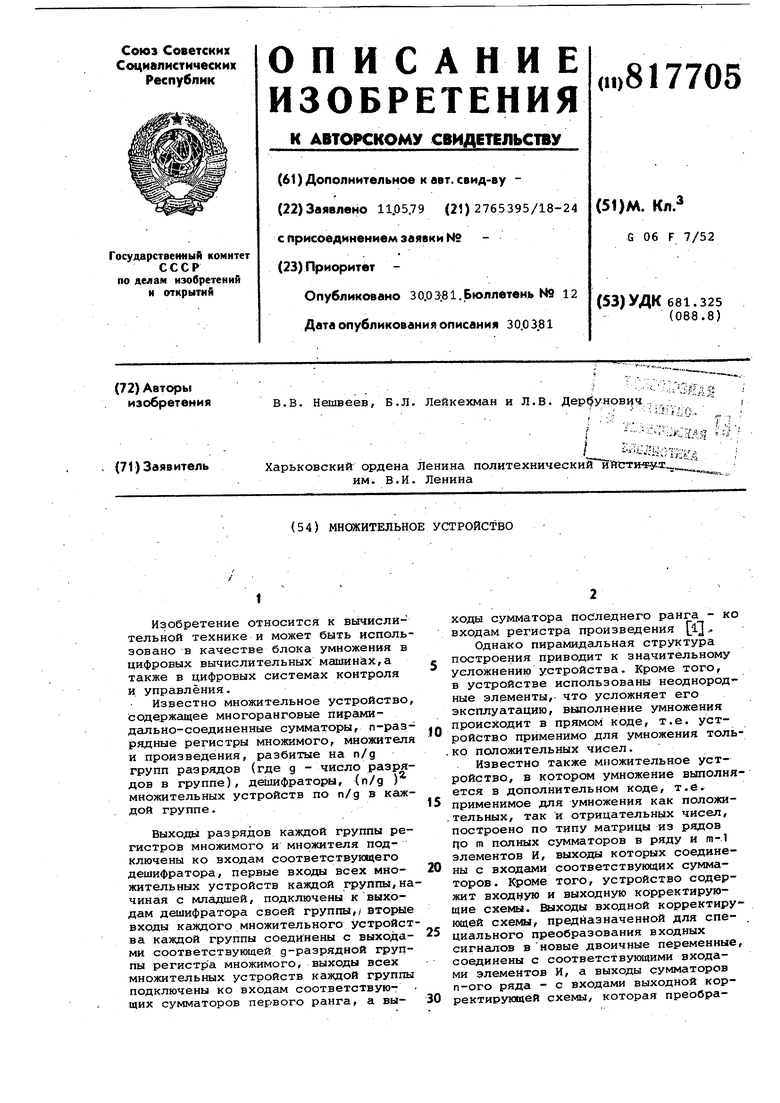

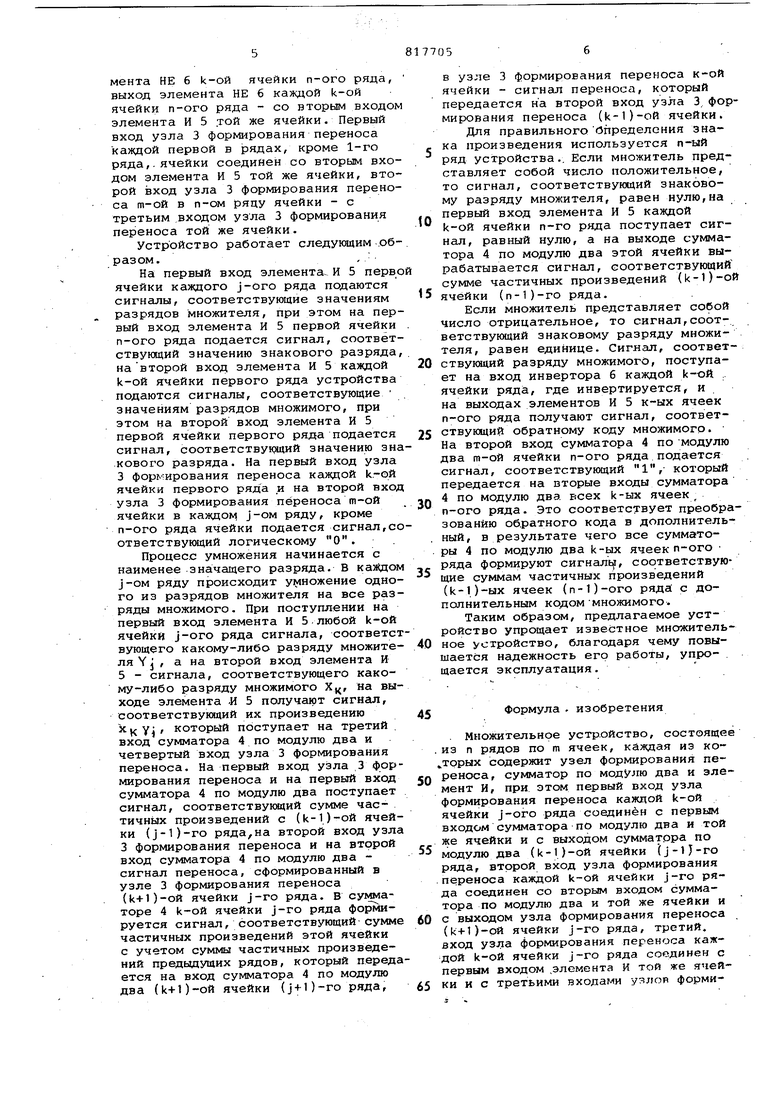

На фиг. 1 представлена структурная схема предлагаемого множительного устройства; на фиг. 2 -функциональная схема элементарной ячейки первого типа,.на фиг. 3 - функциональная схема элементарной ячейки второго типа (п-го ряда).

Устройство содержит m (п-1) ячезк 1, из которых выполнены все ряды устройства, кроме п-го ряда и m ячеек 2, из которых выполнен п-ый ряд .устройства. -Ячейки 1 и 2 содержат узел 3 формирования переноса, сумматор 4 по модулю два и элемент И 5, ячейки 2 кроме указанных элементов содержат элемент НЕ 6.

Первый вход узла 3 формирования .переноса каждой k-ой ячейки j-ro ряда соединен с первым входом сумматора 4 по модулю два той же ячейки и с выходом сумматора 4 по модулю два (k-1)-oй ячейки (j-l)-ro ряда, второй вход узла 3 - со вторым входом сумматора 4 по модулю два той же ячеки и с выходом узла 3 формирования шереноса (k+1)-ойячейки j-ro ряда, третий вход узла 3 - с первым входом элемента И 5 той же ячейки и с третьими входами узлов 3 формирования переноса всех ячеек j-ro ряда, четвертый вход узла 3-е третьим входом сумматора 4 по модулю два и с выходом элемента И 5 той же ячейки, второй вход элемента И 5 каждой k-ой ячейки первого ряда устройства соединен со вторыми входами элементов И 5 k-ых ячеек последующих рядов кроме п-ого ряда и с входом элемента НЕ 6 k-ой ячейки п-ого ряда, выход элемента НЕ 6 каждой k-ой ячейки п-ого ряда - со вторым входо элемента И 5 той же ячейки. Первый вход узла 3 формирования переноса каждой первой в рядах, кроме 1-го ряда,, ячейки соединен со вторым вхо дом элемента И 5 той же ячейки, вто рой вход узла 3 формирования перено са т-ой в п-ом ряду ячейки - с третьим входом узла 3 формирования переноса той же ячейки. Устройство работает следующим .об разом., На первый вход элемента. И 5 перв ячейки каждого j-oro ряда подаются сигналы, соответствующие значениям разрядов множителя, при этом на пер вый вход элемента И 5 первой ячейки п-ого ряда подается сигнал, соответ ствующий значению знакового разряда навторой вход элемента И 5 каждой k-ой ячейки первого ряда устройства подаются сигналы, соответствующие значениям разрядов множимого, при этом на второй вход элемента И 5 первой ячейки первого ряда подается сигнал, соответствующий значению зн ковохо разряда. На первый вход узла 3 формирования переноса каждой k.-ой ячейки первого ряда и на второй вход узла 3 формирования переноса т-ой ячейки в каждом j-ом ряду, кроме п-ого ряда ячейки подается сигнал,с ответствующий логическому О. Процес.с умножения начинается с наименее значащего разряда. В J-OM ряду происходит умножение одного из разрядов множителя на все разряды множимого. При поступлении на первый вход элемента И 5 любой k-ой ячейки j-oro ряда сигнала, соответст вующего какому-либо разряду множителя Y j , а на второй вход элемента И 5 - сигнала, соответствующего какому-либо разряду множимого Х, на выходе элемента -И 5 получают сигнаш, соответствующий их произведению Хцу, который поступает на третий вход сумматора 4 по модулю два и четвертый вход узла 3 формирования переноса. На первый вход узла 3 формирования переноса и на первый вход сумматора 4 по модулю два поступает сигнал, соответствующий сумме частичных произведений с (k-1)-oй ячейки {j-1)-ro ряда,на второй вход узла 3 формирования переноса и на второй вход сумматора 4 по модулю два сигнал переноса, сформированный в узле 3 формирования переноса {k+1)-oй ячейки j-ro ряда. В сумматоре 4 k-ой ячейки j-ro ряда формируется сигнал, соответствующий- сумме частичных произведений этой ячейки с учетом суммы частичных произведений предыдущих рядов, который переда ется на вход сумматора 4 по модулю два (k+1)-oй ячейки (j+l)-го ряда, в узле 3 формирования переноса к-ой ячейки - сигнал переноса, который передается на второй вход узла 3 формирования переноса (k-1)-oй ячейки. Для правильного Определения знака произведения используется п-ый ряд устройства.. Если множитель представляет собой число положительное, то сигнал, соответствующий знаковому разряду множителя, равен нулю,на первый вход элемента И 5 каждой k-ой ячейки п-го ряда поступает сигнал, равный нулю, а на выходе сумматора 4 по модулю два этой ячейки вырабатывается сигнал, соответствующий сумме частичных произведений (k-1)-oй ячейки (n-l)-ro ряда. Если множитель представляет собой число отрицательное, то сигнал,соответствующий знаковому разряду множителя, равен единице. Сигнал, соответствукщий разряду множимого, поступает на вход инвертора 6 каждой k-оЯ . ячейки ряда, где инвертируется, и на выходах элементов И 5 к-ых ячеек п-ого ряда получают сигнал, соответствующий обратному коду множимого. На второй вход сумматора 4 по модулю два т-ой ячейки п-ого ряда подается сигнал, соответствующий 1,- который передается на вторые входы сумматора 4 по модулю два всех k-ых ячеек п-ого ряда. Это соответствует преобразованию об.ратного кода в дополнительный, в результате чего все сумматоры 4 по модулю два k-ых ячеек п-ого ряда формируют сигналь, соответствующие суммам частичных произведений (k-1)-ыx ячеек (n-l)-oro ряда с дополнительным кодомМНОЖИМОГО. Таким образом, предлагаемое устройство упрощает известное множительное устройство, благодаря чему повышается надежность его работы, упро- . щается эксплуатация. Формула . изобретения . Множительное устройство, состоящее из п рядов по m ячеек, каждая из котррых содержит узел формирования переноса, сумматор по модулю два и элемент И, при этом первый вход узла формирования переноса каждой k-ой ячейки j-oro ряда соединён с первым входом сумматора по модулю два и той же ячейки и с выходом сумматора по одулю два (k-l)-oй ячейки (j-1j-ro яда, второй вход узла формирования ереноса каждой k-ой ячейки j-ro ряа соединен со вторым входом суммаcipa по модулю два и той же ячейки и выходом узла формирования переноса ()-pй ячейки j-ro ряда, третий. ход узла формирования переноса кажой k-ой ячейки j-ro ряда соединен с ервым входом .элемента И той же ячейи и с третьими входами узлоп формирования переноса всех ячеек j-ro ряда, .третий вход сумматора по модулю два каждой k-ой ячейки j-ro ряда соединен с выходом элемента И той же ячейки, отличающееся тем что, с целью упрощения устройства, в каждую k-тую ячейку п-ого ряда вве ден элемент НЕ, выход которого соединен со вторым входом элемента И той же ячейки, второй вход элемента И каждой k-ой ячейки первого ряда устройства соединен непосредственно со вторыми входами элементов И k-ых ячеек последующих рядов, кроме п-ого ряда и с входом эдемента НЕ k-ой ячейки п-ого ряда, а выход элемента И каждой ячейки j-ro ряда соединен с четвертым входом узла формирования переноса той же ячейки, Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 487388, кл. G 06 F 7/52, 1974. 2. ilEEE Transactions on Computezs, October, 1975, p. 1025. 3. Radio and Electronls Engineer, January, 1974, p. 19 (прототип) . 0Y«,.. 0У„,.2 0 0 )(m-3 , 1 т-т-г

л

Cout

cin

(putl

-

S ipu.5

Авторы

Даты

1981-03-30—Публикация

1979-05-11—Подача