Изобретение относитсА к автоматике, телемеханике и вычислительной технике и может быть использовано для непрерывного контроля различных дешифраторов в процессе их основной работы.

Известно устройство для контроля работы дешифратора, содержащее входной регистр, дешифратор, многовходовые схемы ИСКЛОЧАЩЕЕ ИЛИ и схему сравнения р .

Недостаток этого устройства для контроля работы дешифратора вход ная кодовая комбинация должна содержать контрольные разряды,что сужает область применения таких схем контроля.

Известно также устройство для контроля дешифратора, содержащее блок аналогового суммирования, пороговые элементы, элемент ИЛИ 2j .

Однако это устройство не контролирует соответствие выходного сигнал входной кодовой комбинации и поэтому не фиксирует отказы дешифратора в случае,когда на его выходе возбуждается нетребуемая шина или когда при налимий на входе запрещенной кодовой комбинации на одном из выходов дешифратора появляется сигнал.

Наиболее близким техническим решением к изобретению является устройство для контроля дешифратора, со держащее контролируемый дешифратор, многовходовые элементы ИЛИ, схемы нечетности и элементы НЕ, ИЛИ и

.

Недостатком известного устройства является то, что при контроле неполных дешифраторов, оно не выявляет отказы, когда при наличии на входе дешифратора запрещенной кодовой комбинации на его выходе возбуждается нетребуемая шина в группе выходов, соответствующей входной кодовой комбинации.

Цель изобретения - расширение функциональных возможностей устройства за счет обнаружения ошибок в группе выходов, соответствующей входной кодовой комбинации.

Поставленная цель достигается тем что в устройство для контроля дешиф5 ратора, содержащее первый, второй,и третий элементы ИЛИ, первый элемент НЕ, первый и второй элементы И, причем четные и нечетные выходы контролируемого дешифратора соединены с входами первого и в°горого элементов ИЛИ соответственно, выходы которых соединены с первыми входами первого и Btoporo элементов И соот,ветственно, вход младшего разряда дешифрируемого кода дешифратора соединен с вторым входом первого элемента И и через первый элемент НЕ с вторым входом второго элемента И, выходы первого и второго элементов И соединены соответственно с первым и вторым входами третьего элемента И выход которого является контрольным выходом устройства введены четвертый и пятый элементы ИЛИ, второй элемент НЕ, элемент ИЛИ-НЕ, третий, четвертый и пятый элементы И, причем треть группа выходов контролируемого дешифратора соединена с входами четвертого элемента ИЛИ, выход которого соединен с первыми входами третьего и четвертого элементов И и через второй элемент НЕ с первым входом пятого элемента И, выход первого элемента ИЛИ .соединен с первым входом элемента ИЛИ-НЕ и вторым входом четвертого элемента И, выход которого соединен с третьим входом третьего элемента ИЛИ, выход второго элемента ИЛИ, соединен с вторыми входами элемента ИЛИ-НЕ И третьего элемента И, выход которого соединен с четвертым входом третьего элемента ИЛИ, входы контролируемого дешифратора соединены с входами пятого элемента ИЛИ, выход которого соединен с вторым входом пятого элемента И, выход элемента ИЛИ-НЕ соединен с третьим входом пятого элемента И, выход которого соединен с входом третьего элемента ИЛИ.

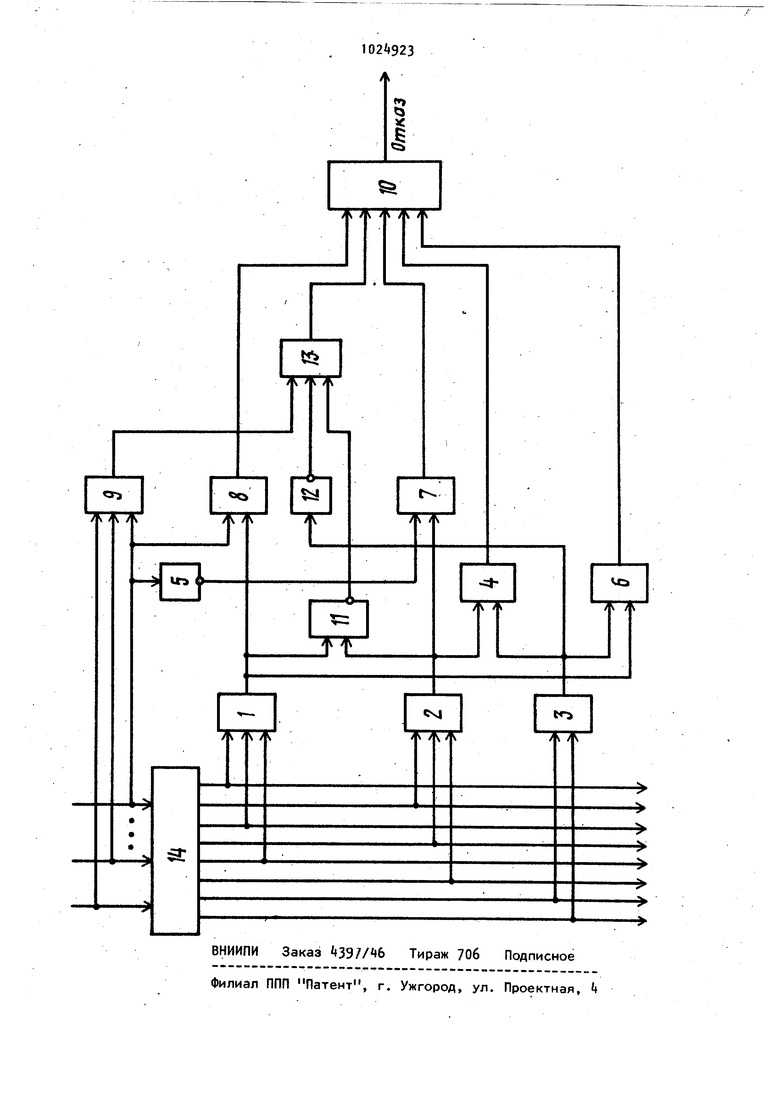

На чертеже приведена функциональная схема предлагаемого устройства.

Устройство для контроля дешифратора содержит элементы ИЛИ 1-3, элемент И k, элемент НЕ 5, элементы И, 6-8, элементы ИЛИ 9 и 10, элемент ИЛИ-НЕ 11, элемент НЕ 12, трехвходовый элемент И 13 и контролируемый дешифратор 14.

Первая группа выходов контролируемого дешифратора 14 соединена с входами элемента ИЛИ 1, вторая с входами элемента ИЛИ 2, а третья группа с входами элемента ИЛИ 3t

Входы контролируемого дешифратора 14 соединены с входами элемента ИЛИ 9. Вход младшего разряда контролируемого дешифратора 14 соединен с входами элемента И 8 и элемента НЕ 5

Выход элемента НЕ 5 соединен с входом элемента И 7. Выход элемента ИЛИ 1 соединен с входами элемента И 8, элемента ИЛИ-НЕ 11 и элемента И 6. Выход элемента ИЛИ 2 соединен с входами элемента ИЛИ-НЕ 11 и элементов И и 7. Выход элемента ИЛИ 3 соединен с входами элементов И и 6 и элемента НЕ 12. Выход элемента ИЛИ 9 соединен с входом трехвходового элемента И 13, его второй вход соединен с выходом элемента НЕ 12, а третий вход - с выходом элемента ИЛИ-НЕ 11 .Выходы элементов И t и 6-8 L и трехвходового элемента И 13 соединены с входами элемента ИЛИ 10. Выход элемента ИЛИ 10 является выходом устройства.

Устройство для контроля дешифраторов выявляет отказы в контролируемом дешифраторе 1, когда выходная возбужденная шина не соответствует входной кодовой комбинации, KOI- да вместе с требуемой выходной шиной возбуждается нетребуемая выходная шина и кЬгда отсутствует возбужденная выходная шина при наличии на входе кодовой комбинации из числа разрешенных.

Кроме того, устройство может контролировать широко распространенный на практике класс неполных дешифраторов. При контроле таких дешифраторов предлагаемое устройство обнаруживает такие отказы, когда возбуждается нетребуемая ёыходная шина при наличии на входе запрещенной кодовой комбинации.

При этом осуществляется контроль двух типов отказов в работе контролируемого дешифратора. При контроле отказов первого типа устройство фиксирует отказы, когда при наличии на входе запрещенной кодовой комбинации на выходе дешифратора возбуждается нетребуемая шина в группе выходов, не соответствующей входной кодовой комбинации. При контроле отказов второго типа устройство обнаруживает кратные ошибки в одной группе выходов контролируемого дешифратора, соответствующей входной кодовой комбинации.

Контроль соответствия выходной возбужденной шины входной кодовой комбинации осуществляется следующим образом.

Выходы контролируемого дешифратора 14 разбиты на группы таким образом, что в первой группе объединены возбуждаемые выходы при поступлении входной кодовой комбинации с нулем в младшем разряде (000,010, 100 и т.д., а во второй группе объдинены возбуждаемые выходы при поступлении входной кодовой комбинации с единицей в младшем разряде (СОТ, 011,101 ит.д.).В третью группу выходов

0 объединены те выходы дешифратора 14 которые соответствуют запрещенным входным комбинациям.

Пусть, например, на вход неполного .контролируемого дешифратора 1

5 поступает кодовая комбинация 100.

При правильной работе дешифратора сигнал, появившейся на его выходе поступает на вход элемента ИЛИ 1, С выхода элемента ИЛИ 1 на выход элемента И 8 этот сигнал не проходит,

0 так как элемент И 8 закрыт нулевым сигналом в младшем разряде входной кодовой комбинации. Элемент И 7 закрыт нулевым сигналом с выхода элемента ИЛИ 2, поэтому сигнал Сбой

5 на выходе элемента ИЛИ 10 отсутст вует.

Если из-за отказа в работе контролируемого дешифратора 1, сигнал появляется во второй группе выходов,

0 он поступает на вход элемента ИЛИ 2. Сигнал с выхода элемента ИЛИ 2 проходит на выход элемента И 7, так как нулевой сигнал в младшем разряде входной кодовой комбинации через ин5вертор 5 открывает элемент И 7. С выхода элемента И 7 сигнал поступает на вход элемента ИЛИ 10, на выходе которого появляется сигнал Сбой.

Если на вход контролируемого де0шифратора 1 поступает, например, кодовая комбинация 001, возбудиться должна выходная шина во второй группе выходов. Тогда при правильной работе дешифратора И элемент И 7 зак5рыт нулевым сигналом с выхода инвертора 5 так как в младшем разряде входного кодовой комбинации присутствует единица, а элемент И 8 закрыт нулевым сигналом с выхода эле0мента ИЛИ 1.

Если из-за отказа в дешифраторе 14 сигнал появляется в первой группе выходов, этот сигнал через элемент ИЛИ 1 проходит на выход эле5мента И 8, открытый по другому входу единичным сигналом в младшем разряде входной кодовой комбинации. С выхода элемента И 8 сигнал поступает на вход Элемента ИЛИ 10, на вы ходе которого появляется сигнал Сбой. Следовательно, контролем попадания возбужденной выходной шины в группу выходов, соответствующих нулевому или единичному состоянию мла шего разряда входной кодовой комбин ции, осуществляется контроль соотвеУствия выходного сигнала входной кодовой комбинации. Если из-за отказа дешифратора 1 сигналы с возбужденных шин на его выходах одновременно поступают на входы элементов ИЛИ 1 и 2 (случай возбуждения требуемой и нетребуемой .выходных шин дешифратора), единичны сигналы с выходов элементов ИЛИ 1 и 2 поступают на входы соответствующи элементов И 8 и 7- В зависимости от него, нулевой или единичный сигнал присутствует в младшем разряде вход ной кодовой комбинации, сигнал с вы хода элементов ИЛИ 1 и 2 проходит со ответственно через элемент И 8 или 7 на вход элемента ИЛИ 10, в резуль тате чего на его выходе появляется сигнал Сбой, I В случае, когда отказ контролируемого дешифратора Т приводит .к отсутствию возбужденной шины на выходе при наличии на в)o(e разрешенной кодовой комбинации, на выходах элементов ИЛИ 1 и 2 присутствуют ну левыб сигналы. Следовательно, на выходе элемента ИЛИ-НЕ 11 присутствует единичный сигнал, который поступает на вход элемента И 13, так как на входе контролируемого дешифратора присутствует кодовая комбина ция , отличная от нулевой, на выходе элемента ИЛИ 9 присутствует единичный сигнал, который поступает на дру гой вход элемента И 13. В случае контроля неполного дешифратора выходы запрещенных комбинаций выделяются в третью группу выходов дешифратора. Поэтому, если на входе контролируемого дешифратора присутствует кодовая комбинация из числа запрещенных, на выходе эле мента ИЛИ 3 присутствует единичный сигнал, который инвертируется элементом НЕ 12. В результате, на выходе элемента НЕ 12 появляется нулевой сигнал, который, поступая на третий вход элемента И 13, запрещает прохождение единичных сигналов с |других входов на его выход. Следовательно, сигнал Сбой на выходе устройства не появляется. В случае, когда на входе контролируемого дешифратора I присутст- . вует кодовая комбинация из числа раз- . решенных, а из-за отказа на его выходах отсутствует возбужденная шина, на первом и втором входах элемента И 13 присутствуют единичные сисналы. На входе контролируемого дешифратора Н присутствует кодовая комбинация из числа разрешенных, поэтому на выходе элемента ИЛИ 3 присутствует нулевой сигнал, который .инвертируется элементом НЕ 12. Следовательно, на третий вход элемента И 13 с вы- хода элеме нта НЕ 12 поступает единичный сигнал. На всех трех входах элемента И 13 присутствуют единичные сигналы, поэтому на его выходе также появляется единичный сигнал, который через элемент ИЛИ 10 проходит на выход устройства. Этот сигнал сигнализирует об отказе дешифратора, при котором на его выходе отсутствует возбужденная шина. При контроле неполных дешифраторов дополнительные выходы (до полного) используются в качестве контролирующих. Первый тип отказов неполных дешифраторов состоит в том, что на выходе возбуждается шина, попадающая в группу выходов, которая не соответствует входной комбинации. В этом случае в зависимости от того, нулевой или единичный сигнал присутствует в младшем разряде входной комбинации, единичный сигнал появляется на выходе элемента И 8 или, 7. Этот сигнал через элемент ИЛИ 10 проходит на выход устройства, сигнализируя об отказе контролируемого дешифратора 1. Второй тип отказа заключается в том, что при наличии на входе запрещенной кодовой комбинации на выходе возбуждается шина, попадающая в группе выходов соответствующей входной комбинации. Пусть, например комбинация 111 относится к числу запрещенных и эта комбинация появляется на выходе дешифратора И. Рассмотрим отказ дешифратора, когда на входную комбинацию 111 возбуждаются два выхода дешифратора - выход, соответствующий, коду 111, и шина, попадающая в группу выходов, которые соответстсуют входным комбинациям с

/ 1

единицей в младшем разряде. В этом случае элемент И 7 закрыт нулевым сигналом с выхода элемента НЕ 5 а элемент И 8 закрыт нулевым сигналом с выхода элемента ИЛИ 1. Следователь но, элементы И 7. и 8 не зафиксируют отказ дешифратора. Однако единичный сигнал с выхода контролирующей шины, соответствующей входному коду 111, проходит через элемент ИЛИ 3 на входы элементов И t и 6. Так как единич ный сигнал с неправильно возбужденной шины попал в группу выходов, поступающих на вход элемента ИЛИ 2, на его выходе появляется единичный сигнал, поступающий на вход элемента И . На другом его входе присутствует единичный сигнал с выхода элемента ИЛИ. По совпадению этих сигналов на выходе элементаг И появляется единичный сигнал, поступающий через элемент ИЛИ 10 .на выход устройства.

При появлении на выходе контролируемого дешифратора k запрещенной

2А9238

кодовой комбинации с нулем в младшем разряде и отказе, при котором возбуждается нетребуемая шина в группе выходов, соединенных с входами элемента ИЛИ 1, отказ обнаруживается аналогично как и в описанном случае. Только в этом случае единичный сигнал появляется на выходе элемента

И 6.. Этот сигнал также проходит на Овыход устройства через элемент ИЛИ 10, сигнализируя об отказе контролируемого дешифратора .

Таким образом, применение изобреts тения позволяет контролировать не только полные дешифраторы, но и широко используемый на практике класс

неполных дешифраторов. Кроме того, оно позволяет обнаружить такие отказы, когда на выходе дешифратора возбуждается нетребуемая шина в группе выходов, соответствующей входной кодовой комбинации, причем контроль дешифратора осуществляется

25 в процессе его функционирования.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля дешифратора | 1980 |

|

SU918948A1 |

| Устройство для контроля дешифраторов | 1986 |

|

SU1339899A1 |

| Устройство для контроля дешифраторов | 1985 |

|

SU1298924A1 |

| Устройство для контроля дешифратора | 1979 |

|

SU811262A1 |

| Устройство для контроля двоичного счетчика | 1979 |

|

SU864580A1 |

| Счетчик импульсов с контролем ошибок | 1978 |

|

SU841125A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1986 |

|

SU1425698A2 |

| Устройство для контроля дешифратора | 1983 |

|

SU1149267A1 |

| Устройство для контроля -разряд-НОгО СчЕТчиКА | 1979 |

|

SU839060A1 |

| Устройство для контроля программ | 1986 |

|

SU1332323A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ДЕШИФРАТОРА, содержащее первый, второй и третий элементы ИЛИ, первый элемент НЕ, первый и второй элементы И, причем четные и нечетные выходы контролируемого дешифратора соединены с входами первого и второго элементов ИЛИ соответственно, выходы которых соединены с первыми входами первого и второго элементов И соответственно, вход младшего разряда дешифруемого кода дешифратора соединен с -вторым входом первого элемента И и через первый элемент НЕ с вторым входом второго элемента И, выходы первого и второго элементов И соединены соответственно с первым и вторым входами третьего элемента ИЛИ, выход которого является контрольным выходом устройства, отличающееся тем, что, с целью расширения функциональных возможностей путем обнаружения ошибок в группе выходов, соответствующей входной кодовой комбинации, в него введены четвертый и пятый элементы ИЛИ, второй элемент НЕ, элемент ИЛИНЕ, третий, четвертый и пятый элементы И, причем третья группа выходов контролируемого дешифратора соединена с входами четвертого элемента ИЛИ, выход которого соединен с первыми входами третьего и четвертого элементов И и через второй элемент НЕ - с первым входом пятого 9 элемента И, выход первого элемента ИЛИ соединен с первым входом элемента ИЛИ-НЕ и вторым входом четвертого Элемента И, выход которого соединен с третьим входом третьего элемента ИЛИ, выход второго элемента ИЛИ соединен с вторыми входами элемента ИЛИ-НЕ и третьего элемента И, выход которого соединен с четIND вертым входом третьего элемента ИЛИ, 4 входы контролируемого дешифратора СО соединены с входами пятого элеменto та ИЛИ, выход которого соединен с 00 вторым входом пятого элемента И, выход элемента ИЛИ-НЕ соединен с третьим входом пятого элемента И, выход которого соединен с пятым входом третьего элемента ИЛИ.

Г7Г

Гг/

tsj

у Г7

7V I

«A

i i

i i

Csl

to

t

у

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ приготовления серо-угольноселитряного пороха | 1924 |

|

SU2220A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР N° , кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Методы обнаружения ошибок в работе ЭЦВМ | |||

| М., Мир, 1972, с.226-233, фиг.12,7 (прототип) | |||

Авторы

Даты

1983-06-23—Публикация

1982-02-12—Подача