(54) УМНОЖИТЕЛЬ ЧАСТОТЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Измеритель переходных характеристик частотных прецизионных устройств | 1987 |

|

SU1620992A1 |

| Умножитель частоты | 1980 |

|

SU900428A2 |

| Преобразователь активной мощности в цифровой код | 1989 |

|

SU1780033A1 |

| Устройство для измерения среднего индикаторного давления двигателя внутреннего сгорания | 1984 |

|

SU1283559A1 |

| Фазометр | 1991 |

|

SU1817037A1 |

| Преобразователь частоты импульсов в код | 1983 |

|

SU1156259A1 |

| РЕЛЕ ЧАСТОТЫ | 2002 |

|

RU2208865C1 |

| Преобразователь напряжение-код | 1977 |

|

SU945976A1 |

| Преобразователь угла поворота вала в код | 1982 |

|

SU1022202A1 |

| Устройство для сжатия информации | 1987 |

|

SU1529043A1 |

Изобретение относится к импульсной и электроизмерительной технике и может обеспечить, например расширение -пределов измерения фазометров. . Известен умножитель частоты выполненный на основе аналоговой техники и состоящий из следящей системы с использованием на входе преобразователя часгогачнапря:йкение, сигнал с которого поступает на схему сравнения. Сигнал с выхода схемы сравнения поступает на интегратор, а с его выхода на преобразователь напряжение-частота. Этот сиг нал является выходным сигналом усТ1эойства. Одновременно он Ьоступает на вход второго преобразователя чвстоты-41апря- жение, выходной свгнап которого через делитель-регулятор коэ4|финвента умножения частот поступает на второй вход схемы сравнения Г. Недостатком этой устройства является ограниченность динамического диапазона, входного сигнала. , Известен умножитель частоты выпопненный на основе цифровой техники. В течение периода входной частоты производится заполнение первого счетчика импульсами, поступающими -с генератора первой опорной частоты, затем полученный код переносится в устройство запоминания, с выхода которого он поступает на один вход схемы сравнения кодов. На второй вход схемы сравнения кодов поступает код со второго счетчика, заполняемого второй опорной частотой в П раз больше первой. С выхода схемы сравнения в момент равенства кодов в устройстве запоминания и во втором счетчике сигнал поступает на вход установки в нуль второго счетчика. Таким образом во втором -счетчике формируется код за время Т в h раз меньше периода входного сигнала Г2; Недостатком этого устройства являетеся зависимость некоторых параметров его от частоты входного сигнала, что также ведет к ограничению динамическо-

го диапазона входного сигнала вследстви насыщения отдельных уздов устройства.

Наиболее близким по те шической сущ ности к предлагаемому является устройство, состоящее из формирователя узких импульсов, блока опорного напряжения, делителя опорного напряжения, ключа, порогового устройства, генератора пилообразного напряжения, разделительного конденсатора. Формирователь узких импуль- сов соединен последовательно с генератором пилообразного напряжения, разделительным конденсатором, первым входом порогового устройства. Ключ имеет связь с точкой соединения разделительного конденсатора и первого входа порогового устройства. Первый вход управления ключом соединен с выходом формирователя узких импульсов, а второй с выходом порогового устройства. Вход блока опорного напряжения соединен с выходом генератора пилообразного напряжения, а выход его соединен с делителем опорного напряжения, выход которого соединен со вторым входом

порогового устройства .ЗД.

Недостатком данного устройства является то, что с изменением частоты входного сигнала изменяется размах пи- лообразного напряжения, что также ве- дет к ограничению динамического диапазона частоты входного сигнала вследствие насыщения генератора пипообразного напряжения.

,,

Цель изобретения - расширенае динамического .диапазона частоты входного сигнала.

Поставленная цель достигается тем, что в умножитель частоты, содержащий формирователь импульсов, блок опорного напряжения, выход которого соединен со входом делителя опорного напряжения, коммутатор и компаратор, вЬеден блок управления, первый вход которого через формирователь импульсов соединен со входом устройства и входом блока опор ного напряжения, второй вход - с выхо- дом компаратора, а выход через коммутатор - с одним из входсж компаратора второй вход которого соединен с первым выходом блока опорного напряжения, вто рой выход которого через делитель Опор«нрго напряжения подключен ко в орому входу коммутатора.

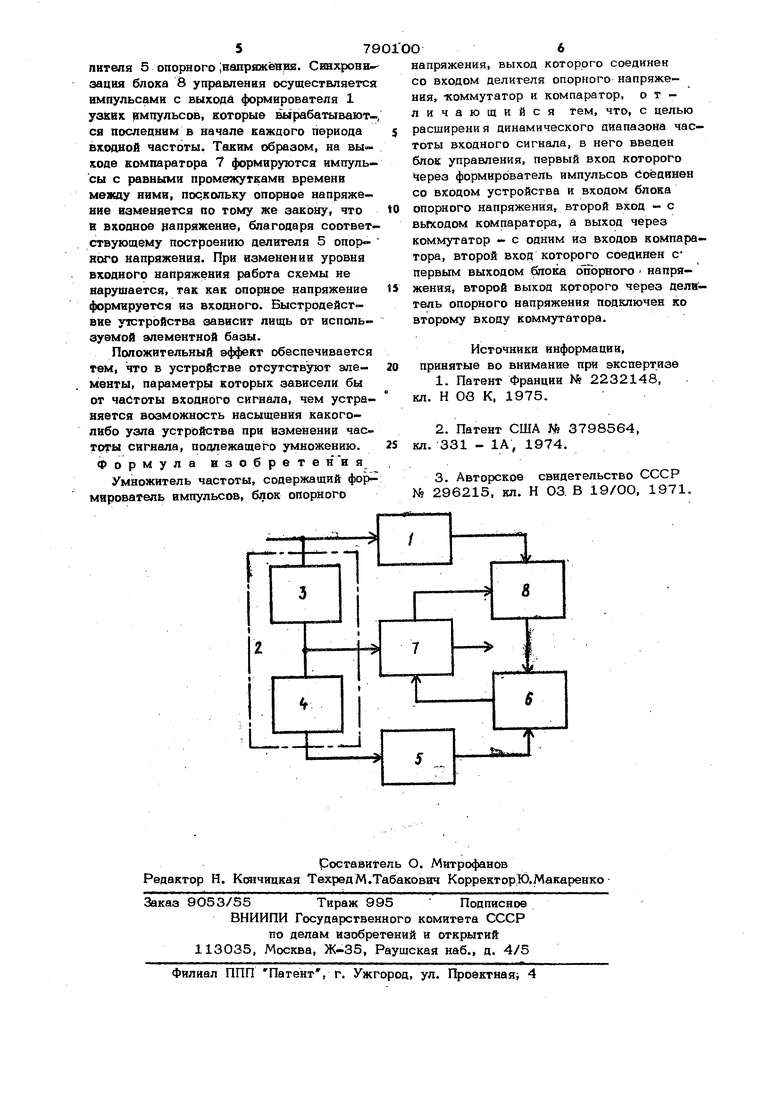

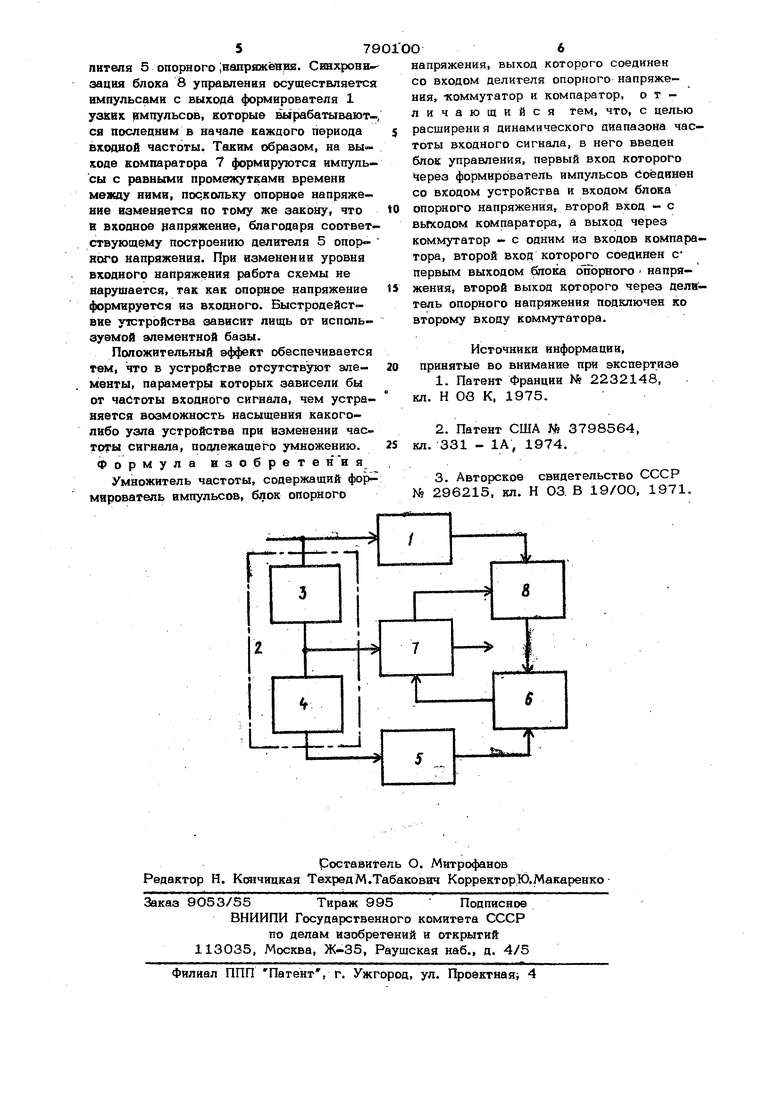

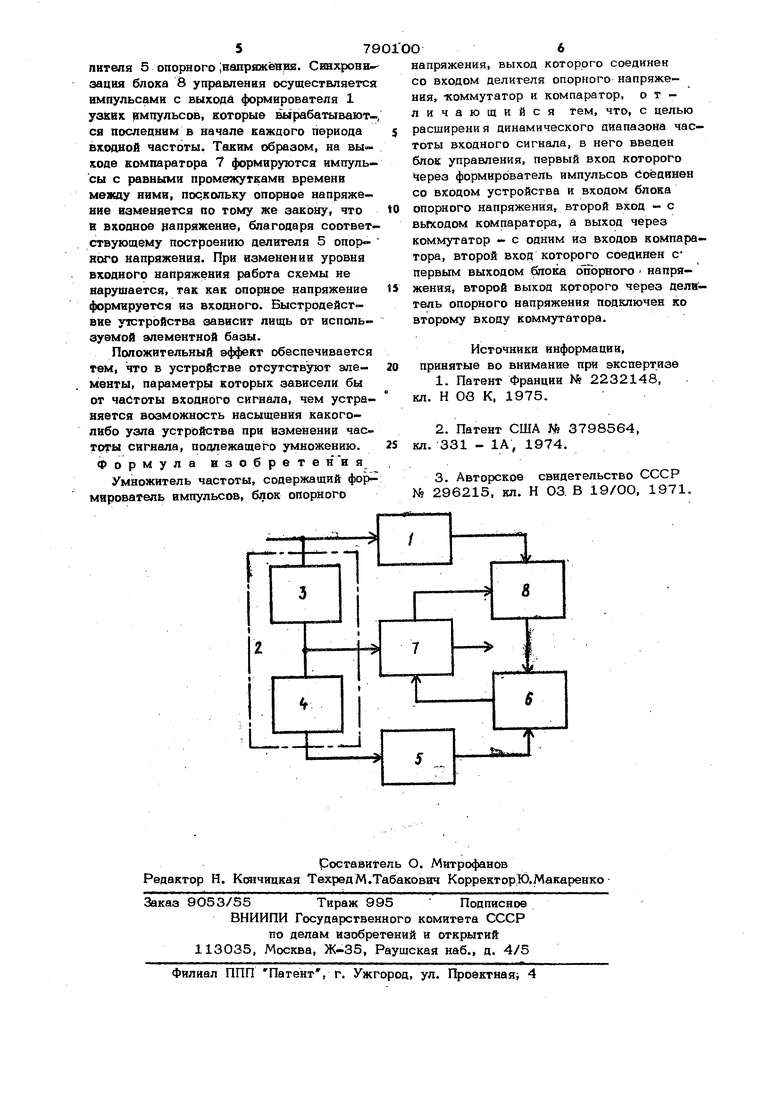

На чертеже представлен схематически умножнтвпь частоты.

Он содержит формирователь i узких импульсов, блок 2 опорного напряжения,

в который входят детектор 3 и фильтр 4 делитель 5 опорного напряжения, коммутатор 6, компаратор 7, блок 8 управления. Вход формирователя 1 узких импульсов соединен с входом блока 2 опорного напряжения, первый выход которого, а именно детектора 3 соединен с фильтром 4. Выхой фильтра 4 соединен последовательно с делителем 5 опорного напряжения, коммутатором 6, первым входом компаратора 7 н входом блока 8 управления. Выход детектора 3 соединен со вторым входом компаратора 7. Вход синхронизации устройства управления 8 соединен с выходом формирователя узких импульсов, а выход с входом управления коммутатора 6.

Работа предлагаемого устройства осу ществляется следующим образом.

.«..

Входной сигнал (например синусоидальный) поступает в блок 2 опорного напряжения, где происходит запоминание его максимального значения. С выхода фильтра 4 блока 2 опорного напряжения поступает постоянное напряжение на вход делителя 5 опорного напряжения. Делитель 5 опорного напряжения состоит из набора последовательно соединенных резисторов, образующих ступени деления опорного напряжения. При ом величины сопротивлений рассчитываются таким образом, чтобы коэффициент деления изменялся при переходе от одной ступени к другой в соответствий с законом изменения сигнала, подлежащего умножению .(например синусоидальному). С выхода каждой ступени деления делителя 5 шорного нап| яжения сигнал поступает на соответствующие входы коммутатора 6, который в зависимости от сигнала, поступающе.го иэ блока 8 управления на его вход управления, подключает к одному входу компаратора 7 сигнал одной из ступеней делителя 5 опорного напряжения. Это напряжение на выходе коммутатора 6 является опорным для компаратора 7, на второй, вход которого поступает пульсирующее напряжение с детектора 3, которое сравнивается с опорным напряжением на лервом вход&. В момент равенству этих {напряжений компаратором 7 вырабатывается импульс поступающий на выход устройства и на вход блока 8 управления, который в зависимости от числа поступивших импульсов вырабатывает сигналы, производящие переключение коммутатора 6 на пропускание Напряжения очередной ступени оепителя 5 опорного ;напряжёнра. Синхрони. зация блока S управления осуохествляется импульсами с выхода формирователя 1 узкнх импульсов, которые вырабатываются последним в начале каждого периода вхооной частоты. Таким образом, на выходе компаратора 7 формируются импульсы с равными промежутками времени между ними, пос.кольку опорное напряжение изменяется по тому же закону, что в входное напряжение, благодаря соответствующему построению делителя 5 опорнего напряжения. При изменении уровня входного напряжения работа схемы не нарушается, так как опорное напряжение формируется из входного. Быстродействие утстройства зависит лищь от используемой элементной базы.

Положительный эффект обеспечивается тем, что в устройстве отсутствуют элементы, параметры которых зависели бы от частоты входного сигнала, чем устраняется возможность насыщения какоголибо узла устройства при изменении частоты сигнала, подлежащего умножению. Формула изобретения

Умножитель частоты, содержащий фор мйрователь импульсов, блок опорного

IE

rpzciin

7LJ

напряжения, выход которого соединен со входом делителя опорного напряжения, -коммутатор и компаратор, отличающийся тем, что, с целью расширени я динамического диапазона частоты входного сигнала, в него введен блок управления, первый вход которого kiepe3 формирователь импульсов Соединен со входом устройства и входом блока опорного напряжения, второй вход - с выходом компаратора, а выход через коммутатор - с одним из входов компаратора, второй вход которого соединен с первым выходом блока опорного напряжения, второй выход которого через делатель опорного напряжения подключен ко второму входу коммутатора.

Источники информации, принятые во внимание при экспертизе

lavb

Авторы

Даты

1980-12-23—Публикация

1978-11-09—Подача