(Л

ел to

со

о .

00

Фм

Изобретение относится к автоматике и вьп1ислительной технике и предназначено для анализа сигналов в реальном масштабе времени, согласования полосы с полосой пропускания анализирующей и измерительной аппаратуры и пр.

Цель изобретения - повышение точ- НОСТ11 устройства за счет уменьшения динамического диапазона входного сигнала преобразователя аналог-код.

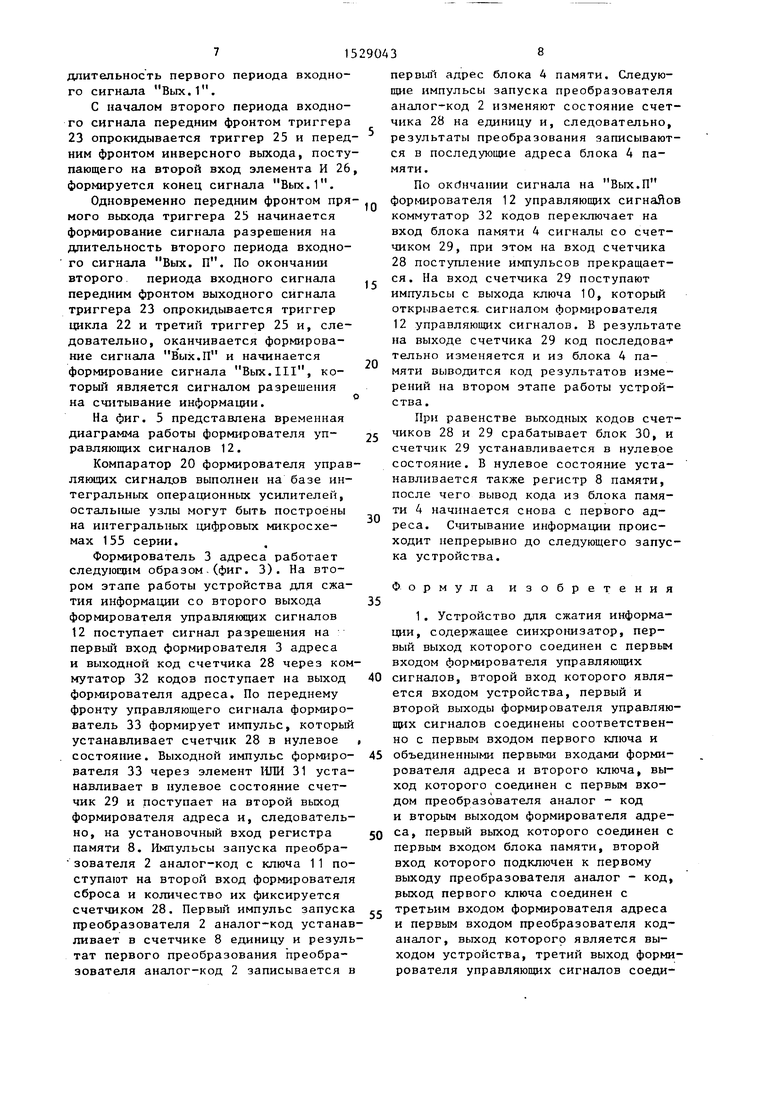

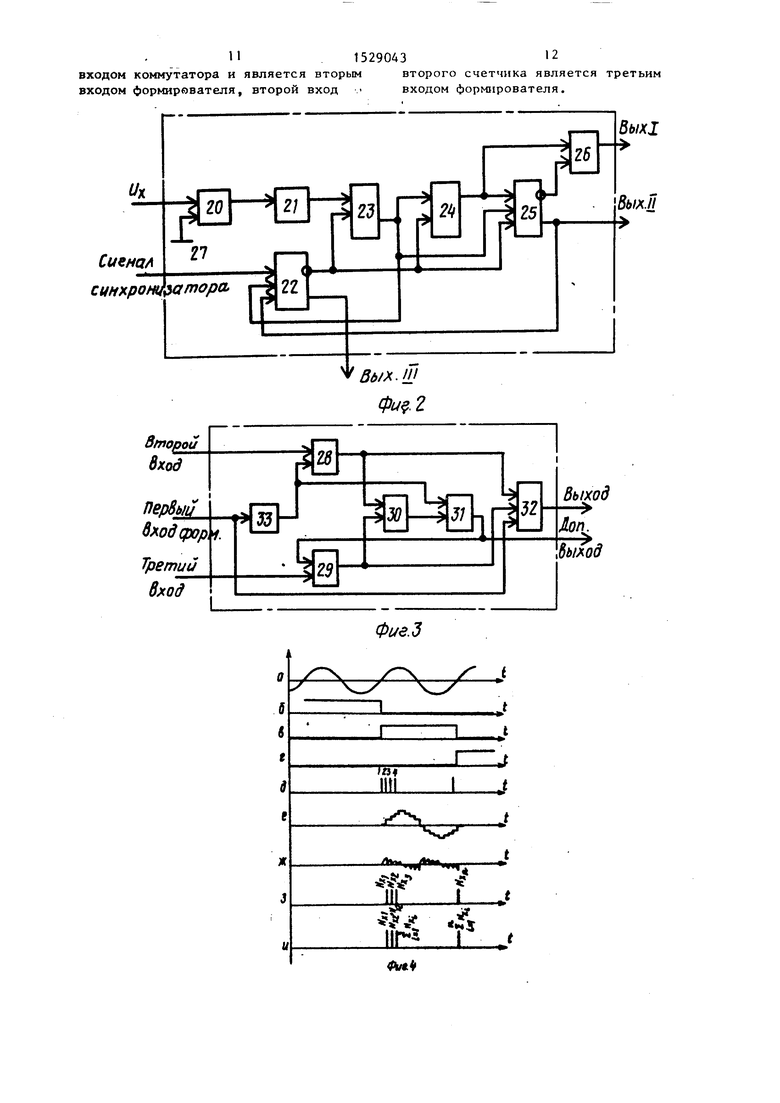

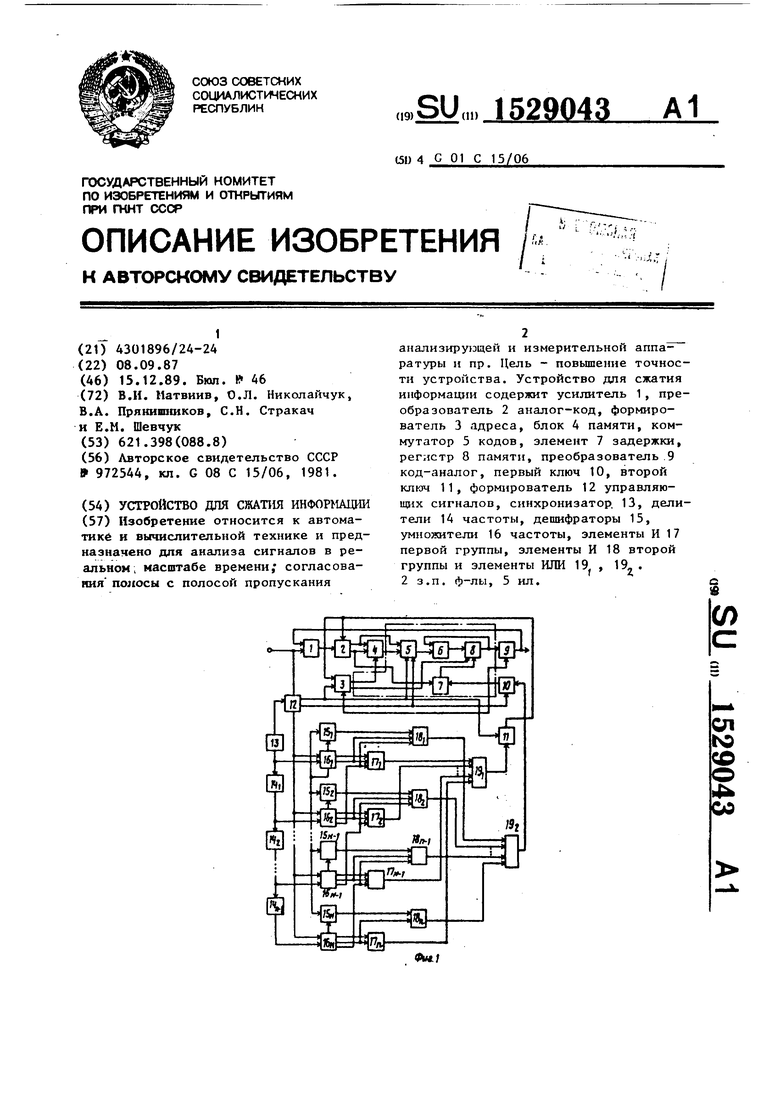

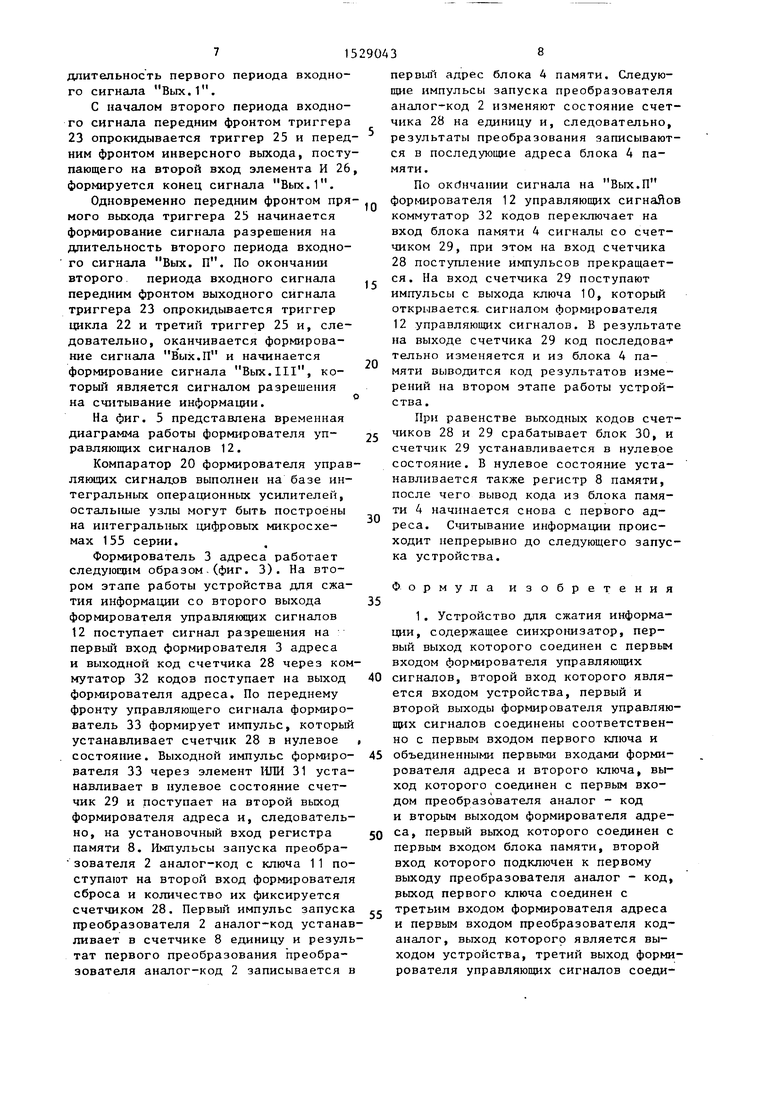

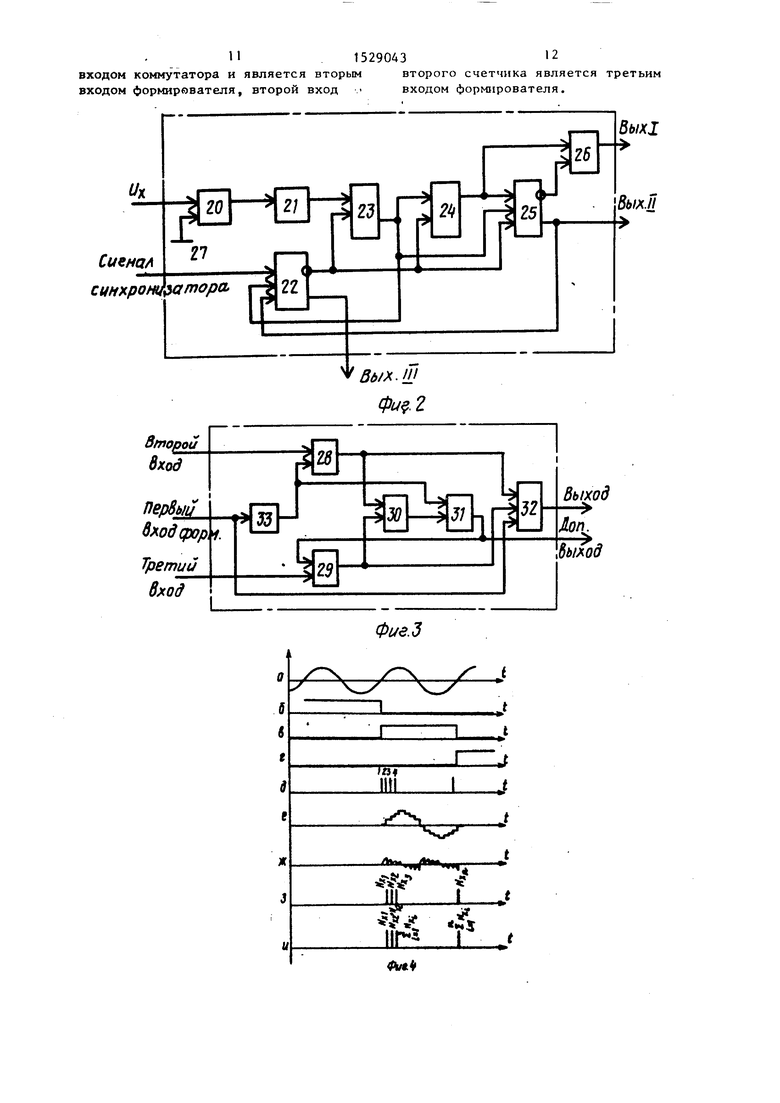

На фиг. 1 представлена функциональная схема устройства сжатия; на фиг. 2 - схема формирователя управ- ляюЕцих сигналовi на фиг. 3 - схема формирователя адреса из фиг. 4 - временные диаграммы, поясняющие работу устройства; на фиг. 5 - временные диаграммы, поясняющие работу формирователя управляющих сигналов.

Устройство дпя сжатия информации (фиг. 1) содержит усилитель 1, преобразователь 2 аналог-код, формирователь 3 адреса, блок 4 памяти, коммутатор 5 кодов, сумматор 6 кодов, элемент 7 задержки, регистр 8 памяти преобразователь 9 код-аналог, первый ключ 10, второй ключ 11, формирователь 12 управляющих сигналов, синхронизатор 13, делители 14,-14, частоты, дещифраторы , умножители 16,-16, частоты, элементы.И первой группы, элементы И 18 -18 второй группы, элементы ИЛИ 19. и 19.

Формирователь управляющих сигнало (фиг. 2) содержит компаратор 20, формирователь 21 импульсов, триггеры 22-25, элемент 26 И шину 27 нулевого потенциала.

Формирователь адреса (фиг. 3) содержит счетчики 28 и 29, блок 30 сравнения кодов, элемент ИЛИ 31, коммутатор 32 кодов, формирователь 33 импульсов сброса.

Устройство работает следующим образом.

Входной периодический сигнал (Ug, фиг. 4а) поступает на усилитель 1 и на формирователь 12 управляющих сигн лов, на выходах которого после запус ка синхронизатором 13 формируются си налы разрешения: на третьем выходе - на длительность первого периода входного сигнала (фиг. 46), на втором выходе - на длительность второго периода (фиг. 4в), на первом выходе - на считывание информации из блока памяти после окончания второго перио

5

0

5

0

5

0

5

0

5

да и до следующего запуска устройства (фиг. 4г).

Таким образом, работа устройства осуществляется в три этапа. На первом этапе (первый период входного сигнала) осуществляется формирование частоты запуска преобразователя 2 аналог-код и частоты считывания информации из блока 4 памяти и такт1Д о- вания преобразователя 9 код-аналог. На первые входы умножителей 16j-16 частоты поступает сигнал разрешения их работы из сетки частот, формируемой каждым умножителем, осуществляется выбор такой частоты, которая обеспечивает деление одного периода на число, равное числу ординат, находящееся в пределах от до 2 .

Дпя обеспечения удобства проведения спектрального анализа с помощью предлагаемого устройства частота запуска преобразователя 2 аналог-код fj и частота запуска преобразователя

9код-аналог J должны соотноситься следующим образом:

fj/f/ , где j 1,2,,,,N Форш1рование указанной сетки частот осуг ествляется с помощью умножителей 16|-16j частоты и (N-1) делителей 14 частоты, причем последние в этом случае имеют коэффициент деления Благодаря этому на входах соседних N умножителей . частоты, идентичные частоты кратны десяти.

Все умножители частоты начинают работать одновременно и выбор частот f-j и f осуществляется следующим образом. I

После первого переполнения счетчика первого умножителя 16 частоты он включает соответствующие элементы И 17 и 18 обеих групп, а так как на вторых входах последних также имеется разрешаюгдай сигнал, то через них и через элементы ИЛИ 19. и 19я на ключи

10и 11 поступают частоты f и f. , После первого переполнения счетчика второго умножителя 16 частоты он вгшючает соответствующие элементы

И 17, ISg обеих групп, а первые элементы И 17у , 18 обеих групп выключает. Через второй элемент И 17 первой группы поступает частота f. , а через второй элемент И 18 второй группы поступает частота f, , причем отношение равно fj /fj 10. Аналогичные изменения происходят после переполнения счетчика j-ro умножителя 16J частоты, причем выполняется соотношение . 10 . Выполнение этого соотношения обеспечивается выполнением отношения fj /fj 10 и тем, что все частоты f/ поступают только из первого умножителя 1б частоты.

Таким образом, в течение первого периода входного сигнала осуществляется выбор частот f/ и f.

На втором этапе работы устройства (второй период входного сигнала) с третьего выхода формирователя 12 управляющих сигналов на умножители 16j-16 частоты поступает запрет их работы, со второго выхода формирователя 12 управляющих сигналов поступает сигнал разрешения на первый вход формирователя 3 адреса, четвертый вход коммутатора 5 кодов и первьп вход второго 11 ключа (фиг. 4б).

При этом на первый вход сумматора 6 через коммутатор 5 кодов подключается выходной код преобразователя 2 аналог-код. С выбранной частотой f осуществляется запуск преобразователя 2 аналог-код и запись полученны выбранных значений входного сигнала в блок А памяти.

В начале первого измерения выходное напряжение преобразователя 9 код аналог равно нулю, а следовательно, на вход преобразователя 2 аналог- код поступает полностью входной сиг нал и, . Код первого преобразования NzU по сигналу Конец преобразования записывается в первый адрес блока 4 памяти и после задержки, ,Сформированной блоком, в регистр 8 пмяти. В результате на выходе преобразователя 9 код-аналог устанавливам

ется выходное напряжение U N т.е. }щ и, (фиг. 4е). При этом на вход преобразователя 2 аналог-код поступает напряжение, равное U. UKI (фиг. 4ж).

Результат второго преобразования аналогично записывается во второй адрес блока памяти 4 и поступает на вход сумматора 6, на вторые входы которого поступает код N из регистра 8 памяти. На выходе сумматоре 6 формируется код, равньи NJ +N2, который по разрешающему сигналу на блоке 7 задержки 2 переписывается в регистр 8 памяти. При этом код пропорционален входному сигналу, N,+N.

т.е.

и

t

5

0

5

0

5

На выходе преобразователя 9 код- аналог устанавливается напряжение U,N,+N или и - и„.

На вход преобразователя 2 аналог- код поступает напряжение, равное

Ux3-UKf

Последующие преобразования происходят аналогично.

По окончании второго периода сигнала в блоке 4 памяти оказываются заполненными от ot до 2 ( выборочных значений. В тот же момент второй ключ 11 закрывается, а первый ключ 10 и коммутатор 5 кодов открывается сигналом разрешения с первого выхода формирователя 12 управляющих сигналов. Начинается третий этап работы устройства - считывание информации из блока 4 памяти и ее преобразование в аналоговую форму в преобразователе 9 код-аналог. С выхода первого 10 ключа частота f. поступает на тактирование фор1 Шрователя 3, преобразователя 9 аналог-код и на вход элемента 7 задержки. Считывание информации происходит непрерывно до следующего запуска устройства. Начало третьего этапа работы означает конец преобразования временного (спектрального) масштаба входного периодического сигнала.

Формирователь 12 управляющих сигналов работает следующим образом (фиг. 2).

Входной периодический сигнал

40 поступает на вход компаратора 20. После прихода сигнала запуска с синхронизатора 13 схема формирователя при помощи триггера 22 приводится в рабочее состояние. При каждом пере45 ходе через нуль периодического входного сигнала компаратор 20 формирует прямоугольные импульсы. Формирователь 21 по каждому фронту формирует импульсы, поступающие на счетный вход триг50 гера 23, Который делит частоту поступающих импульсов на два. Выходные сигналы триггера 23 поступают на счетные входы триггеров 24 и 25. Передним фронтом выходного сигнала триггера 23

55 опрокидывается триггер 24, выход которого соединен с D-входом триггера 25 и первым входом элемента И 26, при этом на выходе элемента И 26 формируется начало сигнала разрешения на

длительность первого периода входного сигнала Вых.1.

С началом второго периода входного сигнала передним фронтом триггера 23 опрокидывается триггер 25 и передним фронтом инверсного выхода, поступающего на второй вход элемента И 26, формируется конец сигнала Вых.1.

15290438

первьш адрес блока 4 памяти. Следующие импульсы запуска преобразователя аналог-код 2 изменяют состояние счетчика 28 на единицу и, следовательно, результаты преобразования записываются в последующие адреса блока 4 памяти.

По окбнчании сигнала на Вых.П

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сжатия информации | 1988 |

|

SU1550558A1 |

| Генератор сигналов сложной формы | 1980 |

|

SU983692A1 |

| Цифровой многофазный преобразователь мощности в частоту | 1989 |

|

SU1707557A1 |

| Устройство для моделирования видеоизображений | 1988 |

|

SU1603421A1 |

| Устройство для временного сжатия входного сигнала | 1982 |

|

SU1100632A1 |

| УСТРОЙСТВО ДЛЯ РЕГУЛИРОВАНИЯ ДАВЛЕНИЯ | 1992 |

|

RU2072548C1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Устройство для считывания графической информации | 1987 |

|

SU1564661A1 |

| Устройство для отображения радиолокационной информации на экране электронно-лучевой трубки | 1989 |

|

SU1691880A1 |

| СПОСОБ РЕГУЛИРОВАНИЯ ЖИДКОСТНОГО РАКЕТНОГО ДВИГАТЕЛЯ И УСТРОЙСТВА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1993 |

|

RU2085755C1 |

Изобретение относится к автоматике и вычислительной технике и предназначено для анализа сигналов в реальном масштабе времени, согласования полосы с полосой пропускания анализирующей и измерительной аппаратуры и пр. Цель - повышение точности устройства. Устройство для сжатия информации содержит усилитель 1, преобразователь 2 аналог-код, формирователь 3 адреса, блок 4 памяти, коммутатор 5 кодов, элемент 7 задержки, регистр 8 памяти, преобразователь 9 код-аналог, первый ключ 10, второй ключ 11, формирователь 12 управляющих сигналов, синхронизатор 13, делители 14 частоты, дешифраторы 15, умножители 16 частоты, элементы И 17 первой группы, элементы И 18 второй группы и элементы ИЛИ 191, 192. 2 з.п. ф-лы, 5 ил.

Одновременно передним фронтом пря-.. формирователя 12 управляющих сигнаЯов

мого выхода триггера 25 начинается формирование сигнала разрешения на длительность второго периода входного сигнала Вых. П. По окончании второго. периода входного сигнала передним фронтом выходного сигнала триггера 23 опрокидывается триггер цикла 22 и третий триггер 25 и, следовательно, оканчивается формирование сигнала Вых.П и начинается формирование сигнала Вых.III, который является сигналом разрешения на считывание информации.

На фиг. 5 представлена временная диаграмма работы формирователя управляющих сигналов 12.

Компаратор 20 формирователя управляющих сигнал,ов выполнен на базе интегральных операционных усилителей, осталыш1е узлы могут быть построены на интегральных цифровых микросхемах 155 серии.

Формирователь 3 адреса работает следующим образом,(фиг. 3). На втором этапе работы устройства для сжатия информации со второго выхода формирователя управляющих сигналов 12 поступает сигнал разрешения на : первьш вход формирователя 3 адреса и выходной код счетчика 28 через коммутатор 32 кодов поступает на выход формирователя адреса. По переднему фронту управляющего сигнала формирователь 33 формирует импульс, который устанавливает счетчик 28 в нулевое , состояние. Выходной импульс формирователя 33 через элемент ПЛИ 31 устанавливает в нулевое состояние счетчик 29 и поступает на второй выход формирователя адреса и, следовательно, на установочный вход регистра памяти 8. Импульсы запуска преобра- зователя 2 аналог-код с ключа 11 поступают на второй вход формирователя сброса и количество их фиксируется счетчиком 28. Первый импульс запуска преобразователя 2 аналог-код устанавливает в счетчике 8 единицу и результат первого преобразования преобразователя аналог-код 2 записывается в

15

20

25

30

35

40

45

50

55

коммутатор 32 кодов переключает на вход блока памяти 4 сигналы со счетчиком 29, при этом на вход счетчика 28 поступление импульсов прекращается. На вход счетчика 29 поступают импульсы с выхода ключа 10, который открывается, сигналом формирователя 12 управляющих сигналов. В результате на выходе счетчика 29 код последова- тельно изменяется и из блока 4 памяти выводится код результатов измерений на втором этапе работы устройства.

При равенстве выходных кодов счетчиков 28 и 29 срабатывает блок 30, и счетчик 29 устанавливается в нулевое состояние. В нулевое состояние устанавливается также регистр 8 памяти, после чего вывод кода из блока памяти 4 начинается снова с первого адреса. Считывание информации происходит непрерывно до следующего запуска устройства.

Формула изобретения

5

0

5

0

5

0

5

0

5

коммутатор 32 кодов переключает на вход блока памяти 4 сигналы со счетчиком 29, при этом на вход счетчика 28 поступление импульсов прекращается. На вход счетчика 29 поступают импульсы с выхода ключа 10, который открывается, сигналом формирователя 12 управляющих сигналов. В результате на выходе счетчика 29 код последова- тельно изменяется и из блока 4 памяти выводится код результатов измерений на втором этапе работы устройства.

При равенстве выходных кодов счетчиков 28 и 29 срабатывает блок 30, и счетчик 29 устанавливается в нулевое состояние. В нулевое состояние устанавливается также регистр 8 памяти, после чего вывод кода из блока памяти 4 начинается снова с первого адреса. Считывание информации происходит непрерывно до следующего запуска устройства.

Формула изобретения

ра соединен с входом первого делителя частоты и вторым входом первого умножителя частоты, выход каждого делителя частоты соединен с входом следующего делителя частоты и вторым входом второго и последующих умножителей частоты.

и компараторе, выход которого через

r формирователь импульсов соединен с первым входом первого триггера, выход которого соединен с первыми входами второго, третьего и четвертого триггеров, выход второго триггера

0 Соединен с первым входом элемента И и вторым входом третьего триггера, инверсный выход которого соединен с вторым входом элемента И, выход которого является первым выходом формиро5 вателя, прямой выход третьего триггера соединен с вторым входом четвертого триггера и является вторым выходом формирователя, инверсньй выход четвертого триггера соединен с вторыми входами первого и второго триггеров и третьим входом третьего триггера, третий вход и прямой выход четвертого триггера являются соответственно первым входом и третьим выходом формирователя, первый и второй

5 входы компаратора соответственно подключен к шине нулевого потенциала и является вторым входом формирователя .

5 первыми входаг-ш элемента ИЛИ и первого счетчика, выход которого соединен с первыми входами блока сравнения и коммутатора, выход которого является первым выходом формирователя, вы0 ход блока сравнения соединен с вторым входом элемента ИЛИ, выход элемента ИЛИ является вторым выходом формирователя и соединен с первым входом второго счетчика, выход которого сое-,

5 динен с вторыми входами коммутатора и блока сравнения, второй вход пер- эого счетчика является первым входом формирователя, вход формирователя импульсов сброса объединен с третьим

0

11152904312

входом коммутатора и является вторым второго счетчика является третьим входом формирователя, второй вход входом формирователя.

п

л

Редактор Н.Горват

Составитель Н.Бочарова

Техред Л.Олийнык Корректор Н.Король

Заказ 7839/35

Тираж 683

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. А/3

зс

п

п

фие.5

Подписное

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1989-12-15—Публикация

1987-09-08—Подача