1

Многодиапазонное c4eTHO-aHaji6f6вое реле времени относится .к электрическим системам автоматического управления, в частности к времяз 1дающим устройствам, предназначено для создания временных выдержек и задержек входного сигнала и может быть .... наиболее эффективно использовано при создании систем управления различным технологическим оборудованием в саjMbix разнообразных областях промышленности, таких как термическое, химическое, сборное, сварочное и т.д. при разработке отдельных станков, агрегатов и целых линий.

Известны аналоговые реле времени, построенные на принципе формирования выдержки времени за счет заряда и разряда конденсатора через резистор или стабилизатор тока с быстрым восстановлением первоначального значения напряжения на конденсаторе по окончании цикла работы {).

При формировании коротких временных интервалов (десятки секунд) аналоговые реле времени работают доста точно удовлетворительно в части получения необходимых точностей и повторяемости выдержек времени (нестабиль.ность 0,5-1%). При этом необходигад

применять стабильные по температуре и времени конденсаторы, резисторы и пороговые элементы (элементы сравнения), а также принимать специальные меры для стабилизации питающего напряжения.

Применение аналоговых реле времени для получения больших временных интервалов (минуты, часы) с необхоfO ДИМОЙ нестабильностью (0,5-1%) приводит к появлению больших технических трудностей, преодоление которых влечет за собой значите.г1ьное повышение стоимости и увеличение габаритов,

«5 что делает разработку .и применение аналоговых реле времени нецелесообразным. Применение а аналоговом реле времени вместо специальных высокостабильных конденсаторов малогабаритных и обладающих большой емкостью электролитических конденсаторов приводит к резкому повышению нестабиль ности указанных реле, что делает их малопригодными для формирования

25 больших выдержек времени.

Увеличение емкости .конденсаторов приводит также к увеличению минимальных уставок времени за счет остаточного заряда на обкладках конденсатора при больших значениях емкое- ти. С увеличением верхней границыf вьщержки времени одновременно возраст,ает и нижняя граница, т.е. минимал ьйые выдержки времени, что не позволяет расширить диапазон выдержек времени путем изменения сопротивления цепи заряда конденсатора. Применяемые в настоящее время счет.ные реле времени на широкий диапазон времен являются сложнь ми и дорогими устройствами, требующими сложного задатчика времени и не позволяющие производить уставку времени на. любое требуемое значение, так как все счетные реле времени имеют дискретные уставки.

.Цель изобретения - увеличение выдержки времени и стабильности при аналоговом задании времени, а также расширение области применения.

Для достижения указанной цели устройство, содержащее аналоговое : реле времени, подключенное к задатчику времени, содержит счетную часть, включающую в себя п делителей частоты, и управляющую часть, содержащую первый инвертор, вход которого подключен к клемме внешнего сигнала запуска, вйход через первый элемент ИЛИ связан со входом аналогового реле времени, выход которого через второй- элемент ИЛИ и второй инвертор связан со входом первого из П последовательно соединенных делителей частоты, .вход КЯждого из которых и выход последнего подключены к контактам переключателя диапазонов, а выход второго элемента ИЛИ подключен ко входу узла задержки, вход и,выход которого подключены к различным входам первого элемента И, выход которого подключен ко вторым входам обоих элементов ИЛИ, а третий вход первого элемента И связан с общим контактом переключателя диапазонов и первым входом второго элемента И, выход первого инвертора связан со вторым : входом второго элемента И, а источник внешнего сигнала запуска связан со входом сброса каждого из п делителей частоты.

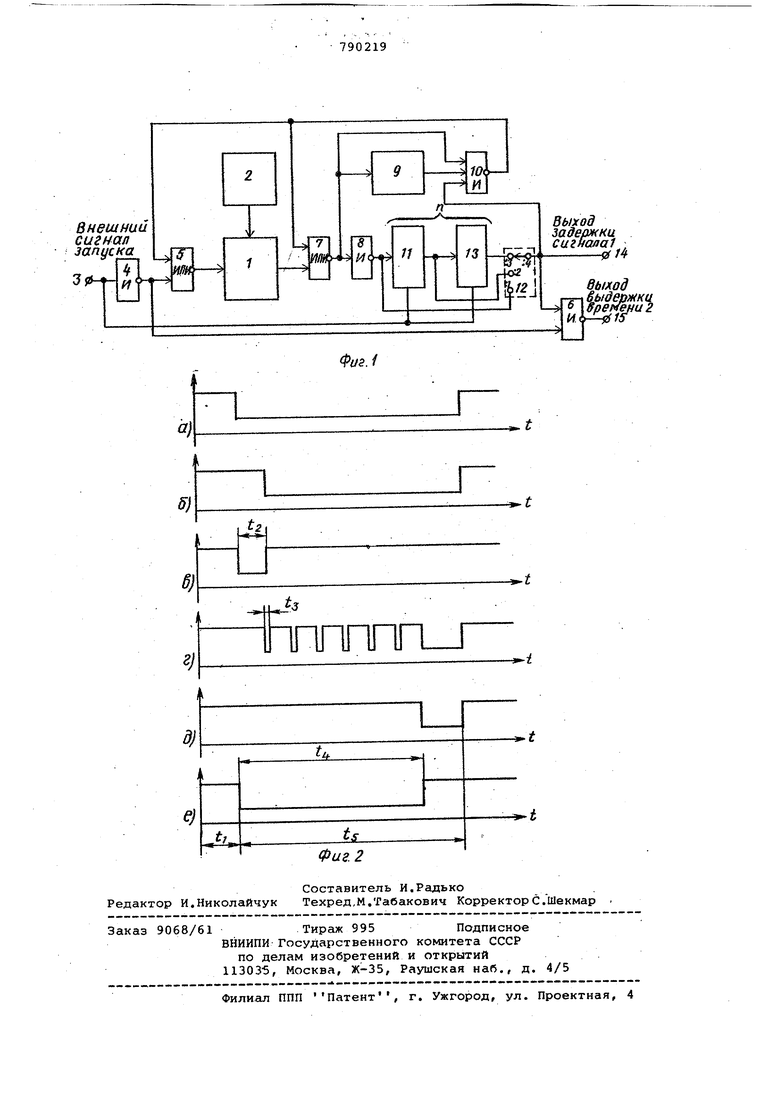

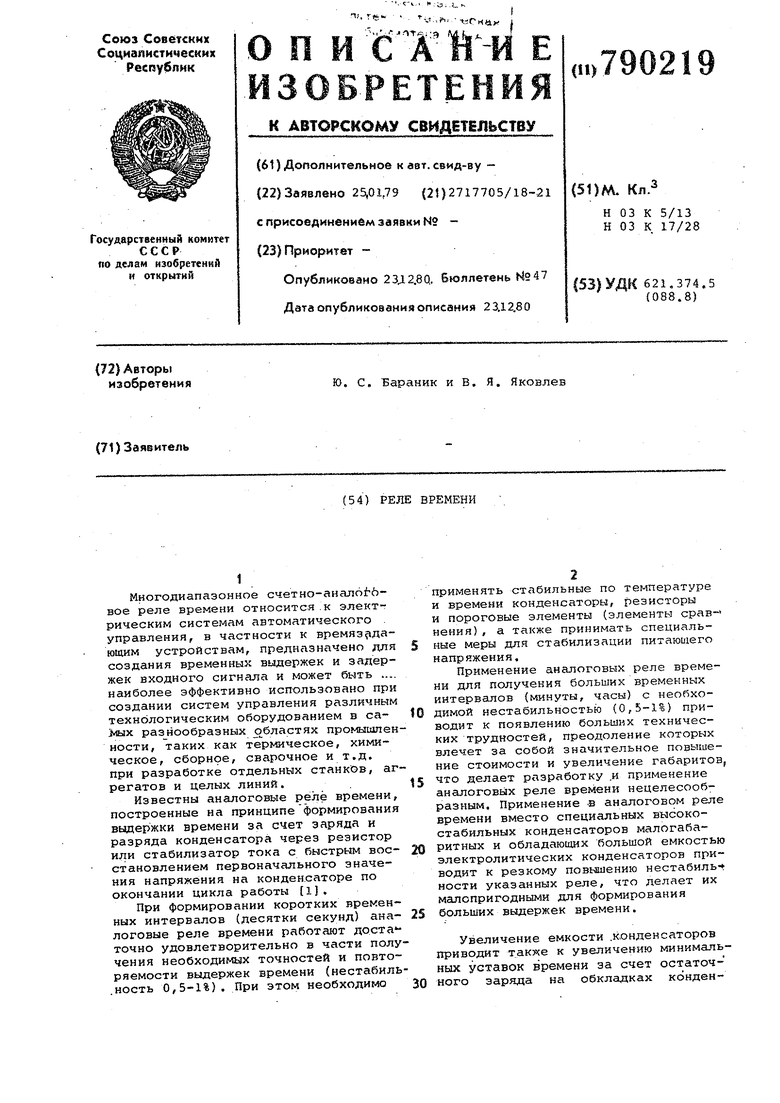

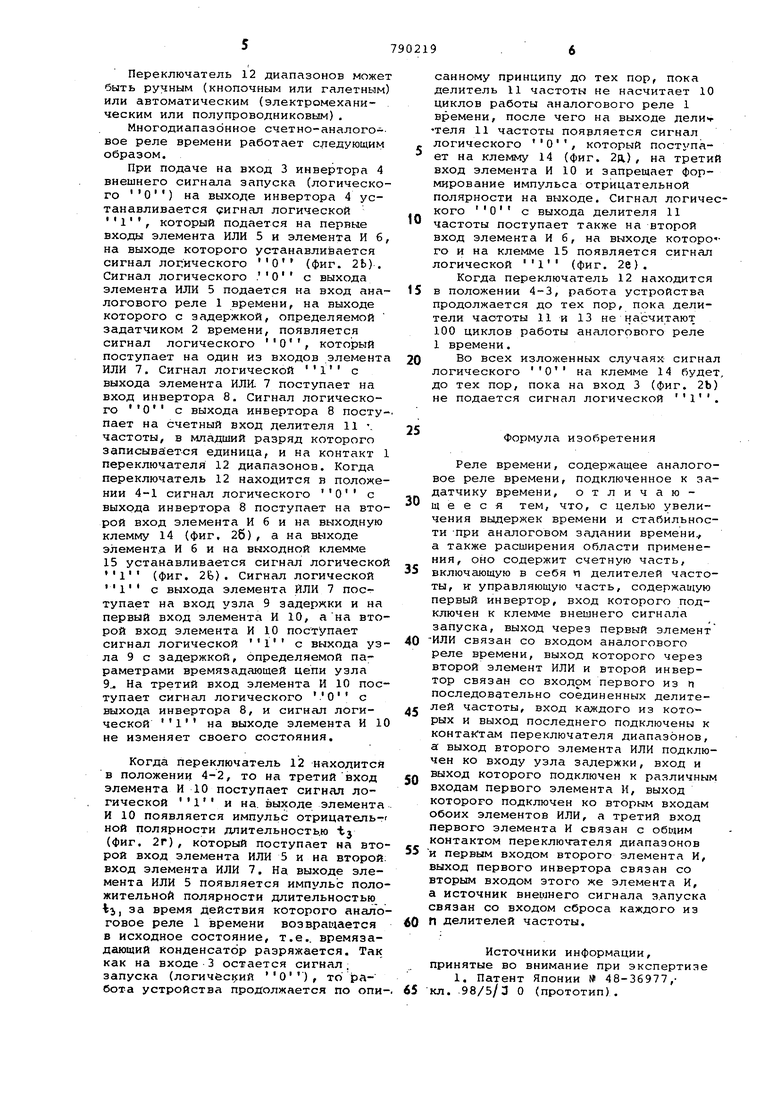

На фиг. 1 представлена структур-ная схема многодиапазонного счетноаналогового реле времени; на фиг. 2временные диаграммы, поясняющие его работу.

Реле времени содержит аналоговое реле 1 времени, управляемое от задатчика 2 времени Внешний сигнал запуска подается на вход 3 инвертора 4, выход которого связан со входом логического элемента ИЛИ 5 и входом логического элемента И 6, а выход логического элемента ИЛИ 5 связан со входом аналогового реле 1 времени.

Выход аналогового реле I времени связан со входом логического элемента ИЛИ 7, выход которого соединен со

входом инвертора 8, входом узла 9 задержки и первым входом логического элемента И 10. Выход узла 9 задержки связан со вторым входом логичес кого элемент.а И 10, выход которого подключен ко второму входу логического элемента ИЛИ 5 и ко второму входу логического элемента ИЛИ 7. Выход инвертора 8 связан со входом первого делителя 11 частоты и переключателя 12 диапазонов.. Выход делителя 11 частоты связан со входом / следующего из п. делителей частрты и соответствующим контактом переключателя 12 диапазонов. (На Фиг. 1 изображены два делителя частоты 11 и 13 и переключатель 12 диапазонов на три положения) . Общий контакт 4 переключателя диапазонов .подключен ко второму входу логического элемента И 6, третьему входу логического элемента И 10 и выходной клемме 14, которая является выходом сигнала задержки. Выход логического элемента И 6 подключен к at годной клемме 15, которая является выходом сигнала задержки времени. Клемма 3 внешнего сигнала запуска связана со входом сброса каждого из п делителей частоты (на фиг. 1 делители частоты 11 и 13) .

Анёшоговое реле 1 времени может алть выполнено по любой известной схеме, и, в частности, может быть реализовано на принципе заряда или разряда емкости конденсатора. Единственным ограничением к выбору схемы аналогового реле 1 времени является следующее условие - при подаче на вход реле внешнего сигнала запуска на выходе реле времени с задержкой, определяемой времязадающей цепью, устанавливается выходной сигнал, который удерживается только при наличи внешнего сигнала запуска и пропадает одновременно со снятием последнего.

Логические элементы ИЛИ 5 и 7, логические элементы И 6 и 10 и инверторы 4 и 8 представляют собой обычные логические схемы, выполненные на полупроводниковых приборах или интегральных схемах.

Узел 9 задержки может быть выполнен на базе линии задержки, интегрирующей RC, -цепи или с использованием любой другой схемы, обеспечивающей задержку переднего фронта входного сигнала на сравнительно незначительное время.

Делители 11 и 13 частоты представляют собой обычную .пересчетную схему, выполненную на полупроводниковых приборах или интегральных схемах. Коэффициент деления делителей 11 и 13 частоты может быть любым, однако для удобства работы коэффициент деления предпочтительно брать равным 10.

Переключатель 12 диапазонов может быть ручным (кнопочным или галетным) или автоматическим (электромеханическим или полупроводниковым).

Многодиапазонное счетно-аналого-вое реле времени работает следующим образом.

При подаче на вход 3 инвертора 4 внешнего сигнала запуска (логического О) на выходе инвертора 4 устанавливается сигнал логической , который подается на первы:е входы элемента ИЛИ 5 и элемента И б, на выходе которого устанавливается сигнал логического О (фиг. 2Ь) . Сигнал логического .О с выхода элемента ИЛИ 5 подается на вход аналогового реле 1 времени, на выходе которого с задержкой, определяемой задатчиком 2 времени, появляется сигнал логического О , который поступает на один из входов элемента ИЛИ 7. Сигнал логической i с выхода элемента ИЛИ. 7 поступает на вход инвертора 8. Сигнал логического с выхода инвертора 8 поступает на счетный вход делителя И . частоты, в младший разряд которого записывается единица, и на контакт 1 переключателя 12 диапазонов. Когда переключатель 12 находится в положении 4-1 сигнал логического О с выхода инвертора 8 поступает на второй вход элемента И б и на выходную клемму 14 (фиг, 2б), а на выходе элемент.а И 6 и на выходной клемме 15 устанавливается сигнал логической (фиг. 2&). Сигнал логической с выхода элемента ИЛИ 7 поступает на вход узла 9 задержки и на первый вход элемента И 10, второй вход элемента И 10 поступает сигнал логической i с выхода узла 9 с задержкой, определяемой параметрами времязадающей цепи узла 9 На третий вход элемента И 10 поступает сигнал логического .О с выхода инвертора 8, и сигнал логической на выходе элемента И 10 не изменяет своего состояния.

Когда переключатель 12 находится в положении 4-2, то на третийвход элемента И 10 поступает сигнал логической и на. выходе элемента И 10 появляется импульс отрицательной полярности длительность.ю tj (фиг. 2г), который поступает на второй вход элемента ИЛИ 5 и на второй вход элемента ИЛИ 7. На. выходе элемента ИЛИ 5 появляется импульс положительной полярности длительностью %j, за время действия которого аналоговое реле 1 времени возвращается в исходное состояние, т.е.. времязадающий конденсатор разряжается. Так как на входе 3 остается сигнал, запуска (логичёс1 ий О), торабота устройства продолжается по опи

санному принципу до тех пор, пока делитель 11 частоты не насчитает 10 циклов работы аналогового реле 1 времени, после чего на выходе делич«теля 11 частоты появляется сигнал логического О , который поступает на клемму 14 (фиг. 2я) , на третий вход элемента И 10 и запрещает формирование импульса отрицательной полярности на выходе. Сигнал логического О с выхода делителя 11 частоты поступает также на второй вход элемента И б, на выходе которо го и на клемме 15 появляется сигнал

(фиг. 2е).

логической

Когда переключатель 12 находится в положении 4-3, работа устройства продолжается до тех пор, пока делители частоты 11 и 13 не насчитают 100 циклов работы аналогового реле 1 времени.

Во всех изложенных случаях сигнал логического О на клемме 14 будет, до тех пор, пока на вход 3 (фиг. 2Ь) не подается сигнал логической .

25

Формула изобретения

Реле времени, содержащее аналоговое реле времени, подключенное к задатчику времени, отличающ е е с я тем, что, с целью увеличения выдержек времени и стабильности -при аналоговом задании времени а также расширения области применения, оно содержит счетную часть,

включающую в себя п делителей частоты, к управляющую часть, содержащую первый инвертор, вход которого подключен к клемме внешнего сигнала запуска, выход через первый элемент

ИЛИ связан со входом аналогового реле времени, выход которого через второй элемент ИЛИ и второй инвертор связан со входом первого из м последовательно соединенных делителей частоты, вход из которых и выход последнего подключены к контактам переключателя диапазонов, а выход второго элемента ИЛИ подключен ко входу узла задержки, вход и выход которого подключен к различным входам первого элемента И, выход которого подключен ко вторым входам обоих элементов ИЛИ, а третий вход первого элемента И связан с общим контактом переключателя диапазонов

и первым входом второго элемента И,

выход первого инвертора связан со вторым входом этого же элемента И, а источник внешнего сигнала з.апуска связан со входом сброса каждого из П делителей частоты.

Источники информации, принятые во внимание при экспертизе

1. Патент Японии № 48-36977,кл. .98/5/3 О (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления дуговой сваркой | 1987 |

|

SU1505705A1 |

| Реле времени | 1991 |

|

SU1800609A1 |

| Устройство для управления поперечной резкой ленты стекла | 1985 |

|

SU1296522A1 |

| СИГНАЛИЗАТОР ЗАГРУЗКИ ДВИГАТЕЛЯ | 1992 |

|

RU2027979C1 |

| РЕЛЕ ВРЕМЕНИ | 2002 |

|

RU2208259C1 |

| Устройство управления паровоздушным молотом | 1983 |

|

SU1131584A1 |

| Многоканальный регулятор | 1982 |

|

SU1100606A1 |

| Преобразователь аналоговых сигналов во временной интервал | 1980 |

|

SU949812A1 |

| Устройство контроля сопротивления изоляции | 1988 |

|

SU1597770A1 |

| Устройство контроля пламени | 1985 |

|

SU1285273A1 |

Авторы

Даты

1980-12-23—Публикация

1979-01-25—Подача