I

Изобретение относится к области радиотехНИКИ и может быть использовано при построении систем передачи изображений со сжатием данных.

Известно устройство, предназначенное для сжатия полосы частот видеосигнала, содержащее блок временных задержек, преобразователь по Адмару, блок кодирования элементов трансформанты, блок код1фования выходного сшнала ,

Од}1ако известное устройство не обладает высокой точностью преобразования сигнала, т.е. в результате сжатия полосы частот видеосигнала получается неодинаковое качество переданных участков изображений, содержащих слабоконтрасткые детали, и участков изобрах ения, содержащих сильноконтрастные детали.

Цель изобретения - увеличение точности преобразования видеосигнала, в результате чего повышается качество переданного изображения.

Для этого в устройство сжатия полосы частот видеосигнала, содержащее блок временных задержек и блок кодирования элементов трансформанты, первый, второй, третий и четвертый выходы которого соединены с первым, вторым, третьим и четвертым входалш блока кощфования выходного а1гнапа соответственно, введега. четыре сумматора, пять блоков вычитания, три блока вычисления абсолютных значений сигнала, три пороговых блока и элемент ИЛИ. При этом первый выход блока временных задержек соединен с первым входом первого сумматора и первым входом первого блока вычитания, второй выход блока временных задержек соединен с вторым входом первого сумматора, с вторым входом первого блока вычитания и с первым входом третьего блока вьгоггания, третш выход блока временных задержек соединен с первыми входами второго сумматора и второго блока вычитагшя, вторым входом третьего блока вычитания, четвертый выход блока временных задержек соединен с вторым входом второго сумматора и вторым входом второго блока вычитания. Причем выходы первого, второго и третьего блоков вычитания через соответствующие блоки вычисления абсолютных значений шгнала соединены с входами первого, второго и третьего пороговых блоков соответственно, а выходы пороговых блоков соединены с первым, вторым и третьим входом элемента ИЛИ. Выход первого сумматора соединен с первым входом третьего сумматора и первым входом четвертого блока вычитания, а выход второго сумматора соединен с вторым входом третьего сумматора и вторым входом четвертого блока вычитания. Выход первого блока вычитания соединен с первым входом четвертого сумматора и первым входом пятого блока вычитания. Выход второго блока вычитания соединен с вторым входом четвертого сумматора и вторым входом пятого блока вычитания, причем выход третьего сумматора соединен с первым входом блока кодирования элементов трансформанты, к второму входу которого подключен выход четвертого сумматора. Выходы четвертого и пятого блоков вычитания подключены к третьему и четвертому входам блока кодирования элементов трансформанты соответственно, а выход элемента ИЛИ соединен с пятым входом блока кодирования элементов трансформанты и пятым входом блока кодирования выходного сигнала.

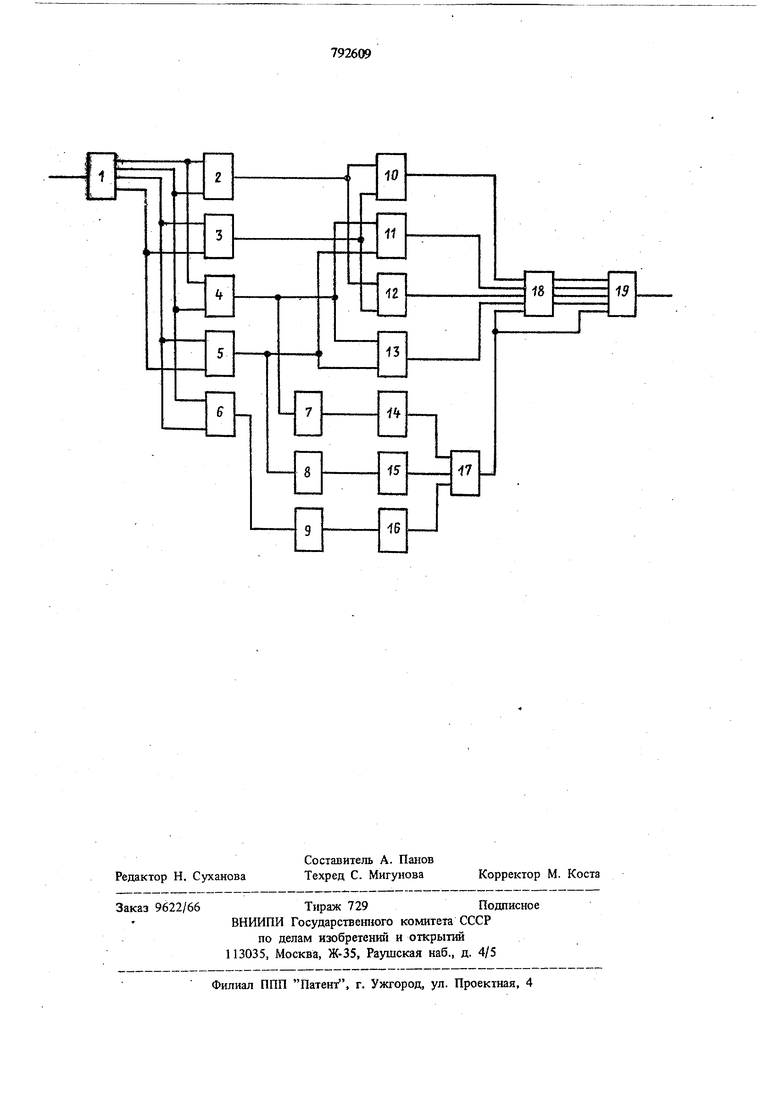

На чертеже изображена структурная электрическая схема устройства сжатия полосы частот видеосигнала.

Устройство содержит блок 1 временных задержек, первый сумматор 2, второй сумматор 3, первый блок 4 вычитания, второй блок 5 вычитания, третий блок 6 вычитания, три блока 7-9 вычисления абсолютных значений сигнала, третий сумматор 10, четвертый сумматор 11, четвертый блок 12 вычитания, пятый блок 13 вычитания, три nqporoвых блока 14-16, элемент ИЛИ 17, блок 18 кодирования элементов трансформанты и блок 19 кодирования выходного сигнала. Принцип работы устройства заключается в следутощем,

На вход блока 1 временных задержек поступает ввдеосигнал в цифровом виде (дискретизированный и квантованный). Б блоке 1 временных задержек осуществляется преобразование четырех последовательно поступающих на вход отсчетов видеошгнала в параллельный четырехточечный сигнал, поступающий на входы сумматоров 2 и 3 и входы блоков 4-6 вычитания. Сумматоры 2, 3, 10, 11 и блоки 4, 5, 12 и 13 вычитания осуществляют преобразование четьфех отсчетов сигнала, поступающего с выходов блока I временных задержек, в соответствии с алгоритмом Адамара. На выходах сумматоров 10, 11 и выходах блоков 12, 13 вычитания образуются при этом значения, так называемых, элементов трансформанты. Так, если обозначить значения сигналов на

выходах блока 1 временных задержек через зо, 81, 82, Зз, на выходах сумматоров 10 и 11 - через bo, bi, на выходах блоков 12, 13 вычитания - через bj, Ьз, то а- и Ь. (i 0,1,2,3) будут связаны следующими соотношениями:

bo Эо +31 + 3j +63,

bi 80 - 81 + а2 - аз, Ьа Эо + 3i - 32 - Зз,

Ьз Эо - 3 - 32 t 8з.

Кроме того, сигналы с выходов блоков 4 и 5 вычитания, участвующих в преобразовании, а также с выхода блока 6 подаются на входы блоков 7-9 вычисления абсолютных значений сигнала, в каждом из которых

Q осуществляется определение абсолютного значения величины числа, поступающего на вход. С выходов блоков 7-9 вьиисления абсолютных значений сигнала величины (ao-ai), (а2-аз), (ai-a2) поступают на входы порого5 вых блоков 14-16. В каждом из блоков 14-16 осуществляется сравнение величины поступившего числа (модуля разности) с величиной порога (несколько градаций) и в случае превышения числом порога на выQ ходе формируется сигнал О. В случае непревыщения числом порога на выходе формируется сигнал 1. На выходе логического элемента ИЛИ 17 формируется сигнал I, если хотя бы на один из его трех входов поступает сигнал 1. В соответствии со значением сигнала на выходе логического элемента ИЛИ 17 в блоке 18 кодирования элементов трансформанты осуществляется кодирование элементов трансформаиты одним из двух возможных способов, но с использованием в каждом случае одного и того же числа двоичных единиц.

Первый вариант кодирования обеспечивает минимизацию искажений, являющихся результатом код1фования при больших отличиях в значениях отсчетов в пределах четырех отсчетов за счет повышенной точности передачи старщих разрядов элементов трансформанты. Второй вариант кодирования обеспечивает минимизацию искажений при небольших отличиях в значениях отсчетов в пределах четырех отсчетов за счет повышенной точности передачи младших разрядов элементов трансформанты.

Таким образом, введение в устройство сжа тия полосы частот видеосигнала ряда блоков. совместно обеспечивающих одновременное преобразование по Адамару и формирование сигнала, управляющего параметрами блока кодирования элементов трансформанты, позволяет увеличить точиость преобразования видеосигнала и, тем самым, повысить качество переданного изображения, выражающееся в обеспечении одинакового высокого качества переданных участков изображения, содержащих слабоконтрастные детали, и участков изобра: женин, содержащих сильноконтрастные детали при сохранении степени сжатия полисы частот видеосигнала. Формула изобретения Устройство сжатия полосы частот видеосигнала, содержащее блок временных задержек и блок кодирования элементов трансформанты первый, второй, третий и четвертый выходы которого соединены с первым, вторым, третьи и четвертым входами блока кодирования выходного сигнала соответственно, отличающееся тем, что, с целью увеличения точности преобразования видеосигнала, в него введены четыре сумматора, пять блоков вычитания, три блока вычисления абсолютных значений сигнала, три пороговых блока и элемент ИЛИ, при этом первый выход блока временных задержек соединен с первым входом первого сумматора и первым входом пер вого блока вычитания, второй выход блока временных задержек соедшсен с вторым входом первого сумматора, Q вторым входом блока вычитания и с первым входом TpctbOpo блока вычитания, третий выход блока временных задержек соединен с первыми входами второго сумматора и второго блока вычитания, вторым входом третьего блока 96 вычитания, четвертый выход блока временных задержек соединен с вторым входом второго сумматора и вторым входом второго блока вычитания, причем выходы первого, второго и третьего блоков вычитания через соответствующие блоки вычисления абсолютных значений сигнала соединены с входами первого, второго и третьего пороговых блоков соответственно, а выходы пороговых блоков соединены с первым, вторым и третьим входом элемента ИЛИ, выход первого сумматора соединен с первым входом третьего сумматора и первым входом четвертого блока вычитания, выход вторЬго сумматора соед1шен с вторым входом третьего сумматора и вторым входом четвертого блока вычитания, выход первого блока вычитания соединен с первым входом четвертого сумматора и первым входом пятого блока вычитания, выход второго блока вычитания соединен с вторым входом четвертого сумматора и вторым входом пятого блока вычитания, причем выход третьего сумматора соединен с первым входом блока кодирования элементов трансформанты, к второму входу которого подключен выход четвертого сумматора, выходы четвертого и пятого блоков вычитания подключены к третьему и четвертому входам блока кодирования элементов трансформанты соответственно, а выход элемента ИЛИ соединен с пятым входом блока кодирования элементов трансформанты и пятым входом блока кодирования выходного сигнала. Источники информации, принятые во внимание при экспертизе 1. Патент США № 3984626, кл. 178-6, опублик. 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Кодер видеосигнала | 1987 |

|

SU1506554A1 |

| Устройство сжатия полосы частот видеосигнала | 1986 |

|

SU1394466A1 |

| Кодер видеосигнала | 1989 |

|

SU1667256A2 |

| Устройство фильтрации импульсных помех на изображении | 1983 |

|

SU1133692A1 |

| Устройство приема телевизионного сигнала с дифференциальной импульсно-кодовой модуляцией | 1987 |

|

SU1434563A1 |

| СПОСОБ ПРЕОБРАЗОВАНИЯ СИГНАЛА ТЕЛЕВИЗИОННОГО ИЗОБРАЖЕНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2010 |

|

RU2454822C2 |

| СПОСОБ ПРЕОБРАЗОВАНИЯ ЦИФРОВОГО СИГНАЛА ИЗОБРАЖЕНИЯ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2004 |

|

RU2287909C2 |

| Устройство для обработки интерферограмм | 1984 |

|

SU1218501A1 |

| Цифровая телевизионная система | 1982 |

|

SU1085015A1 |

| ЦИФРОВАЯ СИСТЕМА ТЕЛЕВИДЕНИЯ ВЫСОКОЙ ЧЕТКОСТИ | 2000 |

|

RU2194370C2 |

Авторы

Даты

1980-12-30—Публикация

1979-03-21—Подача